# A Review on Quantum Computing: Qubits, Cryogenic Electronics and Cryogenic MOSFET Physics

(Invited Paper)

Farzan Jazaeri<sup>a</sup>, Arnout Beckers<sup>a</sup>, Armin Tajalli<sup>b</sup>, and Jean-Michel Sallese<sup>a</sup>

a) Ecole Polytechnique Fédérale de Lausanne (EPFL), Switzerland.

b) Electrical and Computer Engineering Department, University of Utah, USA. E-mail: farzan.jazaeri@epfl.ch, arnout.beckers@epfl.ch

Abstract—Quantum computing (QC) has already entered the industrial landscape and several multinational corporations have initiated their own research efforts. So far, many of these efforts have been focusing on superconducting qubits, whose industrial progress is currently way ahead of all other qubit implementations. This paper briefly reviews the progress made on the silicon-based QC platform, which is highly promising to meet the scale-up challenges by leveraging the semiconductor industry. We look at different types of qubits, the advantages of silicon, and techniques for qubit manipulation in the solid state. Finally, we discuss the possibility of co-integrating silicon qubits with FET-based, cooled front-end electronics, and review the device physics of MOSFETs at deep cryogenic temperatures.

## Keywords: Quantum computing, qubits, cryogenic electronics, cryo-CMOS, MOSFET.

#### I. INTRODUCTION

Quantum computing is attracting more and more the interest of industrial actors, not only broad-interest corporations like Google [1] or Microsoft [2], but also companies more traditionally linked to the area of nanoelectronics and nanotechnology (e.g., IBM [3], Intel [4], and Lockheed Martin [5]).

The field of quantum computing started in the early 1980s. The need for quantum computers (QCs) to simulate quantum physics efficiently, was first foreseen by Richard Feynman [6]. His focus at that time was primarily on the application of QCs to simulate physics, notably quantum mechanics, by exploiting the intrinsic parallelism present in quantum systems. In 1985, David Deutsch proposed to model a universal quantum computer in his seminal paper, "Quantum theory, the Church-Turing principle and the universal quantum computer" [7]. The years following this publication saw several developments in quantum algorithms and quantum-computing theory, particularly by Simon and Vazirani. Interest in the QC field increased exponentially after Peter Shor discovered his factoring algorithm and Lov Grover his search algorithm [8]-[11]. Consequently, the breadth of applications of QCs expanded from Richard Feynman's initial proposal of quantum chemistry/physics, to other potential applications that speak to a wider audience: information security, optimization, machine learning, etc. Later on, in 1999, the world's first quantum computer was made out of superconductors by a Canadian company called D-Wave Systems [12], [13]. A 28qubit quantum computer was demonstrated in 2007, followed by 128 qubits in 2010, 512 qubits in 2013, and 2000 qubits in 2018. However, there is still a heavy debate going on about the actual 'quantumness' of the D-wave computers [14], [15]. The approach followed by D-Wave Systems can be viewed as similar to early computers in the sense that their quantum computer is non-universal, meaning that it can only perform very specific tasks [14]. That is why some people are convinced that a 'universal' quantum computer is yet to be realized. Very recently, IBM proclaimed their company goal to build commercially available, universal quantum computing systems. Their first IBM-Q systems and services are now delivered via the cloud. In addition to Lockheed Martin and IBM, other companies such as Google, Intel, and Microsoft have joined the race for a universal quantum computer. They all have launched recently major research efforts on quantum computing, funding laboratories all over the world known for their early developments in QC. Besides private companies, the European Commission has recently announced the billiondollar Quantum Technologies Flagship [16]. Smaller European projects are ongoing as well, e.g., the MOS-Quito Project (MOS-based Quantum Information Technology) [17], which was set up after the birth of the CMOS compatible qubit in France [18]. Many other physical realizations of quantum bits (qubits) have been proposed and investigated at the level of basic research laboratories. Solid-state implementations have gained increasing attention in recent years owing to their potential for scaling to larger numbers of qubits. Solid-state qubits appear to be the overwhelming choice for industrial and commercial R&D efforts. To the group of solid-state qubits belong superconducting Josephson junctions [19] and spin qubits in silicon [20], [21]. The compatibility of silicon qubits with CMOS foundries is a great asset. To increase the number of qubits in commercial quantum computers, the number of interconnections to the measurements equipment at room temperature will become intractable very soon. Each qubit needs to be individually addressed, requiring a single connection to the outside world. This lowers the degree to which the sub-Kelvin environment of the qubits can be isolated. Thermal noise seeping into the fridge is nefast for the quantum computations. The qubits reside at the bottom of the dilution refrigerator. The interconnections pass from the  $\approx 10$ -mK environment to the 4.2-K stage of the dilution fridge all the way to outside. Since thermal noise can never be completely avoided, the current view is that quantum error correction is necessary, introducing even more qubits for redundancy. Several redundant physical qubits have to be used to encode one logical qubit. Furthermore, the wiring capacitances accumulate when the system scales, which increases the latency. This poses problems to running more sophisticated quantum algorithms that require immediate action after a qubit is read [22]. To face these scale-up challenges, the use of CMOS front-end electronics that can operate at deep cryogenic temperatures (< 10 K) has been proposed by many research groups all over the world [23]-[29]. Recently, a CMOS prototype IC with a pulse generator to talk to qubits has been deployed in the 4-K stage of the Google Bristlecone quantum computer [30]. By sharing the same CMOS technology, qubits and peripheral electronics could lie even on the same chip. To fully profit from the most established industrial technology, the ultimate goal would be to realize so-called 'quantum-integrated circuits' or QICs. Many challenges remain to accomplish this, ranging from qubits to MOSFET models to system architectures.

In this review, we discuss when (not) to use quantum computers, the physics of qubits, basic quantum logic gates, different physical realizations of qubits, and the development of peripheral low-temperature electronics for an efficient interface between qubits and external (room-temperature) circuitry. Finally, we explain the MOSFET physics at deep cryogenic temperatures that furthers our understanding for model verification and validation for deep cryogenic IC design.

## II. WHEN (NOT) TO USE QUANTUM COMPUTERS

Quantum computers will only give a speed-up over conventional computers for specific problems, typically 'very hard' problems. The quantum computer works by executing the same quantum algorithm several times over again. The most likely result after these runs is the solution. The time it takes to run the quantum computer several times can still be exponentially faster to arrive at the result of a very hard problem than a conventional computer would need in a single run working on the same problem. Many problems are characterized by this 'very hard' exponential growth in complexity. These problems are intractable today on supercomputing clusters in a reasonable amount of time. We can thus benefit from quantum computers in optimization problems, machine learning, sampling of large data sets, forecasting etc. Another example is quantum chemistry (e.g., simulating proteins for new medicine) that is currently running at the limit of classical computers. To actually simulate what is going on in a simple molecule, every electron-electron interaction needs to be taken into account. Next, Shor's algorithm is the most famous example of a computation problem that requires a quantum computer to solve. To factorize a number of N into its prime numbers, a classical computer would take, in some cases, more than the age of the universe to produce a result. It is, therefore, used as a basic encryption tool in information security all over the world. A quantum computer could solve this problem much faster. Lastly, chip manufacturers tend to go to great lengths to suppress quantum effects. It seems only natural to attempt to harness these quantum effects for the benefit of computing.

#### III. QUBITS AND QUANTUM LOGIC GATES

# A. The Qubit

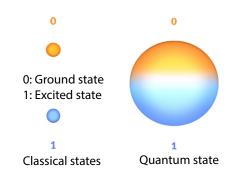

The qubit (or quantum bit) is the basic container of information in a QC, replacing the bit in a conventional computer. The qubit can be in both ground and excited states at the same time (see Fig. 1). The two logical states of each qubit must be mapped onto the eigenstates of some suitable physical system. The most straightforward example is the spin. A spin qubit relies on a spin degree of freedom of either electronic or nuclear nature, which can hold a bit of quantum information for very long times. Note that there are many other examples of qubits: two different polarizations of a photon, two energy states of an electron orbiting a single atom, etc. The quantum computer is fundamentally different than a classical computer due to two distinct properties of qubits. The first property is 'quantum superposition' or the linear combination of possible configurations. The second one is 'quantum entanglement'.

#### B. Quantum Superposition

Consider a system with two basis states, call them  $|0\rangle$  and  $|1\rangle$ . A classical bit of data can be represented by a single atom that is in one of the two states denoted by  $|0\rangle$  and  $|1\rangle$  (left of Fig. 1). By contrast, a quantum state of a qubit is in a continuous state between "0" and "1" until the qubit is measured. The outcome can only be "0" or "1". Therefore, a qubit is a continuous object and its quantum state is given by  $|\psi\rangle = \alpha_1|0\rangle + \alpha_2|1\rangle$ , where  $\alpha_1$  and  $\alpha_2$  are complex amplitudes. If we measure this in the computational basis, we obtain the  $|0\rangle$  state with probability  $|\alpha_1|^2$  or the  $|1\rangle$  state with probability  $|\alpha_2|^2$ , where  $|\alpha_1|^2 + |\alpha_2|^2 = 1$ . If one qubit can be in the superposition of two classical states, two qubits can be in a superposition of four, and *n* qubits can be in a superposition of n qubits is given by  $|\psi\rangle = \alpha_0|0\rangle + \alpha_1|1\rangle + ... + \alpha_{2^n-1}|2^n - 1\rangle$ ,

Fig. 1. The basic unit of information in a QC is the quantum bit (qubit) which can be in any linear combination of ground and excited sates.

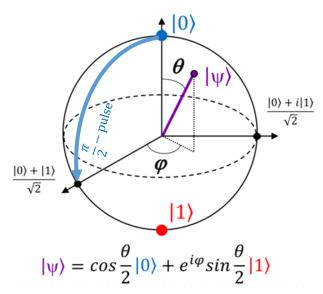

Fig. 2. The Bloch sphere provides a useful means of visualizing the state of a single qubit and operations on it. Any point on this sphere represents a linear combination of the 0 and 1 states with complex coefficients. A  $\pi/2$ -pulse 'rotates' a qubit from the 0-state to a superposition state.

where  $\sum_{j=0}^{2^n-1} |\alpha_j|^2 = 1$ . Figure 2 shows the Bloch sphere. The Bloch sphere provides a useful means of visualizing the state of a single qubit and often serves as an excellent testbed for ideas about quantum computation and quantum information [31]. The angles  $\theta$  and  $\varphi$  can be interpreted as the polar and azimuth angles of points on the sphere, respectively. There are an infinite number of these points on the unit sphere. It is worth emphasizing that we cannot "see" a superposition itself, but only classical states. It is not determined in advance what the outcome of the measurement will be. The only thing we can say before the measurement is that we will observe state  $|j\rangle$  with probability  $|\alpha_j|^2$ .

## C. Quantum Entanglement

The second property that distinguishes QCs from conventional computers is entanglement. If two qubits are 'entangled' there is a correlation between these two qubits. If one qubit is in one particular state, the other one *has to be* in another particular state. If two electrons become entangled, their spin states are correlated such that if one of the electrons has a spin-up, then the other one has a spin-down after measurement. This property was pointed by Albert Einstein in 1935 [32]. The creation and manipulation of entangled states plays a central role in quantum information processing.

## D. How to Interact with a Qubit?

For example, an electron in an atom can be in either the ground state or any excited state. By shining light on the atom, with appropriate energy and for an appropriate length of time, it is possible to move the electron from the ground to excited state or vice versa. More interestingly, by reducing the time we shine the light, an electron initially in the state  $|0\rangle$  can be moved halfway between  $|0\rangle$  and  $|1\rangle$ .

Similarly to the previous example, the qubits in a quantum computer are first initialized, say all spin-up (zero state on the Bloch sphere in Fig. 2) by applying a large, static magnetic field of around one Tesla. An electromagnetic pulse is then applied to each qubit individually to bring the qubit into any possible state on the Bloch sphere. The actual qubit state depends on the pulse amplitude and time. For instance, a superposition state can be created when using a so-called  $\pi/2$ pulse, which 'rotates' the qubit from the top of the Bloch sphere to the equator, as shown in Fig. 2. The timing of a  $\pi/2$ -pulse is given by  $t = \pi/(2\omega)$ , where  $\omega$  is the angular frequency of the electromagnetic driving field [33]. Similarly, a  $\pi$ -pulse would flip the qubit from the zero to the one state in Fig. 2. For silicon qubits,  $\omega$  is typically in the order of hundreds of MHz to tens of GHz. These type of pulses can be created by oscillators integrated in advanced CMOS technologies, as discussed in Sec. V. The superposed qubits then still need to be coupled (entangled). The quantum information is in the fragile entanglements. After time evolution, the quantum states are read-out and the quantum algorithm is repeated.

To sum up this subsection, there are two main things we can do with a qubit: (i) we can measure it as 0 or 1 with a certain probability, or, (ii) we can apply some operation to it, which corresponds to rotating the quantum state to a different position on the Bloch sphere. Rotations on the Bloch sphere are implemented in a quantum computer by so-called 'quantum logic gates' which are discussed next.

#### E. Quantum Logic Gates

To build a universal quantum computer, a set of universal quantum logic gates is required, similar to the ones present in classical computers [7]. A unitary operator that acts on a small number of qubits is often called a 'gate', in analogy to classical logic gates like AND, OR, and NOT. In what follows, we discuss three of the most important quantum logic gates.

1) NOT Gate: We start with a simple quantum NOT gate, also called bitflip gate, or X. The output of this gate is  $c_1|0\rangle + c_0|1\rangle$  when the input is  $c_0|0\rangle + c_1|1\rangle$ . In matrix form, this is

$$X = \begin{pmatrix} 0 & 1\\ 1 & 0 \end{pmatrix} \tag{1}$$

2) Controlled-NOT Gate: An example of a two-qubit gate is the controlled-not gate or CNOT. It negates the second bit of its input if the first bit is  $|1\rangle$ , and does nothing if the first bit is 0. Therefore, CNOT is a quantum gate which is different than NOT and the output depends on the first input. The first qubit is called the control qubit, the second the target qubit. In matrix form, this can be expressed as:

$$CNOT = \frac{1}{\sqrt{2}} \begin{pmatrix} 1 & 0 & 0 & 0\\ 0 & 1 & 0 & 0\\ 0 & 0 & 0 & 1\\ 0 & 0 & 1 & 0 \end{pmatrix}$$

(2)

3) Hadamard Gate: Another important quantum gate is the Hadamard gate which is used to create the quantum superposition ( $\pi/2$ -pulse), specified by  $H|0\rangle = \frac{1}{\sqrt{2}}|0\rangle + \frac{1}{\sqrt{2}}|1\rangle$ when starting from the zero state. The Hadamard gate outputs  $|0\rangle$  or  $|1\rangle$  with equal probability. As a unitary matrix, this is

$$H = \frac{1}{\sqrt{2}} \quad \begin{pmatrix} 1 & 1\\ 1 & -1 \end{pmatrix} \tag{3}$$

There are other quantum gates in use, such as the phaseflip, phaseshift, and Toffoli gate among others. For a more detailed treatment of quantum gates, see e.g., Chuang and Nielsen [31].

#### **IV. QUBIT IMPLEMENTATIONS**

The qubits in a quantum computer should meet the following five traditional requirements called the DiVincenzo criteria, after the theoretical physicist David P. DiVincenzo [34]:

- 1) A scalable physical system,

- 2) Ability to initialize the state of the qubits,

- 3) Coherence time longer than the gate operation time,

- 4) A universal set of quantum gates,

- 5) A qubit-specific measurement capability.

Over the years, researchers have come up with several physical realizations of qubits that each fulfill these criteria to a certain extent. Liquid-state nuclear-magnetic-resonance (NMR) [35] and ion traps [36] were amongst the earliest studied. Superconducting and semiconductor qubits are becoming more relevant for scalability. Each qubit type has its own advantages and industrial players have placed bets on their favorites.

## A. Nuclear Magnetic Resonance Qubits

Nuclear Magnetic Resonance (NMR) provides a way to build QCs by using the spin of atomic nuclei [37]. Shor's factoring algorithm has been realized using this technique by Vandersypen and Chuang [38]. NMR systems have fairly long relaxation times, and thus decoherence is not a major problem. Even though NMR largely satisfies the DiVincenzo criteria reaching a high degree of qubit control and permitting hundreds of operations in sequence, there is a quite strong limitation on the size that NMR quantum computers can attain.

#### B. Ion Traps

Ion traps offer great possibilities for building quantum computers [36]. Ion trap quantum computing operates on a qubit register formed by a linear string of ions confined in a high electromagnetic field. Ions are excellent quantum memories and long coherence times have been demonstrated [36], [39]. In addition, scaling the number of qubits in an ion trap quantum processor is in principle feasible [40].

## C. Superconducting Qubits

Scientists have built artificial atoms made out of superconducting devices [19], e.g., a Josephson junction, coupled to a microwave resonator for control and read-out [3]. This is the road chosen by e.g., Google and IBM. A normal LC circuit made from non-superconducting metals is not a good qubit because the energy spacing of the quantum harmonic oscillator is the same over the energy scale ( $E = \hbar \omega_o$ , where  $\omega_o = \sqrt{LC}$  is the resonance frequency). The Josephson inductance introduces a nonlinearity which increases the energy spacing such that the ground state and first excited state of the oscillator become separate from the other excited states. This allows to selectively excite a two-state system and thus use it as a qubit.

## D. Nitrogen Vacancies in Diamond

Nitrogen vacancies (NV centers) in diamond have the advantage over other qubits in that they are easily coupled to photons. This can be exploited to accomplish efficient quantum networks [41]. It is not unlikely that different types of qubits will complement each other in different systems and applications. However, NV centers are defects in a diamond crystal which are harder to control during fabrication than spin qubits in silicon, including the CMOS compatible qubits.

### E. Silicon Qubits and CMOS Compatible Qubits

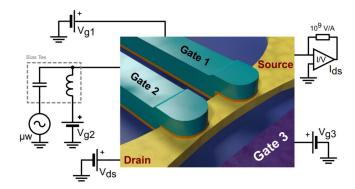

Semiconductor qubits were initially developed in III-V materials, typically GaAs [42]. However, a variety of spin qubits in silicon have now been demonstrated in academic research laboratories that have longer spin coherence times, up to several milliseconds [43]. This is mainly thanks to the possibility of isotopically purifying silicon from excess nuclear spins. Nuclear spins in the host material can decohere the quantum state of a qubit. In silicon, two routes for spin qubit fabrication are available: qubits that rely on (i) the spins of electrons in electrostatically defined quantum dots (QDs), and (ii) the spins of electrons or nuclei of impurity atoms implanted in the silicon host. Apart from its outstanding properties as a host material for qubits, silicon has the advantage that the processes to make these quantum devices are largely in place today, requiring relatively few modifications to existing silicon fabs. Silicon is also the best understood material in terms of defects by years of industrial experience. The University of New South Wales in Sydney proposed the first qubits in silicon [21]. A few years later, CEA-Léti in France proposed the first CMOS compatible qubit in a fully-depleted SOI technology [18], [44]. Others are following the initiative to use silicon. For instance, the Hughes Research Laboratory in the United States has recently opened a research line on siliconbased quantum computing. Furthermore, the nanoelectronics expertise center IMEC in Belgium is collaborating with several partners, including CEA-Léti, to scale up the fabrication of quantum devices in its state-of-the-art cleanrooms [45]. As shown in Fig. 3, the main idea of a CMOS compatible qubit is to use a MOS gate to electrostatically confine electrons in a corner quantum dot [46]. Only one half of a gate is required for one dot. A single electron can be trapped in the corner by repelling electric fields imposed from all sides. Normally, we would interact with a spin qubit by drawing a metal line close to the qubit and pushing an oscillating current through the wire which would produce an oscillating magnetic field that can interact with the electron spin. However, the use of a metallic wire for each qubit is not very scalable. It is possible to remove the wire and use only a MOS gate to control the

Fig. 3. Schematic of a double quantum dot system. From Corna et al. [48].

spins. This technique is known in literature as Electric Dipole Spin Resonance (EDSR). However, using only a MOS gate, we do not have an oscillating magnetic field and the electric field on the gate interacts only with the position of the electron, not directly with its spin. A requirement to achieve coupling to the electron's spin is that a material with a strong spinorbit coupling is used. To achieve a high spin-orbit coupling in silicon, the focus has recently shifted from electron spin qubits to hole spin qubits [47].

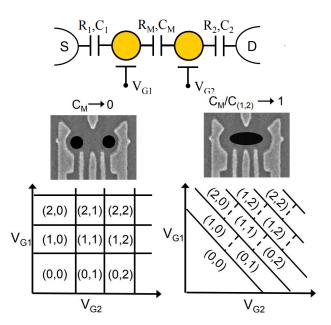

Let's first have a look at the double quantum dot system as shown on the top of Fig. 4. Double dots are useful in QC experiments because one dot can be used for manipulation and the other for measurement, or both can be used to investigate entanglement. It consists of two electrodes known as the drain and the source, we have two quantum dots between the source and drain contacts. The electrical potential of the quantum dots can be tuned by electrodes, known as the gates, which are capacitively coupled to the islands. In double quantum dots, electrons can be transferred from one quantum dot to the other by modifying the electrostatic potential landscape using gate voltages. Depending on the coupling capacitance between the quantum dots, we have to different situations. On the left side of Fig. 4, no coupling exists between the two quantum dots. Different rectangular regions in stability diagrams correspond to different numbers of electrons. On the right side of Fig. 4, when the two quantum dots are coupled, the rectangular regions are symmetric along the line for  $V_{G1} = V_{G2}$ .

During the transport through a dot, the number of electrons in the dot is varied one by one which is a single electron tunneling. This means that the N electron ground state can only be constructed by adding (subtracting) one electron to (from) N-1 (N+1) electron ground state. In such quantum system, a blocking state might occur due to the coulomb blockade and therefore no accessible energy levels are within tunneling range of an electron on the source contact. Variations in the charge of quantum dots due to the tunneling transitions cause a small shift in the resonance frequency which can be detected in the amplitude and phase of the reflected signal in RF reflectometry technique RF reflectometry technique with resonant frequency of few hundred MHz is used to control

Fig. 4. Network of tunnel resistors and capacitors representing two quantum dots coupled in series (top). Charge stability diagrams for (left) uncoupled and (right) coupled double dots, depicting the equilibrium electron numbers (N1,N2) in dot 1 and 2 respectively. Adapted from [49]

and measure qubits if we are not dealing with the spin state of the electrons.

For a given dot structure, a charge stability diagram, or a "honeycomb diagram", can be formed, telling us at which gate voltages what electron occupancy is favored. To construct this diagram, we first model our double or triple dot as a system of capacitors (see Fig. 4). In a perfectly uncoupled double dot, we would expect a pattern of rectangles to be formed in our stability plot. In a perfectly coupled system, we would expect rectangles again, however, now they would be symmetric about the  $V_{G1} = V_{G2}$ . Here, we can flip the orientation of the magnetic moments through the use of electromagnetic radiation at resonant frequencies. The valley eigenstates are separated by a magnetic field and the Pauli blockade regime can be achieved. Therefore, QD1 acts as an effective spin filter regulating the current flow induced by EDSR in QD2. Pauli blockade has been utilized to implement spin-to-charge conversion for reading spin states of electrons in double QDs.

#### V. CRYO-COOLED FRONT-END ELECTRONICS FOR QUBITS

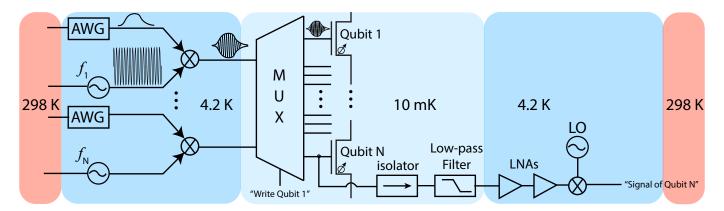

In commercial QCs, the equipment that is needed for qubit control and read-out (i.e., shaping electrical pulses, amplification, etc.) resides mainly at room temperature. As mentioned in the Introduction, this brings about many challenges. These challenges can be at least partially alleviated by integrating the same functionality with CMOS circuits in silicon chips, and implementing them in the 4-Kelvin stage of the dilution refrigerator of the quantum computer. This can reduce latency and increase overall system scalability. If we would extrapolate this practice, ultimately one would end up with so-called quantum

Fig. 5. Simplified schematic showing the front-end electronic circuits required for controlling ('writing') and measuring ('reading') spin qubits.

integrated circuits (QICs) where solid-state qubits (most likely silicon qubits) and peripheral electronics are monolothically co-integrated in the same microsystem. With successful future engineering of qubit devices, it might become possible to increase the operating temperature of the qubits from  $\approx 10 \, \text{mK}$ to 4.2 K and then operate the whole system at 4.2 K. At 4.2 K, the cooling power is several orders of magnitude higher than at 10 mK and more functionality can thus be implemented at 4.2 K. Figure 5 shows a simplified schematic that illustrates some of the required peripheral electronics to read and write spin qubits. The 'Write' operation of spin qubits (aka controlling, manipulating, or rotating) is shown on the left. The 'Read' operation (aka measuring) is shown on the right. To write a qubit, an RF pulse needs to be shaped with a wellcontrolled timing and amplitude and sent to the qubit. This can be done with an arbitrary wave-form generator (AWG), an RF oscillator, and a mixer. The AWG can be designed in CMOS as a digital-to-analog converter, the oscillator as a digital ring oscillator [50] or a voltage-controlled oscillator, and the mixer as a single nonlinear element, e.g., a MOSFET. Multiplexers allow to address multiple qubits at once. Frequency-division and time-division multiple-access techniques are also being investigated for this purpose. To read a qubit, typically RF reflectometry is used on the MOS gate, as briefly mentioned in Sec. IV-E. A read-out pulse is sent to a qubit, which picks up a frequency or phase shift depending on the state of the qubit. The RF read-out signal travels through the isolator, low-pass filter, and amplifier chain, before it reaches the down-converter for further processing. Other circuits such as current and voltage references [51] will also be necessary to realize QICs. Note that Fig. 5 is a simplified schematic and that many other architectures are under research. For instance, recently a structure has been proposed that resembles a one-transistor-onecapacitor dynamic random-access memory technology [52]. The qubit is placed on the spot of the capacitor and the MOSFET is used to read-out the state of the qubit. From the previous discussion, it has become clear that predicting the performance and power consumption of MOSFETs at deep cryogenic temperatures is essential. Digital, analog and RF models are required to meet trade-offs in the design phase.

# VI. MOSFET MODELING AT CRYOGENIC TEMPERATURES

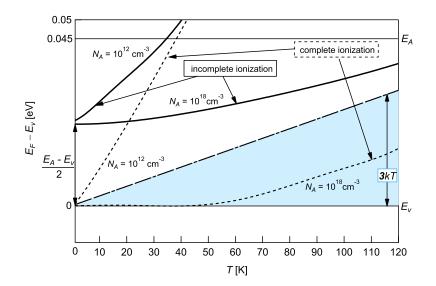

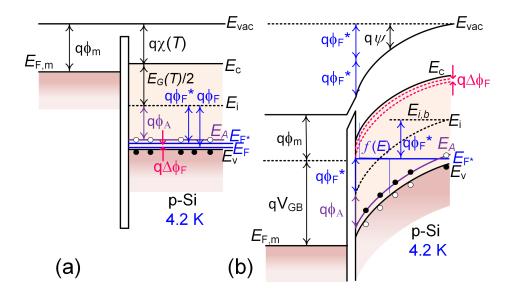

Industry-standard compact models are not readily available for deep cryogenic temperatures (<50 K) [54]. While DC current characteristics down to 77 K can still be adequately modeled, the embedded temperature-scaling in compact models is not sufficient to reach down to 4.2 K and lower temperatures using reasonable values for the physical parameters. This makes it clear that new physical phenomena popping up between 77 and 4.2 K need to be investigated in MOSFET device physics first [55]–[58]. Since the problem already arises in the DC characteristics, it is necessary to investigate the electrostatics and transport in MOSFETs at these extremely low temperatures [53]. A DC physical model that includes the missing phenomena certainly provides a more reliable basis for compact model development, especially when derivatives of the DC model will be required down the road for developing AC, RF, and noise models. In what follows, we first discuss the electrostatics and then the transport of MOSFETs at deep cryogenic temperatures. The first step in the derivation of the electrostatics is to check the validity of the Boltzmann relations of the mobile charge densities that are normally used in Poisson's equation. If the Maxwell-Boltzmann (MB) approximation of Fermi-Dirac statistics would not remain valid, complete Fermi-Dirac integrals would need to be used for the carrier distributions, complicating the development of an explicit model. Fortunately, for non-degenerate doping concentrations and deep-cryogenic temperatures, the MB approximation of Fermi-Dirac statistics remains valid [53]. As shown in Fig.6, the distance between  $E_F$  and the band edges remains larger than  $\approx 3k_BT$  in this temperature range (with  $k_B$  the Boltzmann constant and T temperature). We conclude that the Poisson-Boltzmann equation is a good starting point to derive the MOSFET electrostatics at deep-cryogenic temperatures.

Dopants in the source and drain contacts can be assumed completely ionized at all times due to heavy doping effects [59], [60]. 'Freezeout' or thermal de-ionization of the dopants in the non-degenerately doped MOSFET body [61] can be included in the Poisson-Boltzmann equation simply by replacing  $N_A$  with  $N_A \times P(T, N_A)$  (where  $N_A$  is the dopant concentration and  $P(T, N_A)$  the ionization probability, con-

Fig. 6. Fermi level position in the bandgap at cryogenic temperatures for silicon MOSFET with a *p*-type body. Validity of the Maxwell Boltzmann approximation only when incomplete ionization of the dopants in the MOSFET body is taken into account. Adapted from [53].

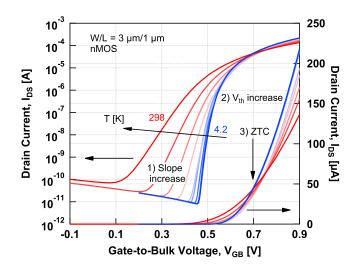

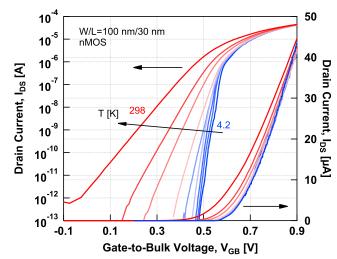

sidering an *n*-channel MOSFET). The ionization probability follows from semiconductor statistics:  $P(T, N_A)$  is given by the Fermi-Dirac occupation probability f(E) of the acceptor energy level  $E_A$ . Figure 6 highlighted the first consequence of incomplete ionization of the dopants in the MOSFET body: incomplete ionization ensures that the MB approximation remains valid ( $|E_F - \text{band edge}| > \approx 3k_BT$ ) [53]. For complete ionization,  $E_F$  would fall in the  $3k_BT$  energy window below the band edge. The second consequence of freezeout (in the bulk) is that the inversion threshold is modified at each temperature and doping concentration from  $2\Phi_{\rm F}$  to  $\Phi_{\rm F} + \Phi_{\rm F}^*$ , where  $\Phi_{\rm F}^* < \Phi_{\rm F}$  [62]. Therefore, although counterintuitive, incomplete ionization of the dopants lowers the inversion threshold at each temperature below 298 K. It is thus a misconception to assume that the increase in threshold voltage  $(V_{th})$  in the I-Vcharacteristics for T decreasing from room down to deepcryogenic temperature (as in Figs. 7 and 8), is due to the initial dopant freezeout in the channel. In other words, the dopants that are thermally de-ionized in the channel in flatband and at deep-cryogenic temperature, say 4.2 K, do not require more gate voltage to becomes ionized. The field-assisted ionization of the dopants is taken into account implicitly in the statistics of  $f(E_A)$ , but is already completed near flatband where the current is still below a measurable value at 4.2 K. The increase in  $V_{th}$  with decreasing T is explained by the compound effect of exponential scaling of the Fermi-Dirac function f(E)and the widening of the bandgap [63], and thus not by the freezeout and/or field-assisted ionization of the dopants [62]. Besides dopants, another important element of electrostatics are the interface traps at the boundary between the channel and gate-oxide [64]. The importance of interface traps on the MOSFET's electrostatics at deep-cryogenic temperatures has since long been recognized [65]. The density of interface traps in the bandgap typically increases toward the band edges [66]. Since weak inversion at deep-cryogenic temperatures happens when the bands are bent such that  $E_F$  at the interface is a few meV below the band edge (as shown in Fig. 9), the number of interface states active in weak inversion can be substantially higher at deep-cryogenic temperatures than at room temperature. However, this increase should not be abused to explain the subthreshold-slope saturation.

'Subthreshold-slope saturation' means that the slope of the  $I_D - V_G$  curve in subthreshold does not reach its maximum attainable value as theoretically predicted by the thermal limit for that temperature. The subthreshold-slope saturation has been measured in many types of FETs at deep-cryogenic temperatures [67]–[78]. It is usually shown by plotting the inverse subthreshold slope (or subthreshold swing SS) beside the Boltzmann thermal limit  $SS = (k_B T/q) \ln 10$ . It is then clear that the trend of the measured SS starts to roll off from the linear Boltzmann limit below  $\approx 50$  K. This gives around 4.2 K typically a  $\Delta SS \approx 10 \,\mathrm{mV/decade}$  higher than the Boltzmann limit (SS  $\approx 1 \,\text{mV/decade}$ ). This behavior continues down to temperatures as low as tens of millikelvin [73], [77] Such high SS can only be explained with the Boltzmann theory when anomalously high densities are used for the interface traps [77]. This highlights that some physical phenomenon is lacking to explain  $\Delta SS$ .

Band tails have been proposed to explain  $\Delta SS$  by Bohuslavskyi *et al.* [79]. Due to disorder and finiteness of the crystal, band edges are not perfectly sharp. A density-of-states tail thus seeps into the bandgap, typically with exponential behavior [80]. However, band-tail electrostatics and drift-diffusion transport is not sufficient to explain  $\Delta SS$ . Beckers *et al.* have shown that the explanation for slope saturation does not lie in degraded electrostatics, but, rather, in an additional

Fig. 7. Low-temperature measurement results in a 28-nm bulk CMOS technology down to 4.2 K. Annotations highlight some typical observations: 1) improvement of the subthreshold slope, 2) increase in threshold voltage, 3) zero temperature-coefficient (ZTC) bias point. Adapted from [62]

quantum transport mechanism which flows in parallel to the drift-diffusion current [81]. This additional current component is a band-tail tunneling current (a hopping current through localized states in the channel) which becomes dominant over the drift and diffusion currents in weak inversion at deepcryogenic temperatures. This hopping current has a worse subthreshold slope than the thermal limit from the diffusion current, and, thus, explains  $\Delta SS$  [81]. Instead of  $(k_B T/q) \ln 10$ , the limit of SS at deep-cryogenic temperatures is derived as  $SS = mW_t \ln 10$ , where  $W_t$  is the characteristic extension of the exponential band tail in the bandgap (expressed in eV).  $W_t$  is typically in the order of a couple of meV [82]. The slope factor m includes the interface-trap density. Using  $SS = mW_t \ln 10$  instead of  $SS = m(k_B T/q) \ln 10$  gives interface-state densities that do not reach anomalously high values at sub-Kelvin temperatures anymore [81]. Furthermore, accounting for the hopping current leads to a SS theory that explains the measured SS roll-off from room down to sub-Kelvin temperature [81].

Besides the saturation of the subthreshold slope, oscillations in weak inversion have been measured in the current characteristics of some devices fabricated in advanced and mature CMOS technologies [74], [76], [83]. These oscillations are most prominent at low drain bias (in the order of 1-10 mV) and temperatures lower than  $\approx 36$  K. Simoen *et al.* hint at a resonant tunneling current to be responsible for this phenomenon [83]. The oscillations are characterized by regions of negative-differential resistance, which is indeed a characteristic for resonant tunneling as exemplified by the wellknown resonant-tunneling diode (RTD) [84]. In an RTD, two potential barriers are typically created by stacking different materials [85]. For more tunnel barriers, this results in a 'superlattice' which can be exploited in the source of exploratory nanotransistors to obtain steep subthreshold slopes [86], [87].

Fig. 8. Low-temperature measurement results in a minimum-length device of a 28-nm bulk CMOS technology down to 4.2 K. Adapted from [62]

In a standard commercial MOSFET, however, the manifestation of resonant tunneling is not immediately clear. Yet, a string of consecutive interface states in the channel can form a sequence of potential barriers between source and drain, and thus an accidental superlattice is established through which minority carriers can resonantly tunnel. Other defects than interface traps with active energies close to a band edge should also be considered for that purpose (e.g., dopants diffused unintentionally from the source and drain contacts into the channel [74], [88]).

Above, we have discussed the current components in weak inversion (drift, diffusion, hopping, and resonant tunneling). In strong inversion, the drift current dominates as usual. The main hurdle to overcome is then a mobility model [89] that scales over temperature, gate and drain voltages, and device aspect ratios [90], [91] The self-heating of the carriers is important as well in this bias regime [92]. Furthermore, quantum confinement effects and ballisticity should be taken into account in an effective carrier mobility [93]–[95].

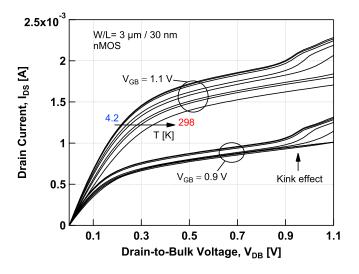

As a final note, the kink effect measured in the output characteristics at deep-cryogenic temperatures is not limited to mature CMOS technologies with micron length scales and high operating voltages. This phenomenon is also measured in contemporary commercial bulk CMOS technologies (e.g., 180nm CMOS [73], and 28-nm CMOS). The appearance of the kink in 28-nm CMOS technology at deep-cryogenic temperatures is shown for the first time here in Fig. 10. The kink happens at an operating voltage above 0.9 V. For 180-nm CMOS, the kink happens around 2V [73]. Since the performance is unstable around the kink, the cryo-CMOS designer should be aware of this phenomenon. The bias voltage should be limited depending on the technology. Phenomena that have not been part of our discussion are: mismatch [96], [97], short-channel effects [98], non-uniform doping [99], hysteresis [100], hotcarrier degradation [101] and other reliability phenomena.

Fig. 9. MOSFET band diagrams at 4.2 K (a) flatband, (b) weak inversion. Adapted from [62].

# VII. CONCLUSION

In this review, we described different quantum computing implementations with a focus on the silicon initiative. This is mostly a brief review with short explanations of the underlying physics for different aspects of quantum computing. The importance of developing low-temperature peripheral electronics and understanding the solid state physics in MOSFETs at deep cryogenic temperatures were explained. Even though the field of quantum computing and the infrastructure around it is still in its infancy, quantum computation, teleportation, and cryptography are nowadays already commercially available.

Fig. 10. The kink effect sets in below T = 110 K and above  $V_{DB} = 0.9$  V in the output characteristics of a commercial 28-nm bulk CMOS technology.

#### REFERENCES

- [1] https://ai.google/research/teams/applied-science/quantum-ai/.

- [2] https://cloudblogs.microsoft.com/quantum/2018/06/06/the-microsoftapproach-to-quantum-computing/.

- [3] https://www.research.ibm.com/ibm-q/network/overview/.

- [4] https://www.intel.com/content/www/us/en/research/quantumcomputing.html.

- [5] https://www.lockheedmartin.com/en-ca/index.html.

- [6] R. P. Feynman, "Simulating physics with computers," *International Journal of Theoretical Physics*, vol. 21, no. 6, pp. 467–488, Jun 1982. [Online]. Available: https://doi.org/10.1007/BF02650179

- [7] D. Deutsch, "Quantum theory, the Church-Turing principle and the universal quantum computer," *Proceedings of the Royal Society of London. A. Mathematical and Physical Sciences*, vol. 400, no. 1818, pp. 97–117, 1985.

- [8] P. W. Shor, "Polynomial-time algorithms for prime factorization and discrete logarithms on a quantum computer," *SIAM J. Comput.*, vol. 26, no. 5, pp. 1484–1509, Oct. 1997. [Online]. Available: http://dx.doi.org/10.1137/S0097539795293172

- [9] P. W. Shor, "Algorithms for quantum computation: discrete logarithms and factoring," in *Proceedings 35th Annual Symposium on Foundations* of Computer Science, Nov 1994, pp. 124–134.

- [10] L. K. Grover, "A fast quantum mechanical algorithm for database search," in *Proceedings of the Twenty-eighth Annual ACM Symposium* on Theory of Computing, ser. STOC '96. New York, NY, USA: ACM, 1996, pp. 212–219. [Online]. Available: http://doi.acm.org/10. 1145/237814.237866

- [11] —, "Quantum mechanics helps in searching for a needle in a haystack," *Phys. Rev. Lett.*, vol. 79, pp. 325–328, Jul 1997. [Online]. Available: https://link.aps.org/doi/10.1103/PhysRevLett.79.325

- [12] https://www.extremetech.com/computing/84228-first-ever-commercialquantum-computer-now-available-for-10-million.

- [13] https://www.dwavesys.com/home.

- [14] https://www.scottaaronson.com/blog/?p=1400.

- [15] https://www.extremetech.com/computing/84228-first-ever-commercialquantum-computer-now-available-for-10-million.

- [16] https://ec.europa.eu/digital-single-market/en/quantum-technologies.

- [17] https://www.mos-quito.eu/.

- [18] R. Maurand, X. Jehl, D. Kotekar-Patil, A. Corna, H. Bohuslavskyi, R. Laviéville, L. Hutin, S. Barraud, M. Vinet, M. Sanquer et al., "A CMOS silicon spin qubit," *Nature communications*, vol. 7, p. 13575, 2016.

- [19] M. H. Devoret and R. J. Schoelkopf, "Superconducting circuits for quantum information: An outlook," *Science*, vol. 339, no. 6124, pp.

1169-1174, 2013. [Online]. Available: https://science.sciencemag.org/ content/339/6124/1169

- [20] B. E. Kane, "A silicon-based nuclear spin quantum computer," *Nature*, vol. 393, pp. 133–137, May 1998.

- [21] J. J. Pla, K. Y. Tan, J. P. Dehollain, W. H. Lim, J. J. Morton, D. N. Jamieson, A. S. Dzurak, and A. Morello, "A single-atom electron spin qubit in silicon," *Nature*, vol. 489, no. 7417, p. 541, 2012.

- [22] N. T. Bronn, B. Abdo, K. Inoue, S. Lekuch, A. D. Córcoles, J. B. Hertzberg, M. Takita, L. S. Bishop, J. M. Gambetta, and J. M. Chow, "Fast, high-fidelity readout of multiple qubits," *Journal of Physics: Conference Series*, vol. 834, p. 012003, 2017.

- [23] L. A. Tracy, D. R. Luhman, S. M. Carr, N. C. Bishop, G. A. Ten Eyck, T. Pluym, J. R. Wendt, M. P. Lilly, and M. S. Carroll, "Single shot spin readout using a cryogenic high-electron-mobility transistor amplifier at sub-Kelvin temperatures," *Applied Physics Letters*, vol. 108, no. 6, p. 063101, Feb. 2016. [Online]. Available: http://aip.scitation.org/doi/10.1063/1.4941421

- [24] S. R. Ekanayake, T. Lehmann, A. S. Dzurak, R. G. Clark, and A. Brawley, "Characterization of SOS-CMOS FETs at Low Temperatures for the Design of Integrated Circuits for Quantum Bit Control and Readout," *IEEE Transactions on Electron Devices*, vol. 57, no. 2, pp. 539–547, Feb 2010.

- [25] E. Charbon, F. Sebastiano, A. Vladimirescu, H. Homulle, S. Visser, L. Song, and R. M. Incandela, "Cryo-CMOS for quantum computing," in 2016 IEEE International Electron Devices Meeting (IEDM), Dec 2016, pp. 13.5.1–13.5.4.

- [26] L. Vandersypen, H. Bluhm, J. Clarke, A. Dzurak, R. Ishihara, A. Morello, D. Reilly, L. Schreiber, and M. Veldhorst, "Interfacing spin qubits in quantum dots and donors-hot, dense, and coherent," *npj Quantum Information*, vol. 3, no. 1, p. 34, 2017.

- [27] J. M. Hornibrook, J. I. Colless, I. D. Conway Lamb, S. J. Pauka, H. Lu, A. C. Gossard, J. D. Watson, G. C. Gardner, S. Fallahi, M. J. Manfra, and D. J. Reilly, "Cryogenic Control Architecture for Large-Scale Quantum Computing," *Phys. Rev. Applied*, vol. 3, p. 024010, Feb 2015. [Online]. Available: https: //link.aps.org/doi/10.1103/PhysRevApplied.3.024010

- [28] C. Degenhardt, L. Geck, A. Kruth, P. Vliex, and S. van Waasen, "CMOS Based Scalable Cryogenic Control Electronics for Qubits," in 2017 IEEE International Conference on Rebooting Computing (ICRC), Nov 2017, pp. 1–4.

- [29] M. Veldhorst, H. Eenink, C. Yang, and A. Dzurak, "Silicon CMOS architecture for a spin-based quantum computer," *Nature communications*, vol. 8, no. 1, p. 1766, 2017.

- [30] J. C. Bardin, E. Jeffrey, E. Lucero, T. Huang, O. Naaman, R. Barends, T. White, M. Giustina, D. Sank, P. Roushan, K. Arya, B. Chiaro, J. Kelly, J. Chen, B. Burkett, Y. Chen, A. Dunsworth, A. Fowler, B. Foxen, C. Gidney, R. Graff, P. Klimov, J. Mutus, M. McEwen, A. Megrant, M. Neeley, C. Neill, C. Quintana, A. Vainsencher, H. Neven, and J. Martinis, "A 28nm Bulk-CMOS 4-to-8 GHz < 2mW Cryogenic Pulse Modulator for Scalable Quantum Computing," in 2019 IEEE International Solid- State Circuits Conference - (ISSCC), Feb 2019, pp. 456–458.

- [31] M. A. Nielsen and I. Chuang, "Quantum computation and quantum information," 2002.

- [32] A. Einstein, B. Podolsky, and N. Rosen, "Can quantum-mechanical description of physical reality be considered complete?" *Phys. Rev.*, vol. 47, pp. 777–780, May 1935. [Online]. Available: https://link.aps.org/doi/10.1103/PhysRev.47.777

- [33] M. Le Bellac, A Short Introduction to Quantum Information and Quantum Computation. Cambridge University Press, 2006.

- [34] D. P. DiVincenzo, "The physical implementation of quantum computation," *Fortschritte der Physik*, vol. 48, no. 911, pp. 771–783.

- [35] L. M. Vandersypen and I. L. Chuang, "NMR techniques for quantum control and computation," *Reviews of modern physics*, vol. 76, no. 4, p. 1037, 2005.

- [36] P. Schindler, D. Nigg, T. Monz, J. T. Barreiro, E. Martinez, S. X. Wang, S. Quint, M. Brandl, V. Nebendahl, C. Roos, M. Chwalla, M. Hennrich, and R. Blatt, "A quantum information processor with trapped ions," *New Journal of Physics*, vol. 15, p. 123012, 12 2013.

- [37] D. G. Cory, A. F. Fahmy, and T. F. Havel, "Ensemble quantum computing by NMR spectroscopy," *Proceedings of the National Academy of Sciences*, vol. 94, no. 5, pp. 1634–1639, 1997. [Online]. Available: https://www.pnas.org/content/94/5/1634

- [38] L. M. Vandersypen, M. Steffen, G. Breyta, C. S. Yannoni, M. H. Sherwood, and I. L. Chuang, "Experimental realization of Shor's quantum factoring algorithm using nuclear magnetic resonance," *Nature*, vol. 414, no. 6866, p. 883, 2001.

- [39] C. D. Bruzewicz, J. Chiaverini, R. McConnell, and J. M. Sage, "Trapped-ion quantum computing: Progress and challenges," *Applied Physics Reviews*, vol. 6, no. 2, p. 021314, 2019. [Online]. Available: https://doi.org/10.1063/1.5088164

- [40] C. Monroe and J. Kim, "Scaling the ion trap quantum processor," *Science*, vol. 339, no. 6124, pp. 1164–1169, 2013. [Online]. Available: https://science.sciencemag.org/content/339/6124/1164

- [41] L. Childress and R. Hanson, "Diamond NV centers for quantum computing and quantum networks," *MRS Bulletin*, vol. 38, no. 2, p. 134138, 2013.

- [42] H. Bluhm, S. Foletti, I. Neder, M. Rudner, D. Mahalu, V. Umansky, and A. Yacoby, "Dephasing time of GaAs electron-spin qubits coupled to a nuclear bath exceeding 200 μs," *Nature Physics*, vol. 7, no. 2, p. 109, 2011.

- [43] L. R. Schreiber and H. Bluhm, "Quantum computation: Silicon comes back," *Nature nanotechnology*, vol. 9, no. 12, p. 966, 2014.

- [44] L. Hutin, R. Maurand, D. Kotekar-Patil, A. Corna, H. Bohuslavskyi, X. Jehl, S. Barraud, S. De Franceschi, M. Sanquer, and M. Vinet, "Si CMOS platform for quantum information processing," in 2016 IEEE Symposium on VLSI Technology, June 2016, pp. 1–2.

- [45] https://www.imec-int.com/en/articles/imec-and-cea-leti-join-forces-onartificial-intelligence-and-quantum-computing.

- [46] A. C. Betz, M. L. V. Tagliaferri, M. Vinet, M. Brostrm, M. Sanquer, A. J. Ferguson, and M. F. Gonzalez-Zalba, "Reconfigurable quadruple quantum dots in a silicon nanowire transistor," *Applied Physics Letters*, vol. 108, no. 20, p. 203108, 2016.

- [47] A. Crippa, R. Maurand, L. Bourdet, D. Kotekar-Patil, A. Amisse, X. Jehl, M. Sanquer, R. Laviéville, H. Bohuslavskyi, L. Hutin, S. Barraud, M. Vinet, Y.-M. Niquet, and S. De Franceschi, "Electrical Spin Driving by g-Matrix Modulation in Spin-Orbit Qubits," *Phys. Rev. Lett.*, vol. 120, p. 137702, Mar 2018. [Online]. Available: https://link.aps.org/doi/10.1103/PhysRevLett.120.137702

- [48] A. Corna, L. Bourdet, R. Maurand, A. Crippa, D. Kotekar-Patil, H. Bohuslavskyi, R. Lavieville, L. Hutin, S. Barraud, X. Jehl, M. Vinet, S. De Franceschi, Y.-M. Niquet, and M. Sanquer, "Electrically driven electron spin resonance mediated by spin-valley-orbit coupling in a silicon quantum dot," *npj quantum information*, vol. 4, p. 6, 02 2018.

- [49] W. G. van der Wiel, S. De Franceschi, J. M. Elzerman, T. Fujisawa, S. Tarucha, and L. P. Kouwenhoven, "Electron transport through double quantum dots," *Rev. Mod. Phys.*, vol. 75, pp. 1–22, Dec 2002. [Online]. Available: https://link.aps.org/doi/10.1103/RevModPhys.75.1

- [50] H. Bohuslavskyi, S. Barraud, V. Barral, M. Cass, L. Le Guevel, L. Hutin, B. Bertrand, A. Crippa, X. Jehl, G. Pillonnet, A. G. M. Jansen, F. Arnaud, P. Galy, R. Maurand, S. De Franceschi, M. Sanquer, and M. Vinet, "Cryogenic Characterization of 28-nm FD-SOI Ring Oscillators With Energy Efficiency Optimization," *IEEE Transactions* on Electron Devices, vol. 65, no. 9, pp. 3682–3688, Sep. 2018.

- [51] H. Homulle, F. Sebastiano, and E. Charbon, "Deep-Cryogenic Voltage References in 40-nm CMOS," *IEEE Solid-State Circuits Letters*, vol. 1, no. 5, pp. 110–113, May 2018.

- [52] S. Schaal, A. Rossi, V. N. Ciriano-Tejel, T.-Y. Yang, S. Barraud, J. J. Morton, and M. F. Gonzalez-Zalba, "A CMOS dynamic random access architecture for radio-frequency readout of quantum devices," *Nature Electronics*, p. 1, 2019.

- [53] A. Beckers, F. Jazaeri, and C. Enz, "Cryogenic MOS Transistor Model," *IEEE Transactions on Electron Devices*, vol. 65, no. 9, pp. 3617–3625, Sep. 2018.

- [54] A. Akturk, M. Holloway, S. Potbhare, D. Gundlach, B. Li, N. Goldsman, M. Peckerar, and K. P. Cheung, "Compact and Distributed Modeling of Cryogenic Bulk MOSFET Operation," *IEEE Transactions* on *Electron Devices*, vol. 57, no. 6, pp. 1334–1342, June 2010.

- [55] R. Kirschman, "Cold electronics: an overview," *Cryogenics*, vol. 25, no. 3, pp. 115 122, 1985.

- [56] F. Balestra and G. Ghibaudo, "Brief review of the MOS device physics for low temperature electronics," *Solid-State Electronics*, vol. 37, no. 12, pp. 1967 – 1975, 1994.

- [57] E. A. Gutierrez-D, J. Deen, and C. Claeys, Low temperature electronics: physics, devices, circuits, and applications. Elsevier, 2000.

- [58] F. Balestra and G. Ghibaudo, Device and circuit cryogenic operation for low temperature electronics. Springer, 2001.

- [59] A. Akturk, J. Allnutt, Z. Dilli, N. Goldsman, and M. Peckerar, "Device modeling at cryogenic temperatures: Effects of incomplete ionization," *IEEE Transactions on Electron Devices*, vol. 54, no. 11, pp. 2984– 2990, Nov 2007.

- [60] N. F. Mott and E. A. Davis, *Electronic processes in non-crystalline materials*. OUP Oxford, 2012.

- [61] F. Balestra, L. Audaire, and C. Lucas, "Influence of substrate freeze-out on the characteristics of MOS transistors at very low temperatures," *Solid-State Electronics*, vol. 30, no. 3, pp. 321 – 327, 1987. [Online]. Available: http://www.sciencedirect.com/science/ article/pii/0038110187901900

- [62] A. Beckers, F. Jazaeri, and C. Enz, "Cryogenic MOSFET Threshold Voltage Model," arXiv preprint arXiv:1904.09911, 2019, Accepted ESSDERC 2019.

- [63] K. P. O'Donnell and X. Chen, "Temperature dependence of semiconductor band gaps," *Applied Physics Letters*, vol. 58, no. 25, pp. 2924–2926, Jun. 1991. [Online]. Available: http: //aip.scitation.org/doi/10.1063/1.104723

- [64] Farzan Jazaeri and Jean-Michel Sallese, "Modeling nanowire and double-gate junctionless field-effect transistors," *Cambridge University Press*, 2017.

- [65] I. M. Hafez, G. Ghibaudo, and F. Balestra, "Assessment of interface state density in silicon metal–oxide–semiconductor transistors at room, liquidnitrogen, and liquid–helium temperatures," *Journal of Applied Physics*, vol. 67, no. 4, pp. 1950–1952, 1990.

- [66] M. Cassé, K. Tachi, S. Thiele, and T. Ernst, "Spectroscopic charge pumping in Si nanowire transistors with a high-k/metal gate," *Applied Physics Letters*, vol. 96, no. 12, p. 123506, 2010.

- [67] A. Kamgar, "Subthreshold behavior of silicon MOSFETs at 4.2 K," Solid-State Electronics, vol. 25, no. 7, pp. 537–539, Jul. 1982.

- [68] M. Shin, M. Shi, M. Mouis, A. Cros, E. Josse, G. T. Kim, and G. Ghibaudo, "Low temperature characterization of 14 nm FDSOI CMOS devices," in 2014 11th International Workshop on Low Temperature Electronics (WOLTE), 2014, pp. 29–32.

- [69] T. Elewa, F. Balestra, S. Cristoloveanu, I. M. Hafez, J. Colinge, A. Auberton-Herve, and J. R. Davis, "Performance and physical mechanisms in SIMOX MOS transistors operated at very low temperature," *IEEE Transactions on Electron Devices*, vol. 37, no. 4, pp. 1007–1019, April 1990.

- [70] A. Beckers, F. Jazaeri, A. Ruffino, C. Bruschini, A. Baschirotto, and C. Enz, "Cryogenic characterization of 28 nm bulk CMOS technology for quantum computing," in 2017 47th European Solid-State Device Research Conference (ESSDERC), Sept 2017, pp. 62–65.

- [71] A. Beckers, F. Jazaeri, and C. Enz, "Characterization and Modeling of 28-nm Bulk CMOS Technology Down to 4.2 K," *IEEE Journal of the Electron Devices Society*, vol. 6, pp. 1007–1018, 2018.

- [72] H. Homulle, L. Song, E. Charbon, and F. Sebastiano, "The Cryogenic Temperature Behavior of Bipolar, MOS, and DTMOS Transistors in Standard CMOS," *IEEE Journal of the Electron Devices Society*, vol. 6, pp. 263–270, 2018.

- [73] R. M. Incandela, L. Song, H. Homulle, E. Charbon, A. Vladimirescu, and F. Sebastiano, "Characterization and Compact Modeling of Nanometer CMOS Transistors at Deep-Cryogenic Temperatures," *IEEE Journal of the Electron Devices Society*, vol. 6, pp. 996–1006, 2018.

- [74] H. Bohuslavskyi, S. Barraud, M. Cassé, V. Barrai, B. Bertrand, L. Hutin, F. Arnaud, P. Galy, M. Sanquer, S. De Franceschi, and M. Vinet, "28 nm Fully-depleted SOI technology: Cryogenic control electronics for quantum computing," in 2017 Silicon Nanoelectronics Workshop (SNW), June 2017, pp. 143–144.

- [75] A. Beckers, F. Jazaeri, H. Bohuslavskyi, L. Hutin, S. De Franceschi, and C. Enz, "Design-oriented modeling of 28 nm FDSOI CMOS technology down to 4.2 K for quantum computing," in 2018 Joint International EUROSOI Workshop and International Conference on Ultimate Integration on Silicon (EUROSOI-ULIS), March 2018, pp. 1–4.

- [76] A. Beckers, F. Jazaeri, H. Bohuslavskyi, L. Hutin, S. D. Franceschi, and C. Enz, "Characterization and modeling of 28-nm FDSOI CMOS technology down to cryogenic temperatures," *Solid-State Electronics*, vol. 159, pp. 106 – 115, 2019, sI: EUROSOI 2018.

- [77] P. Galy, P. Lemieux, J. C. Lemyre, F. Arnaud, D. Drouin, and M. Pioro-Ladrire, "Cryogenic temperature characterization of a 28 nm FD-SOI dedicated structure for advanced CMOS and quantum technologies cointegration," *IEEE Journal of the Electron Devices Society*, pp. 1–1, 2018.

- [78] R. Trevisoli, M. de Souza, R. T. Doria, V. Kilchtyska, D. Flandre, and M. A. Pavanello, "Junctionless nanowire transistors operation at temperatures down to 4.2 K," *Semiconductor Science and Technology*, vol. 31, no. 11, p. 114001, 2016.

- [79] H. Bohuslavskyi, A. G. M. Jansen, S. Barraud, V. Barral, M. Cassé, L. Le Guevel, X. Jehl, L. Hutin, B. Bertrand, G. Billiot, G. Pillonnet, F. Arnaud, P. Galy, S. De Franceschi, M. Vinet, and M. Sanquer, "Cryogenic Subthreshold Swing Saturation in FD-SOI MOSFETs Described With Band Broadening," *IEEE Electron Device Letters*, vol. 40, no. 5, pp. 784–787, May 2019.

- [80] P. Van Mieghem, "Theory of band tails in heavily doped semiconductors," *Rev. Mod. Phys.*, vol. 64, pp. 755–793, Jul 1992. [Online]. Available: https://link.aps.org/doi/10.1103/RevModPhys.64. 755

- [81] A. Beckers, F. Jazaeri, and C. Enz, "Revised theoretical limit of the subthreshold swing in field-effect transistors," arXiv preprint Version 2, arXiv:1811.09146, 2019. [Online]. Available: https: //arxiv.org/abs/1811.09146

- [82] R. M. Jock, S. Shankar, A. M. Tyryshkin, J. He, K. Eng, K. D. Childs, L. A. Tracy, M. P. Lilly, M. S. Carroll, and S. A. Lyon, "Probing band-tail states in silicon metal-oxide-semiconductor heterostructures with electron spin resonance," *Applied Physics Letters*, vol. 100, no. 2, p. 023503, Jan. 2012. [Online]. Available: http://aip.scitation.org/doi/10.1063/1.3675862

- [83] E. Simoen, C. Claeys, and J. Martino, "Parameter Extraction of MOSFETs Operated at Low Temperature," *Journal de Physique IV Colloque*, vol. 06, no. C3, pp. C3–29–C3–42, 1996.

- [84] H. Mizuta and T. Tanoue, *The physics and applications of resonant tunnelling diodes*. Cambridge University Press, 2006, vol. 2.

- [85] L. Chang, L. Esaki, and R. Tsu, "Resonant tunneling in semiconductor double barriers," *Applied Physics Letters*, vol. 24, no. 12, pp. 593–595, 1974.

- [86] E. Gnani, S. Reggiani, A. Gnudi, and G. Baccarani, "Steep-slope nanowire FET with a superlattice in the source extension," in 2010 Proceedings of the European Solid State Device Research Conference, Sep. 2010, pp. 380–383.

- [87] A. Beckers, M. Thewissen, and B. Sorée, "Energy filtering in silicon nanowires and nanosheets using a geometric superlattice and its use for steep-slope transistors," *Journal of Applied Physics*, vol. 124, no. 14, p. 144304, 2018.

- [88] F. A. Zwanenburg, A. S. Dzurak, A. Morello, M. Y. Simmons, L. C. Hollenberg, G. Klimeck, S. Rogge, S. N. Coppersmith, and M. A. Eriksson, "Silicon quantum electronics," *Reviews of modern physics*, vol. 85, no. 3, p. 961, 2013.

- [89] F. Jazaeri, A. Pezzotta, and C. Enz, "Free carrier mobility extraction in fets," *IEEE Transactions on Electron Devices*, vol. 64, no. 12, pp. 5279–5283, Dec 2017.

- [90] A. Emrani, F. Balestra, and G. Ghibaudo, "On the understanding of electron and hole mobility models from room to liquid helium temperatures," *Solid-State Electronics*, vol. 37, no. 10, pp. 1723 – 1730, 1994. [Online]. Available: http://www.sciencedirect.com/science/ article/pii/0038110194902194

- [91] A. Emrani, F. Balestra, and G. Ghibaudo, "Generalized mobility law for drain current modeling in Si MOS transistors from liquid helium to room temperatures," *IEEE Transactions on Electron Devices*, vol. 40, no. 3, pp. 564–569, March 1993.

- [92] K. Triantopoulos, M. Cassé, S. Barraud, S. Haendler, E. Vincent, M. Vinet, F. Gaillard, and G. Ghibaudo, "Self-Heating Effect in FDSOI Transistors Down to Cryogenic Operation at 4.2 K," *IEEE Transactions* on *Electron Devices*, pp. 1–8, 2019.

- [93] J. Colinge, A. J. Quinn, L. Floyd, G. Redmond, J. C. Alderman, Weize Xiong, C. R. Cleavelin, T. Schulz, K. Schruefer, G. Knoblinger, and P. Patruno, "Low-temperature electron mobility in Trigate SOI MOSFETs," *IEEE Electron Device Letters*, vol. 27, no. 2, pp. 120– 122, Feb 2006.

- [94] G. Baccarani and S. Reggiani, "A compact double-gate MOSFET model comprising quantum-mechanical and non-static effects," in 1999 International Conference on Simulation of Semiconductor Processes and Devices. SISPAD'99 (IEEE Cat. No.99TH8387), Sep. 1999, pp. 11–14.

- [95] F. Jazaeri and J. Sallese, "Charge-based epfl hemt model," *IEEE Transactions on Electron Devices*, vol. 66, no. 3, pp. 1218–1229, March 2019.

- [96] K. Das and T. Lehmann, "SOS current mirror matching at 4K: A brief study," in *Proceedings of 2010 IEEE International Symposium* on Circuits and Systems, May 2010, pp. 3405–3408.

- [97] P. A. 't Hart, J. P. G. van Dijk, M. Babaie, E. Charbon, A. Vladimircscu, and F. Sebastiano, "Characterization and Model Validation of Mismatch in Nanometer CMOS at Cryogenic Temperatures," in 2018 48th European Solid-State Device Research Conference (ESSDERC), Sep. 2018, pp. 246–249.

- [98] J. C. S. Woo and J. D. Plummer, "Short-channel effects in MOSFET's at liquid-Nitrogen temperature," *IEEE Transactions on Electron De*vices, vol. 33, no. 7, pp. 1012–1019, July 1986.

- [99] S. M. Sze and K. K. Ng, *Physics of semiconductor devices*. John wiley & sons, 2006.

- [100] B. Dierickx, L. Warmerdam, E. R. Simoen, J. Vermeiren, and C. Claeys, "Model for hysteresis and kink behavior of MOS transistors operating at 4.2 K," *IEEE Transactions on Electron Devices*, vol. 35, no. 7, pp. 1120–1125, July 1988.

- [101] M. Song, K. P. MacWilliams, and J. C. S. Woo, "Comparison of NMOS and PMOS hot carrier effects from 300 to 77 K," *IEEE Transactions* on Electron Devices, vol. 44, no. 2, pp. 268–276, Feb 1997.