Radiation Hardened VA416X0 32-Bit Arm<sup>®</sup> Cortex<sup>®</sup>-M4 (with FPU) microcontroller manufactured with HARDSIL<sup>®</sup> technology offering best in class radiation performance and latch-up immunity.

#### MEMORY CONFIGURATION OPTIONS

- Internal FRAM (VA41630 only)

- External SPI NVM (for code boot)

- External parallel NVM (for code boot)

- External memory bus interface (EBI for code or data)

#### RADIATION HARDENED PERFORMANCE

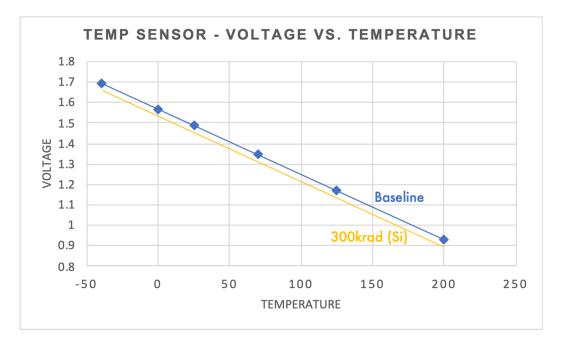

- VA41620 Total Ionizing Dose (TID) > 300 krad(Si)

- VA41630 Total Ionizing Dose (TID) > 200 krad(Si)<sup>1</sup>

- Soft Error Rate (SER) < 1E-15 errors / bit-day w/ EDAC & Scrub enabled (See Section 7 for details)

- Single-Event Latch-Up (SEL) immunity to LET > 110 MeVcm<sup>2</sup> / mg

#### **KEY FEATURES**

- Manufactured with HARDSIL<sup>®</sup> technology

- RAD hardened Registers with Triple-Mode Redundancy (TMR)

- 32-bit Arm<sup>®</sup> Cortex<sup>®</sup>-M4 processor

Single-Precision Floating-Point Unit (FPU)

SWD based debug interface

- Operating voltages

- GPIO 3.3 ± 10% V

- Core 1.5 ± 10% V

- Clock rate up to 100 MHz

- Internal 20 MHz oscillator for fail-safe clocking

- Memory

- 64 Kbyte on-chip data and 256 Kbyte on-chip program memory SRAM

- 256 Kbyte SPI FRAM (VA41630 only)

- Error Detection and Correction (EDAC)

- Built-in Scrub Engine

- Peripherals

- 104 Configurable GPIO pins

- 3 UART interfaces

- 3 I<sup>2</sup>C interfaces

- 3 SPI interfaces

- 2 CAN 2.0B

- Ethernet MAC

- SpaceWire interface

- DMA controller

- 8-Ch 12-bit ADC

- 2-Ch 12-bit DAC

- Temperature sensor

- External Asynchronous Parallel Bus Interface (EBI)

- 8-bit or 16-bit memory support

- Four chip selects of up to 16 Mbytes each

- Timer System

- 24 configurable 32-bit counters / timers

- Input capture, Output compares

- PWMs, Pulse Counters, Watchdog timer

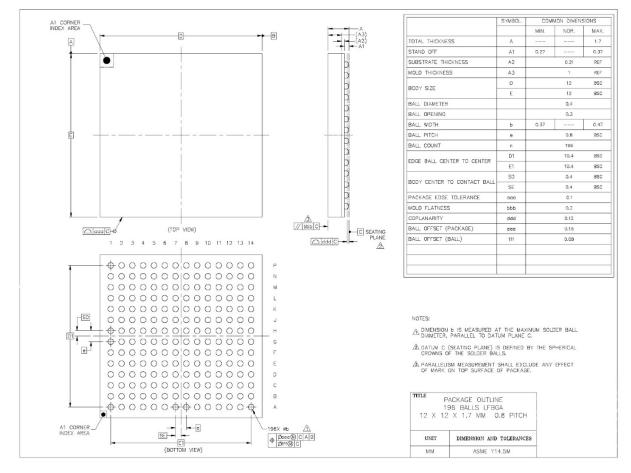

- Packages

- 196 BGA (12mm x 12mm)

- 176 QFP (20mm x 20mm)

#### SUPPORT

- PEB1 development board

- BSP and drivers

- See product errata in Section 12

- <sup>1</sup> Refer to Infineon-CYPT15B102Q-GGMB-Datasheet

- for FRAM radiation data.

### VORAGO CONFIDENTIAL

### **Product Datasheet**

| 1   | Functional Description                             | . 5 |

|-----|----------------------------------------------------|-----|

| 1.1 | Related Documentation                              | 5   |

| 1.2 | Feature Summary                                    | 5   |

| 1.3 | Boot Sequence                                      | 10  |

| 1.4 | Resets                                             | 10  |

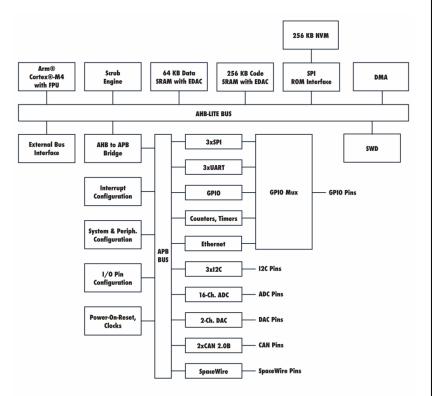

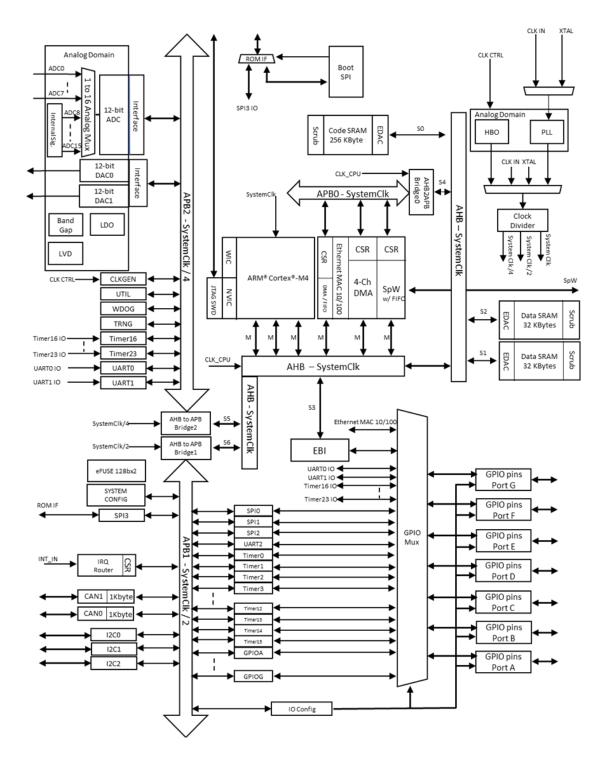

| 2   | Block Diagram                                      | 11  |

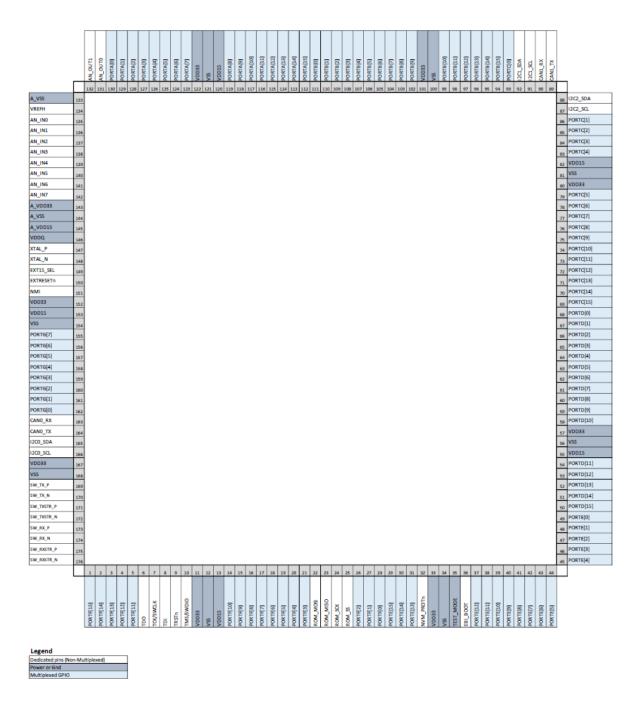

| 3   | Pinout                                             | 12  |

| 3.1 | 176-pin QFP pinout                                 | 12  |

| 3.2 | 196-Pin Plastic BGA Ball-Map Diagram               | 13  |

| 3.3 | 196-Pin Plastic BGA Ball Description               | 14  |

| 3.4 | Pin Descriptions                                   | 21  |

| 3.5 | GPIO Pin Alternative Functions                     | 24  |

| 4   | Peripheral Summary                                 | 28  |

| 4.1 | Serial Peripheral Interface (SPI)                  | 28  |

| 4.2 | Universal Asynchronous Receiver/Transmitter (UART) | 28  |

| 4.3 | Inter-Integrated Circuit (I <sup>2</sup> C)        | 29  |

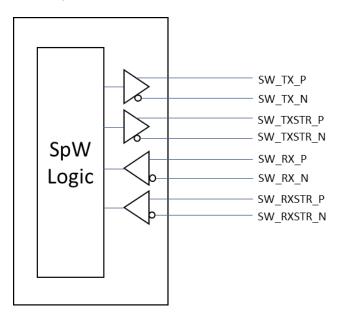

| 4.4 | SpaceWire (SpW)                                    | 30  |

| 4.5 | Controller Area Network (CAN)                      | 31  |

| 4.6 | General Purpose 4-Channel DMA                      | 32  |

| 4.7 | Ethernet Media Access Control (MAC)                | 32  |

| 4.8 | Analog to Digital Converter (ADC)                  | 34  |

| 4.9 | Digital to Analog Converter (DAC)                  | 34  |

| 4.1 |                                                    |     |

| 4.1 | 1 General-Purpose Input/Output Ports (GPIO)        | 35  |

| 4.1 |                                                    |     |

| 4.1 |                                                    |     |

| 4.1 | 4 Debug and programing interface                   | 37  |

| 5   | DC Electrical Characteristics                      | 39  |

| 5.1 | Absolute Maximum Ratings                           | 39  |

| 5.2 | Recommended Supply Conditions                      |     |

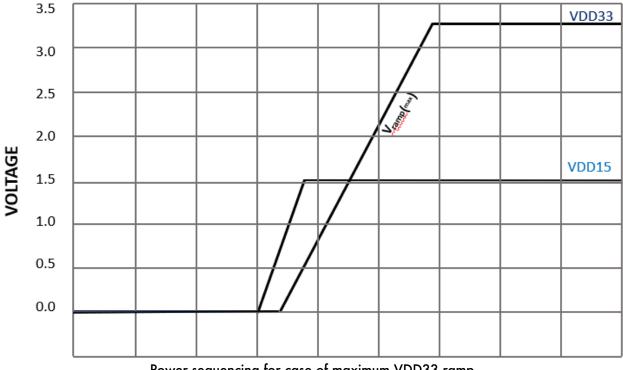

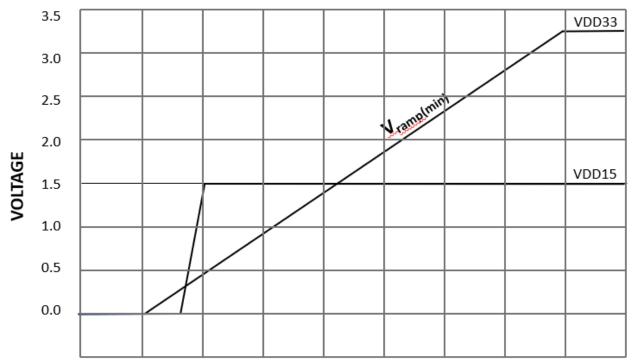

| 5.3 | Required Power Supply Sequencing                   | 40  |

| 5.4 | DC Current Consumption                             | 42  |

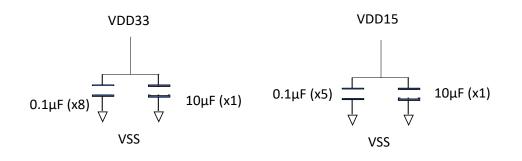

| 5.5 | Power Supply Decoupling                            |     |

| 5.6 | General Purpose I/O                                |     |

| 5.7 | Open Drain I2C Pads                                | 45  |

| 5.8 | SpaceWire Pads                                     |     |

| 5.9 | ADC Operating Conditions                           | 46  |

| 5.1 |                                                    |     |

| 5.1 |                                                    |     |

| 5.1 | •                                                  |     |

| 5.1 | •                                                  |     |

| 5.1 | 1 6                                                |     |

| 5.1 |                                                    |     |

| 5.1 | 5                                                  |     |

| 5.1 | 7 Internal Pull-up/Pull-down Resistors             | 50  |

#### **Product Datasheet**

|    | 5.18 | Pin Capacitance                           | 51 |

|----|------|-------------------------------------------|----|

| 6  |      | AC Electrical Characteristics             | 52 |

|    | 6.1  | AC Timing Conditions                      | 52 |

|    | 6.2  | Internal 20 MHz Oscillator                | 52 |

|    | 6.3  | Internal 1 MHz Oscillator                 | 52 |

|    | 6.4  | External Clock Signals                    | 52 |

|    | 6.5  | Phased Locked Loop (PLL)                  |    |

|    | 6.6  | Serial Wire Debug (SWD)                   | 54 |

|    | 6.7  | Low Voltage Differential Signaling (LVDS) | 55 |

|    | 6.8  | Ethernet MII Timing                       | 56 |

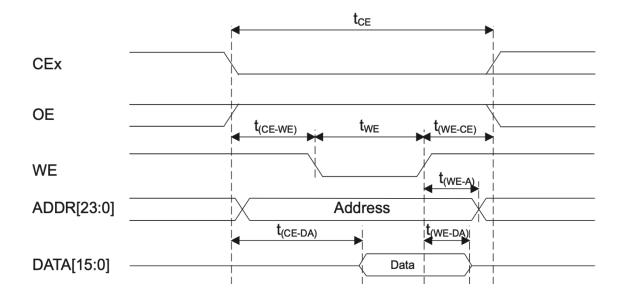

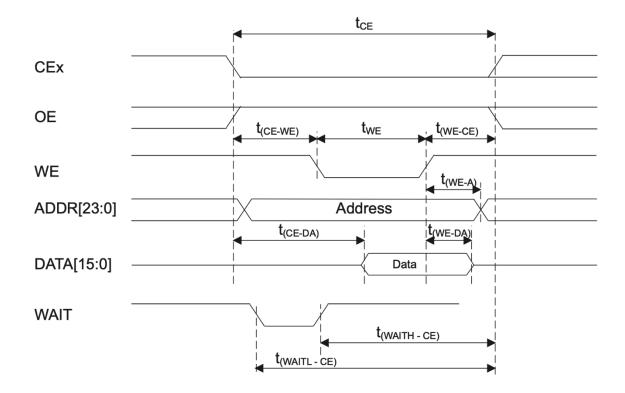

|    | 6.9  | External Bus Interface (EBI) Timing       | 57 |

|    | 6.10 | Electrostatic Discharge (ESD)             | 62 |

| 7  |      | Radiation Hardened Performance Targets    | 62 |

| 8  |      | Thermal Resistance Characteristics        | 62 |

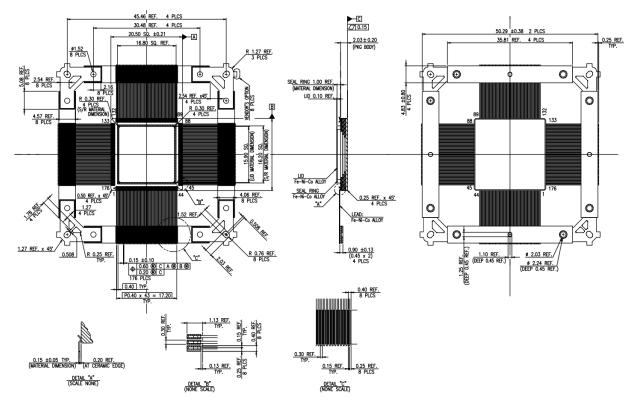

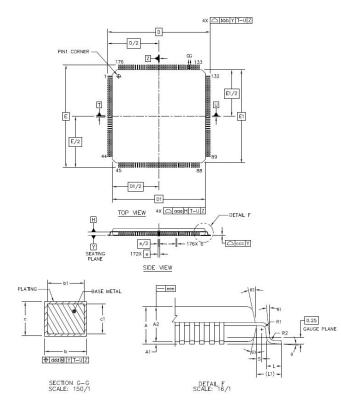

| 9  |      | Package Mechanical Information            | 64 |

|    | 9.1  | 176-Pin Ceramic QFP                       | 64 |

|    | 9.2  | 176-Pin Plastic QFP                       | 65 |

|    | 9.3  | 196-Pin Plastic BGA                       | 66 |

|    | 9.4  | Package Pin Metallization                 | 66 |

|    | 9.5  | Reflow / Soldering Conditions             | 66 |

| 1( | כ    | Ordering Information                      | 67 |

| 11 | L    | Development Kit Ordering Information      | 67 |

| 12 | 2    | VA416XX Errata                            |    |

| 13 | _    | Disclaimer                                |    |

| 14 | -    | Revision History                          |    |

|    | •    |                                           |    |

# Features

- Performance

- 100 MHz Arm<sup>®</sup> Cortex<sup>®</sup>-M4 processor with Single-Precision Floating-Point Unit (FPU)

- On-Chip Memory

- 256 Kbyte Non-Volatile Memory (Infineon FRAM) (VA41630 only)

- 256 Kbyte Program SRAM

- 64 Kbyte Data SRAM

- On-chip Error Detection and Correction (EDAC) and Scrub Engine

- General-purpose I/O (GPIO) pins

- Configurable direction

- Configurable pull-up/down resistors

- Configurable as edge or level sensitive interrupt sources

- 24 General-purpose counter/timers

- Configurable interrupt sources

- Can be triggered from multiple sources (GPIO or other counter/timers)

- Each counter/timer has an independent 32-bit counter

- Configurable as PWM, capture or compare

- 3 x UARTS

- Internal FIFO

- Transmit or receive interrupt source

- 3 x Serial Peripheral Interface (SPI) ports

- Internal FIFO

- Transmit or receive interrupt source

- Multiple chip select outputs

- 3 x l<sup>2</sup>C ports

- Internal FIFO

- Master and Slave mode on all ports

- Standard and Fast mode support

- System-level Triple-Mode Redundancy (TMR) on critical internal registers

- 8-Channel, 12-bit ADC

- 2-Channel, 12-bit DAC

- 2 x CAN 2.0B controllers

- Ethernet MAC

- SpaceWire controller with LVDS interface

- Random Number Generator

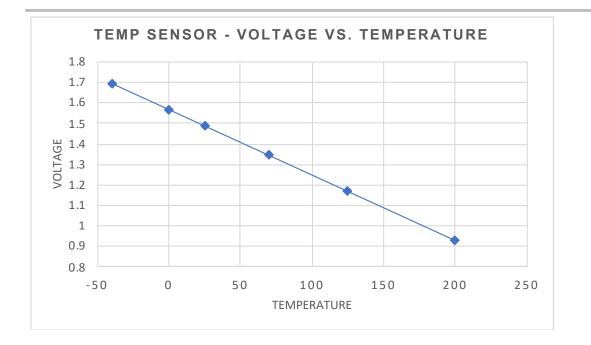

- Temperature sensor

- Serial Wire Debug (SWD) based debug controller (JTAG is for factory test only)

- Parallel external memory bus interface (EBI)

### 1 Functional Description

The VA416X0 is optimized for radiation environments and consists of an Arm<sup>®</sup> Cortex<sup>®</sup>-M4 CPU core and a related set of peripherals. It includes Error Detection and Correction (EDAC) logic on the internal memories. The program space EDAC is 16-bit word-based for optimum performance and reliability. The data space EDAC is 8-bit to allow reliable byte size data manipulation. In addition, the VA416X0 includes Triple-Mode Redundancy (TMR) with voting on select internal flip-flop storage elements.

#### 1.1 Related Documentation

The following associated documents will help understand this device:

- Arm<sup>®</sup> Documents (Available from <u>http://infocenter.arm.com</u>)

- Cortex<sup>®</sup>-M4 Generic User Guide

- Cortex<sup>®</sup>-M4 Technical Reference Manual

- AMBA<sup>®</sup> 3 AHB-Lite<sup>™</sup> Protocol Specification

- AMBA<sup>®</sup> 3 APB Protocol Specification

- Arm<sup>®</sup> TrustZone<sup>®</sup> True Random Number Generator Technical Reference Manual

- Arm<sup>®</sup> PrimeCell<sup>®</sup> External Bus Interface Technical Reference Manual

- Arm<sup>®</sup> PrimeCell<sup>®</sup> DMA Technical Reference Manual

- NXP Documents

- I<sup>2</sup>C-bus Specification

- Infineon Documents

- FM25V20A FRAM Datasheet

- VORAGO Documents

- VA416XX Programmer's Guide

#### 1.2 Feature Summary

- Processor Core

- Arm<sup>®</sup> Cortex<sup>®</sup>-M4 processor

- Up to 100 MHz operation

- SysTick Counter

- Single Cycle Multiply-and-accumulate

- Hardware divide (2 to 12 cycles)

- Single-precision IEEE 754 compliant HW Floating Point Unit (FPU)

- Bit-Banding region for registers and data SRAM

- Arm<sup>®</sup> Cortex<sup>®</sup>-M4 built-in Nested Vectored Interrupt Controller (NVIC)

- 240 Interrupt sources with a unique 3-bit priority level (176 of these are used)

- External Non-Maskable Interrupt (NMI) pin

- Tail chaining supported

- Arm<sup>®</sup> CoreSight<sup>™</sup> debug and trace technology

- SWD: Serial Wire Debug

- DAP: Debug Access Port

- Four Breakpoint Comparators

- Two Data Watch Point Comparators

- Memory

- 64 Kbyte SRAM Data Memory (32 Kbyte on Data bus and 32 Kbyte on System bus)

- Byte-level Error Detection and Correction (EDAC) logic on Data memory

- 256 Kbyte SRAM Instruction Memory

- Loaded from Serial Peripheral Interface (SPI) based memory or from external memory on the External Bus interface at startup

- Configurable boot delay, boot speed, and error checking

- 16-bit level EDAC on instruction memory

- Programmable Scrub Engine for both Data and Instruction memory

- Utility peripheral

- Provides means of injecting single and multi-bit errors to check error handling routines.

- 256 Kbyte serial FRAM in package (VA41630 only)

- System Integration Peripherals

- System Configuration

- Memory Control

- Data memory clear on reset

- Code memory reload on reset

- Code memory write protect

- Code/Data memory Scrub rate

- Code/Data memory SBE/MBE counters

- Code/Data memory SBE/MBE Interrupt control

- GPIO Glitch Filter rate control

- Peripheral Configuration

- Clock gating and Reset control of individual peripherals

- Interrupt Router

- Maps interrupt sources to timers, ADC, DAC, and DMA for flexible event triggers

- Four-Channel DMA

- Allows CPU independent data movement from memory to memory, peripherals to memory, or memory to peripherals.

- Analog Peripherals

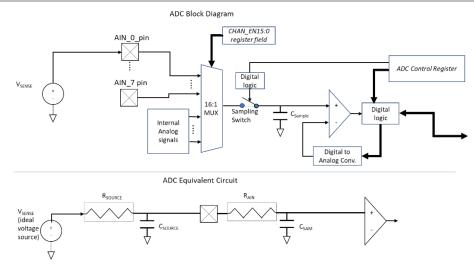

- 12-bit SAR ADC

- Eight channels on dedicated pins

- Internal temperature sensor connection

- 600 kps maximum sampling rate

- Triggerable by a timer event

- Digital to Analog Converter (DAC)

- Two independent channels on dedicated pins

- 12-bit resolution

- 0.5 mA drive capability

- DMA connection allows waveform generation

- Serial Communication Peripherals

- Three UARTs

- 16-word Transmit and Receive FIFOs

- Fractional baud rate generation

- Supports:

- 5, 6, 7, 8, and 9 bits

- Even, Odd and None parity

- Stop Bits 1 or 2

- Break generation and detection

- Error detection

- FIFO overflow

- Framing error

- Parity error

- Break detection

- Configurable Interrupt generation

- FIFO level (fully configurable)

- Receive Timeout

- Error

- Three SPI Ports (Fourth SPI used only to program Boot SPI FRAM)

- Supports all four modes of SPI operation

- Data size of 4 to 16 bits

- 16-word Transmit and Receive FIFOs

- Block mode support for larger Frame sizes

- Master-mode clock rates up to 1/4 System clock (3.125 Mbytes/s)

- Slave-mode clock rates up to 1/24 System clock (520 kbytes/s)

- Configurable Interrupt generation for transmitting and receiving

- FIFO level (fully configurable)

- FIFO Overflow

- Receive Timeout

- Three I<sup>2</sup>C Ports

- Standard I<sup>2</sup>C-compliant bus interface

- Dedicated open-drain pins supporting l<sup>2</sup>C Fast mode

- Configurable as Master or Slave

- 16-byte Transmit and Receive FIFOs

- Configurable Interrupt generation

- FIFO level (fully configurable)

- Ethernet Media Access Controller (MAC)

- Supports 10/100BASE-T

- Media-Independent interface (MII)

- Two Controller Area Network (CAN) Ports

- Supports CAN 2.0B

- Two-wire interface to external Physical Layer (PHY)

- SpaceWire port

- Supports SpaceWire standard ECSS-E-ST-50-12C

- 1k byte receive FIFO

- 1k byte transmit FIFO

- System Connection Peripherals

- o GPIO

- Seven GPIO Ports with up to 104 pins total

- 16-bit ports A-F

- 8-bit port G

- Configurable direction control of individual bits

- Bit-level mask register allows single instruction setting or clearing of any bits in one port.

- Configurable interrupt generation on ports A-F

- Level or Edge sensitive

- Configurable Pulse mode on individual bits

- Configurable (0 to 3) cycle delay filtering on individual bits

- I/O Configuration

- Manages programmable function selects of each pin to allow peripherals to be mapped to GPIO

- Sets electrical parameters:

- Glitch filters

- Pull-up/Pull-down resistors

- Signal inversion

- Pseudo open-drain

- Timers

- Twenty-four 32-bit timers

- Advanced trigger modes using cascade feature

- Separate Start/Stop based on other timers or interrupt signals

- Multiple trigger sources from GPIO or other timers

- Configurable output event

- One cycle pulse when timer equal to zero detected

- Active mode

- Divide by two for square wave creation

- Two PWM modes: single edge and double edge detection (supports center alignment)

- External Bus interface

- Asynchronous with 16-bit or 8-bit data width

- Double mapped in memory to allow Instruction or Data access

- 16 Mbyte memory space with four chip selects

- Configurable wait states

- Power supplies

- Configured for use with dual supplies

- 3.3 V for I/O

- 1.5 V for logic

- Radiation Hardness

- Latch-up immunity in extreme environments

- Built to be resistant to Single Event Upsets (SEU)

- Built with VORAGO proprietary HARDSIL<sup>®</sup> technology

- Designed with Dual-Interlocked Storage Cells (DICE) and Triple-Mode Redundancy (TMR) on key register elements.

#### **1.3 Boot Sequence**

The VA416XX can boot from one of two sources: an internal/external Serial Peripheral Interface (SPI) peripheral connected to the ROM SPI interface or via the External Parallel Bus Interface (EBI). The boot mode is selected with the EBI\_BOOT pin. The clock source for boot operation is a 20 MHz internally generated oscillator (HBO)

If EBI\_BOOT=0, The VA416X0 begins operation by loading the internal SRAM code memory from an SPI memory (internal/external) via a connected Serial Peripheral Interface (SPI)

If EBI\_BOOT=1, The VA416X0 will load the internal code memory from an external memory device via the External Bus Interface.

After loading the code memory, the processor follows a typical Arm<sup>®</sup> Cortex<sup>®</sup>-M4 start sequence.

#### 1.4 Resets

In addition to the Power-on reset, the device can be reset from other events:

- EXTRESETn pin

- SYSRESETREQ from software

- Hardware events configured by IRQ Selector Peripheral or the System Controller Peripheral:

- Watchdog Timer

- Memory Errors (Single or Multi-bit errors from the EDAC memory controller)

# 2 Block Diagram

**Product Datasheet**

#### 3 Pinout

The VA416X0 is available in a choice of packages: 176-pin plastic QFP, 176-pin ceramic QFP, and 196-pin plastic BGA.

### 3.1 176-pin QFP pinout

# 3.2 196-Pin Plastic BGA Ball-Map Diagram

|   | 1    | 2    | 3     | 4    | 5     | 6    | 7    | 8    | 9    | 10    | 11    | 12   | 13   | 14    |

|---|------|------|-------|------|-------|------|------|------|------|-------|-------|------|------|-------|

| A | PF15 | NC   | SRXSN | SRXN | STXSN | STXN | SDA0 | PG01 | PG05 | NC    | XTALp | AN7  | AN3  | VREFH |

| В | PF11 | PF14 | SRXSP | SRXP | STXSP | SCL0 | PG00 | PG04 | NMI  | XTALn | A3V3  | AN4  | AN0  | DAC0  |

| С | TRST | TDO  | PF13  | STXP | 3V3   | CRXO | PG03 | PG07 | E1V5 | A1V5  | AN5   | AN1  | DAC1 | ATOUT |

| D | PF08 | TMS  | тск   | PF12 | CTX0  | PG02 | PG06 | RSTn | VDDQ | AN6   | AN2   | PA03 | PA01 | PA00  |

| E | PF04 | PF07 | PF10  | TDI  | 1V5   | VSS  | 3V3  | 1V5  | VSS  | 3V3   | PA09  | PA06 | PA04 | PA02  |

| F | SCK  | PF03 | PF06  | PF09 | VSS   | VSS  | 3V3  | 1V5  | VSS  | VSS   | PA13  | PA10 | PA07 | PA05  |

| G | PF01 | CSn  | MOSI  | PF05 | 1V5   | 1V5  | VSS  | VSS  | 3V3  | 3V3   | PB01  | PA14 | PA11 | PA08  |

| н | PE13 | PF00 | F_SO  | MISO | 3V3   | 3V3  | VSS  | VSS  | 1V5  | 1V5   | PB04  | NC   | PA15 | PA12  |

| J | EBI  | WPn  | PE15  | PF02 | VSS   | VSS  | 1V5  | 3V3  | VSS  | VSS   | PB08  | PB05 | PB02 | PB00  |

| К | PE10 | PE12 | TEST  | PE14 | 3V3   | VSS  | 1V5  | 3V3  | VSS  | 1V5   | PB12  | PB09 | PB06 | PB03  |

| L | PE08 | PE09 | PE11  | PE01 | PD13  | PD09 | PD05 | PD01 | PC13 | PC10  | PC00  | PB13 | PB10 | PB07  |

| Μ | PE06 | PE07 | PE02  | PD14 | PD10  | PD06 | PD02 | PC14 | NC   | PC07  | PC04  | SDA1 | PB14 | PB11  |

| Ν | PE05 | PE03 | PD15  | PD11 | PD07  | PD03 | PC15 | PC11 | PC08 | PC05  | PC02  | SCL2 | SCL1 | PB15  |

| Ρ | PE04 | PE00 | PD12  | PD08 | PD04  | PD00 | PC12 | PC09 | PC06 | PC03  | PC01  | SDA2 | CTX1 | CRX1  |

# 3.3 196-Pin Plastic BGA Ball Description

| MASTER<br>196B PBGA<br>BALL NUMBER | VA416x0<br>1968 PBGA<br>BALL NAME | VA416x0 Description                                                                                                                      |  |  |

|------------------------------------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| A01                                | PF15                              | PORTF[15] Software configurable general-purpose I/O. Software configurable for direction, interrupt sources, and counter/timer triggers. |  |  |

| A02                                | NC                                | No connect                                                                                                                               |  |  |

| A03                                | SRXSN                             | SpaceWire Rx strobe -                                                                                                                    |  |  |

| A04                                | SRXN                              | SpaceWire Rx -                                                                                                                           |  |  |

| A05                                | STXSN                             | SpaceWire Tx strobe -                                                                                                                    |  |  |

| A06                                | STXN                              | SpaceWire Tx -                                                                                                                           |  |  |

| A07                                | SDA0                              | I <sup>2</sup> C0 Data                                                                                                                   |  |  |

| A08                                | PG01                              | PORTG[1] Software configurable general-purpose I/O. Software configurable for direction, interrupt sources, and counter/timer triggers.  |  |  |

| A09                                | PG05                              | PORTG[5] Software configurable general-purpose I/O. Software configurable for direction, interrupt sources, and counter/timer triggers.  |  |  |

| A10                                | NC                                | No connect                                                                                                                               |  |  |

| A11                                | XTALp                             | Crystal Oscillator Output                                                                                                                |  |  |

| A12                                | AN7                               | Analog input channel 7                                                                                                                   |  |  |

| A13                                | AN3                               | Analog input channel 3                                                                                                                   |  |  |

| A14                                | VREFH                             | Analog Reference (3.3 V)                                                                                                                 |  |  |

| BO1                                | PF11                              | PORTF[11] Software configurable general-purpose I/O. Software configurable for direction, interrupt sources, and counter/timer triggers. |  |  |

| B02                                | PF14                              | PORTF[14] Software configurable general-purpose I/O. Software configurable for direction, interrupt sources, and counter/timer triggers. |  |  |

| B03                                | SRXSP                             | SpaceWire Rx strobe +                                                                                                                    |  |  |

| B04                                | SRXP                              | SpaceWire Rx +                                                                                                                           |  |  |

| B05                                | STXSP                             | SpaceWire Tx strobe +                                                                                                                    |  |  |

| B06                                | SCL0                              | I <sup>2</sup> C0 Clock                                                                                                                  |  |  |

| B07                                | PG00                              | PORTG[0] Software configurable general-purpose I/O. Software configurable for direction, interrupt sources, and counter/timer triggers.  |  |  |

| B08                                | PG04                              | PORTG[4] Software configurable general-purpose I/O. Software configurable for direction, interrupt sources, and counter/timer triggers.  |  |  |

| B09                                | NMI                               | Non-maskable Interrupt – active high                                                                                                     |  |  |

| B10                                | XTALn                             | Crystal Oscillator Input                                                                                                                 |  |  |

| B11                                | A3V3                              | 3.3 V Analog IO power                                                                                                                    |  |  |

| B12      | AN4    | Analog input channel 4                                                                                                                                                                |

|----------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B13      | AN0    | Analog input channel 0                                                                                                                                                                |

|          |        |                                                                                                                                                                                       |

| B14      | DAC0   | Digital to analog output 0                                                                                                                                                            |

| C01      | TRST   | Test Reset, active low                                                                                                                                                                |

| C02      | TDO    | Test Data Out                                                                                                                                                                         |

| C03      | PF13   | PORTF[13] Software configurable general-purpose I/O. Software configurable for direction, interrupt sources, and counter/timer triggers.                                              |

| C04      | STXP   | SpaceWire Tx +                                                                                                                                                                        |

| C05      | 3V3    | 3.3 V power                                                                                                                                                                           |

| C06      | CRX0   | CANO RX                                                                                                                                                                               |

| C07      | PG03   | PORTG[3] Software configurable general-purpose I/O. Software configurable for direction, interrupt sources, and counter/timer triggers.                                               |

| C08      | PG07   | PORTG[7] Software configurable general-purpose I/O. Software                                                                                                                          |

|          |        | configurable for direction, interrupt sources, and counter/timer triggers.                                                                                                            |

| C09      | E1V5   | When high, this signal disables the internal 1.5 V regulator, and 1.5 V must                                                                                                          |

| <u> </u> | A 11/5 | be applied externally to all 1V5 pins and A1V5.                                                                                                                                       |

| C10      | A1V5   | 1.5 V Analog power (must be supplied externally if EXT15_SEL=1)                                                                                                                       |

| C11      | AN5    | Analog input channel 5                                                                                                                                                                |

| C12      | AN1    | Analog input channel 1                                                                                                                                                                |

| C13      | DAC1   | Digital to analog output 1                                                                                                                                                            |

| C14      | ATOUT  | For factory use only. Must be pulled to VSS                                                                                                                                           |

| D01      | PF08   | PORTF[8] Software configurable general-purpose I/O. Software configurable for direction, interrupt sources, and counter/timer triggers.                                               |

| D02      | TMS    | Test Mode Select/Serial Wire Debug Data IO                                                                                                                                            |

| D03      | ТСК    | Test Clock/Serial Wire Debug Clock                                                                                                                                                    |

| 005      |        |                                                                                                                                                                                       |

| D04      | PF12   | PORTF[12] Software configurable general-purpose I/O. Software configurable for direction, interrupt sources, and counter/timer triggers.                                              |

| D05      | CTX0   | CANO TX                                                                                                                                                                               |

| D06      | PG02   | PORTG[2] Software configurable general-purpose I/O. Software configurable for direction, interrupt sources, and counter/timer triggers.                                               |

| D07      | PG06   | PORTG[6] Software configurable general-purpose I/O. Software                                                                                                                          |

|          |        | configurable for direction, interrupt sources, and counter/timer triggers.                                                                                                            |

| D08      | RSTn   | External System Reset, active low. Resets the processor and all peripherals.<br>Any reset will cause this pin to drive low during the reset sequence. (Must<br>have external pull-up) |

| D09      | VDDQ   | For factory use only. Must be tied to VSS                                                                                                                                             |

| D10      | AN6    | Analog input channel 6                                                                                                                                                                |

| D11      | AN2    | Analog input channel 2                                                                                                                                                                |

| D12 | PA03 | PORTA[3] Software configurable general-purpose I/O. Software                                                                                   |  |  |  |

|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| D13 | PA01 | configurable for direction, interrupt sources, and counter/timer triggers.        PORTA[1] Software configurable general-purpose I/O. Software |  |  |  |

| 013 | FAUT | configurable for direction, interrupt sources, and counter/timer triggers.                                                                     |  |  |  |

| D14 | PA00 | PORTA[0] Software configurable general-purpose I/O. Software                                                                                   |  |  |  |

| 014 | FAUU | configurable for direction, interrupt sources, and counter/timer triggers.                                                                     |  |  |  |

| E01 | PF04 | PORTF[4] Software configurable general-purpose I/O. Software                                                                                   |  |  |  |

| EUT | FF04 | configurable for direction, interrupt sources, and counter/timer triggers.                                                                     |  |  |  |

| E02 | PF07 | PORTF[7] Software configurable general-purpose I/O. Software                                                                                   |  |  |  |

|     | 1107 | configurable for direction, interrupt sources, and counter/timer triggers.                                                                     |  |  |  |

| E03 | PF10 | PORTF[10] Software configurable general-purpose I/O. Software                                                                                  |  |  |  |

| 203 | FIIV | configurable for direction, interrupt sources, and counter/timer triggers.                                                                     |  |  |  |

| E04 | TDI  | Test Data In                                                                                                                                   |  |  |  |

| 204 |      |                                                                                                                                                |  |  |  |

| E05 | 1V5  | 1.5 V power (must be supplied externally if EXT15_SEL=1)                                                                                       |  |  |  |

| E06 | VSS  | Ground                                                                                                                                         |  |  |  |

| EU0 | \$33 | Ground                                                                                                                                         |  |  |  |

| E07 | 3V3  | 3.3 V power                                                                                                                                    |  |  |  |

| E08 | 1V5  | 1.5 V power (must be supplied externally if EXT15_SEL=1)                                                                                       |  |  |  |

| E09 | VSS  | Ground                                                                                                                                         |  |  |  |

| E10 | 3V3  | 3.3 V power                                                                                                                                    |  |  |  |

| E11 | PA09 | PORTA[9] Software configurable general-purpose I/O. Software                                                                                   |  |  |  |

|     |      | configurable for direction, interrupt sources, and counter/timer triggers.                                                                     |  |  |  |

| E12 | PA06 | PORTA[6] Software configurable general-purpose I/O. Software                                                                                   |  |  |  |

|     |      | configurable for direction, interrupt sources, and counter/timer triggers.                                                                     |  |  |  |

| E13 | PA04 | PORTA[4] Software configurable general-purpose I/O. Software                                                                                   |  |  |  |

|     |      | configurable for direction, interrupt sources, and counter/timer triggers.                                                                     |  |  |  |

| E14 | PA02 | PORTA[2] Software configurable general-purpose I/O. Software                                                                                   |  |  |  |

|     |      | configurable for direction, interrupt sources, and counter/timer triggers.                                                                     |  |  |  |

| F01 | SCK  | SPI Clock to Boot ROM.                                                                                                                         |  |  |  |

| 500 | DEOD |                                                                                                                                                |  |  |  |

| F02 | PF03 | PORTF[3] Software configurable general-purpose I/O. Software                                                                                   |  |  |  |

| F03 | PF06 | configurable for direction, interrupt sources, and counter/timer triggers.        PORTF[6] Software configurable general-purpose I/O. Software |  |  |  |

| 103 | FFUO | configurable for direction, interrupt sources, and counter/timer triggers.                                                                     |  |  |  |

| F04 | PF09 | PORTF[9] Software configurable general-purpose I/O. Software                                                                                   |  |  |  |

| F04 | FFU7 | configurable for direction, interrupt sources, and counter/timer triggers.                                                                     |  |  |  |

| F05 | VSS  | Ground                                                                                                                                         |  |  |  |

| 105 | *33  | Cround                                                                                                                                         |  |  |  |

| F06 | VSS  | Ground                                                                                                                                         |  |  |  |

| F07 | 3V3  | 3.3 V power                                                                                                                                    |  |  |  |

| F08 | 1V5  | 1.5 V power (must be supplied externally if EXT15_SEL=1)                                                                                       |  |  |  |

| F09 | VSS  | Ground                                                                                                                                         |  |  |  |

| E10 | 1/66 | Ground                                                                                                                                         |  |  |  |

| F10 | VSS  | Ground                                                                                                                                         |  |  |  |

| F11 | PA13 | PORTA[13] Software configurable general-purpose I/O. Software configurable for direction, interrupt sources, and counter/timer triggers.       |  |  |  |

| F12  | PA10  | PORTA[10] Software configurable general-purpose I/O. Software configurable for direction, interrupt sources, and counter/timer triggers. |  |

|------|-------|------------------------------------------------------------------------------------------------------------------------------------------|--|

| F13  | PA07  | PORTA[7] Software configurable general-purpose I/O. Software                                                                             |  |

|      |       | configurable for direction, interrupt sources, and counter/timer triggers.                                                               |  |

| F14  | PA05  | PORTA[5] Software configurable general-purpose I/O. Software                                                                             |  |

|      |       | configurable for direction, interrupt sources, and counter/timer triggers.                                                               |  |

| G01  | PF01  | PORTF[1] Software configurable general-purpose I/O. Software                                                                             |  |

| 001  |       | configurable for direction, interrupt sources, and counter/timer triggers.                                                               |  |

| G02  | CSn   | SPI Chip Select to Boot ROM (Active Low).                                                                                                |  |

| 002  | Con   |                                                                                                                                          |  |

| G03  | MOSI  | SPI Data Out to Boot ROM.                                                                                                                |  |

| G04  | PF05  | PORTF[5] Software configurable general-purpose I/O. Software                                                                             |  |

| 004  |       | configurable for direction, interrupt sources, and counter/timer triggers.                                                               |  |

| G05  | 1V5   | 1.5 V power (must be supplied externally if EXT15_SEL=1)                                                                                 |  |

| 005  | 145   | 1.5 V power (most be supplied externally if EXTIS_SEE T)                                                                                 |  |

| G06  | 1V5   | 1.5 V power (must be supplied externally if EXT15_SEL=1)                                                                                 |  |

| G07  | VSS   | Ground                                                                                                                                   |  |

|      |       |                                                                                                                                          |  |

| G08  | VSS   | Ground                                                                                                                                   |  |

| G09  | 3V3   | 3.3 V power                                                                                                                              |  |

|      | 0,0   |                                                                                                                                          |  |

| G10  | 3V3   | 3.3 V power                                                                                                                              |  |

| G11  | PBO1  | PORTB[1] Software configurable general-purpose I/O. Software                                                                             |  |

| •••• |       | configurable for direction, interrupt sources, and counter/timer triggers.                                                               |  |

| G12  | PA14  | PORTA[14] Software configurable general-purpose I/O. Software                                                                            |  |

| 0.2  |       | configurable for direction, interrupt sources, and counter/timer triggers.                                                               |  |

| G13  | PA11  | PORTA[11] Software configurable general-purpose I/O. Software                                                                            |  |

| 010  |       | configurable for direction, interrupt sources, and counter/timer triggers.                                                               |  |

| G14  | PA08  | PORTA[8] Software configurable general-purpose I/O. Software                                                                             |  |

| 014  | 1,400 |                                                                                                                                          |  |

| 1101 | DE10  | configurable for direction, interrupt sources, and counter/timer triggers.                                                               |  |

| H01  | PE13  | PORTE[13] Software configurable general-purpose I/O. Software                                                                            |  |

|      |       | configurable for direction, interrupt sources, and counter/timer triggers.                                                               |  |

| H02  | PFOO  | PORTF[0] Software configurable general-purpose I/O. Software                                                                             |  |

|      |       | configurable for direction, interrupt sources, and counter/timer triggers.                                                               |  |

| H03  | F_SO  | SPI Data In from Boot ROM. Must be connected to H04                                                                                      |  |

| H04  | MISO  | SPI Data In from Boot ROM. Must be connected to H03                                                                                      |  |

| H05  | 3V3   | 3.3 V power                                                                                                                              |  |

| 1107 | 0)/0  |                                                                                                                                          |  |

| H06  | 3V3   | 3.3 V power                                                                                                                              |  |

| H07  | VSS   | Ground                                                                                                                                   |  |

| H08  | VSS   | Ground                                                                                                                                   |  |

| H09  | 1V5   | 1.5 V power (must be supplied externally if EXT15_SEL=1)                                                                                 |  |

| H10  | 1V5   | 1.5 V power (must be supplied externally if EXT15_SEL=1)                                                                                 |  |

| H11  | PB04  | PORTB[4] Software configurable general-purpose I/O. Software                                                                             |  |

|      | rdV4  | configurable for direction, interrupt sources, and counter/timer triggers.                                                               |  |

### **Product Datasheet**

| H12 | NC   | No connect                                                                                                                               |  |

|-----|------|------------------------------------------------------------------------------------------------------------------------------------------|--|

| H13 | PA15 | PORTA[15] Software configurable general-purpose I/O. Software configurable for direction, interrupt sources, and counter/timer triggers. |  |

| H14 | PA12 | PORTA[12] Software configurable general-purpose I/O. Software configurable for direction, interrupt sources, and counter/timer triggers. |  |

| J01 | EBI  | Expanded Bus Boot Mode                                                                                                                   |  |

| J02 | WPn  | Nonvolatile memory write protection                                                                                                      |  |

| J03 | PE15 | PORTE[15] Software configurable general-purpose I/O. Software configurable for direction, interrupt sources, and counter/timer triggers. |  |

| J04 | PF02 | PORTF[2] Software configurable general-purpose I/O. Software configurable for direction, interrupt sources, and counter/timer triggers.  |  |

| J05 | VSS  | Ground                                                                                                                                   |  |

| J06 | VSS  | Ground                                                                                                                                   |  |

| J07 | 1V5  | 1.5 V power (must be supplied externally if EXT15_SEL=1)                                                                                 |  |

| 108 | 3V3  | 3.3 V power                                                                                                                              |  |

| J09 | VSS  | Ground                                                                                                                                   |  |

| J10 | VSS  | Ground                                                                                                                                   |  |

| J11 | PB08 | PORTB[8] Software configurable general-purpose I/O. Software configurable for direction, interrupt sources, and counter/timer triggers.  |  |

| J12 | PB05 | PORTB[5] Software configurable general-purpose I/O. Software configurable for direction, interrupt sources, and counter/timer triggers.  |  |

| J13 | PB02 | PORTB[2] Software configurable general-purpose I/O. Software configurable for direction, interrupt sources, and counter/timer triggers.  |  |

| J14 | РВОО | PORTB[0] Software configurable general-purpose I/O. Software configurable for direction, interrupt sources, and counter/timer triggers.  |  |

| K01 | PE10 | PORTE[10] Software configurable general-purpose I/O. Software configurable for direction, interrupt sources, and counter/timer triggers. |  |

| K02 | PE12 | PORTE[12] Software configurable general-purpose I/O. Software configurable for direction, interrupt sources, and counter/timer triggers. |  |

| K03 | TEST | For factory use only. Must be tied to ground with a 10k resistor.                                                                        |  |

| K04 | PE14 | PORTE[14] Software configurable general-purpose I/O. Software configurable for direction, interrupt sources, and counter/timer triggers. |  |

| K05 | 3V3  | 3.3 V power                                                                                                                              |  |

| K06 | VSS  | Ground                                                                                                                                   |  |

| K07 | 1V5  | 1.5 V power (must be supplied externally if EXT15_SEL=1)                                                                                 |  |

| K08 | 3V3  | 3.3 V power                                                                                                                              |  |

| К09 | VSS  | Ground                                                                                                                                   |  |

| К10 | 1V5  | 1.5 V power (must be supplied externally if EXT15_SEL=1)                                                                                 |  |

| K11 | PB12 | PORTB[12] Software configurable general-purpose I/O. Software configurable for direction, interrupt sources, and counter/timer triggers. |  |

| K12   | PB09     | PORTB[9] Software configurable general-purpose I/O. Software               |

|-------|----------|----------------------------------------------------------------------------|

|       |          | configurable for direction, interrupt sources, and counter/timer triggers. |

| K13   | PB06     | PORTB[6] Software configurable general-purpose I/O. Software               |

|       |          | configurable for direction, interrupt sources, and counter/timer triggers. |

| K14   | PB03     | PORTB[3] Software configurable general-purpose I/O. Software               |

|       |          | configurable for direction, interrupt sources, and counter/timer triggers. |

| L01   | PE08     | PORTE[8] Software configurable general-purpose I/O. Software               |

|       |          | configurable for direction, interrupt sources, and counter/timer triggers. |

| L02   | PE09     | PORTE[9] Software configurable general-purpose I/O. Software               |

|       |          | configurable for direction, interrupt sources, and counter/timer triggers. |

| L03   | PE11     | PORTE[11] Software configurable general-purpose I/O. Software              |

| 200   |          | configurable for direction, interrupt sources, and counter/timer triggers. |

| L04   | PE01     | PORTE[1] Software configurable general-purpose I/O. Software               |

| 104   | 1201     | configurable for direction, interrupt sources, and counter/timer triggers. |

| 105   | PD13     |                                                                            |

| L05   | PDI3     | PORTD[13] Software configurable general-purpose I/O. Software              |

|       |          | configurable for direction, interrupt sources, and counter/timer triggers. |

| L06   | PD09     | PORTD[9] Software configurable general-purpose I/O. Software               |

|       |          | configurable for direction, interrupt sources, and counter/timer triggers. |

| L07   | PD05     | PORTD[5] Software configurable general-purpose I/O. Software               |

|       |          | configurable for direction, interrupt sources, and counter/timer triggers. |

| L08   | PD01     | PORTD[1] Software configurable general-purpose I/O. Software               |

|       |          | configurable for direction, interrupt sources, and counter/timer triggers. |

| L09   | PC13     | PORTC[13] Software configurable general-purpose I/O. Software              |

|       |          | configurable for direction, interrupt sources, and counter/timer triggers. |

| L10   | PC10     | PORTC[10] Software configurable general-purpose I/O. Software              |

|       |          | configurable for direction, interrupt sources, and counter/timer triggers. |

| L11   | PC00     | PORTC[0] Software configurable general-purpose I/O. Software               |

|       |          | configurable for direction, interrupt sources, and counter/timer triggers. |

| L12   |          |                                                                            |

|       |          | configurable for direction, interrupt sources, and counter/timer triggers. |

| L13   | PB10     | PORTB[10] Software configurable general-purpose I/O. Software              |

| 210   | 1510     | configurable for direction, interrupt sources, and counter/timer triggers. |

| L14   | PB07     | PORTB[7] Software configurable general-purpose I/O. Software               |

| L14   | FD07     |                                                                            |

| 1101  |          | configurable for direction, interrupt sources, and counter/timer triggers. |

| M01   | PE06     | PORTE[6] Software configurable general-purpose I/O. Software               |

|       |          | configurable for direction, interrupt sources, and counter/timer triggers. |

| M02   | PE07     | PORTE[7] Software configurable general-purpose I/O. Software               |

|       |          | configurable for direction, interrupt sources, and counter/timer triggers. |

| M03   | PE02     | PORTE[2] Software configurable general-purpose I/O. Software               |

|       |          | configurable for direction, interrupt sources, and counter/timer triggers. |

| M04   | PD14     | PORTD[14] Software configurable general-purpose I/O. Software              |

|       |          | configurable for direction, interrupt sources, and counter/timer triggers. |

| M05   | PD10     | PORTD[10] Software configurable general-purpose I/O. Software              |

|       |          | configurable for direction, interrupt sources, and counter/timer triggers. |

| M06   | PD06     | PORTD[6] Software configurable general-purpose I/O. Software               |

|       |          | configurable for direction, interrupt sources, and counter/timer triggers. |

| M07   | PD02     | PORTD[2] Software configurable general-purpose I/O. Software               |

|       | <b>-</b> | configurable for direction, interrupt sources, and counter/timer triggers. |

| M08   | PC14     | PORTC[14] Software configurable general-purpose I/O. Software              |

|       | 1014     | configurable for direction, interrupt sources, and counter/timer triggers. |

| M09   | NC       | No connect                                                                 |

| 11117 |          |                                                                            |

| M10  | PC07   | PORTC[7] Software configurable general-purpose I/O. Software                                                                            |

|------|--------|-----------------------------------------------------------------------------------------------------------------------------------------|

|      |        | configurable for direction, interrupt sources, and counter/timer triggers.                                                              |

| M11  | PC04   | PORTC[4] Software configurable general-purpose I/O. Software                                                                            |

|      |        | configurable for direction, interrupt sources, and counter/timer triggers.                                                              |

| M12  | SDA1   | l <sup>2</sup> C1 Data                                                                                                                  |

| M13  | PB14   | PORTB[14] Software configurable general-purpose I/O. Software                                                                           |

|      |        | configurable for direction, interrupt sources, and counter/timer triggers.                                                              |

| M14  | PB11   | PORTB[11] Software configurable general-purpose I/O. Software                                                                           |

|      |        | configurable for direction, interrupt sources, and counter/timer triggers.                                                              |

| N01  | PE05   | PORTE[5] Software configurable general-purpose I/O. Software                                                                            |

|      |        | configurable for direction, interrupt sources, and counter/timer triggers.                                                              |

| N02  | PE03   | PORTE[3] Software configurable general-purpose I/O. Software                                                                            |

|      |        | configurable for direction, interrupt sources, and counter/timer triggers.                                                              |

| N03  | PD15   | PORTD[15] Software configurable general-purpose I/O. Software                                                                           |

|      | -      | configurable for direction, interrupt sources, and counter/timer triggers.                                                              |

| N04  | PD11   | PORTD[11] Software configurable general-purpose I/O. Software                                                                           |

|      |        | configurable for direction, interrupt sources, and counter/timer triggers.                                                              |

| N05  | PD07   | PORTD[7] Software configurable general-purpose I/O. Software                                                                            |

| 1105 | 100/   | configurable for direction, interrupt sources, and counter/timer triggers.                                                              |

| N06  | PD03   | PORTD[3] Software configurable general-purpose I/O. Software                                                                            |

| 1100 | 1000   | configurable for direction, interrupt sources, and counter/timer triggers.                                                              |

| N07  | PC15   | PORTC[15] Software configurable general-purpose I/O. Software                                                                           |

| 1407 | r CI J | configurable for direction, interrupt sources, and counter/timer triggers.                                                              |

| N08  | PC11   | PORTC[11] Software configurable general-purpose I/O. Software                                                                           |

| INUO | ren    |                                                                                                                                         |

| N09  | PC08   | configurable for direction, interrupt sources, and counter/timer triggers.                                                              |

| 1109 | PC00   | PORTC[8] Software configurable general-purpose I/O. Software                                                                            |

| N10  | DCOF   | configurable for direction, interrupt sources, and counter/timer triggers.                                                              |

| NIU  | PC05   | PORTC[5] Software configurable general-purpose I/O. Software configurable for direction, interrupt sources, and counter/timer triggers. |

| N11  | PC02   | PORTC[2] Software configurable general-purpose I/O. Software                                                                            |

|      | PCUZ   |                                                                                                                                         |

| N110 | 6610   | configurable for direction, interrupt sources, and counter/timer triggers.                                                              |

| N12  | SCL2   | I <sup>2</sup> C2 Clock                                                                                                                 |

| N13  | SCL1   | I²C1 Clock                                                                                                                              |

|      |        |                                                                                                                                         |

| N14  | PB15   | PORTB[15] Software configurable general-purpose I/O. Software                                                                           |

|      |        | configurable for direction, interrupt sources, and counter/timer triggers.                                                              |

| P01  | PEO4   | PORTE[4] Software configurable general-purpose I/O. Software                                                                            |

|      |        | configurable for direction, interrupt sources, and counter/timer triggers.                                                              |

| P02  | PEOO   | PORTE[0] Software configurable general-purpose I/O. Software                                                                            |

|      |        | configurable for direction, interrupt sources, and counter/timer triggers.                                                              |

| P03  | PD12   | PORTD[12] Software configurable general-purpose I/O. Software                                                                           |

|      |        | configurable for direction, interrupt sources, and counter/timer triggers.                                                              |

| P04  | PD08   | PORTD[8] Software configurable general-purpose I/O. Software                                                                            |

|      |        | configurable for direction, interrupt sources, and counter/timer triggers.                                                              |

| P05  | PD04   | PORTD[4] Software configurable general-purpose I/O. Software                                                                            |

|      |        | configurable for direction, interrupt sources, and counter/timer triggers.                                                              |

| P06  | PD00   | PORTD[0] Software configurable general-purpose I/O. Software                                                                            |

|      |        | configurable for direction, interrupt sources, and counter/timer triggers.                                                              |

| P07  | PC12   | PORTC[12] Software configurable general-purpose I/O. Software                                                                           |

|      |        | configurable for direction, interrupt sources, and counter/timer triggers.                                                              |

|      | 1      |                                                                                                                                         |

| P08 | PC09 | PORTC[9] Software configurable general-purpose I/O. Software configurable for direction, interrupt sources, and counter/timer triggers. |

|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------|

| P09 | PC06 | PORTC[6] Software configurable general-purpose I/O. Software configurable for direction, interrupt sources, and counter/timer triggers. |

| P10 | PC03 | PORTC[3] Software configurable general-purpose I/O. Software configurable for direction, interrupt sources, and counter/timer triggers. |

| P11 | PC01 | PORTC[1] Software configurable general-purpose I/O. Software configurable for direction, interrupt sources, and counter/timer triggers. |

| P12 | SDA2 | l <sup>2</sup> C2 Data                                                                                                                  |

| P13 | CTX1 | CAN1 TX                                                                                                                                 |

| P14 | CRX1 | CAN1 RX                                                                                                                                 |

# 3.4 Pin Descriptions

| Pin Type  | Description                                                                                                                                                                                                             | Туре                                  | Internal<br>Pull-<br>up/down |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|------------------------------|

|           | System Pins                                                                                                                                                                                                             |                                       |                              |

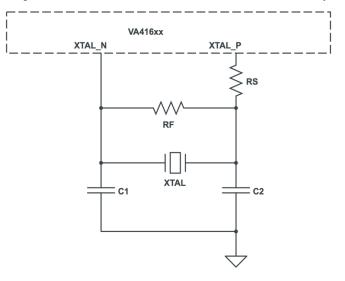

| XTAL_P    | Crystal Oscillator Output                                                                                                                                                                                               | Out                                   | None                         |

| XTAL_N    | Crystal Oscillator Input                                                                                                                                                                                                | In                                    | None                         |

| EXTRESETn | External System Reset, active low. Resets the<br>processor and all peripherals. This signal is<br>internally synchronized before being used. Any<br>reset will cause this pin to pull low during the<br>reset sequence. | Async In<br>/<br>Open<br>drain<br>Out | Pull-up                      |

| NMI       | Non-maskable Interrupt – active high                                                                                                                                                                                    | Async In                              | None                         |

| EBI_BOOT  | When high, this signal enables software boot<br>from the EBI port rather than the SPI ROM<br>interface.                                                                                                                 | In                                    | None                         |

| EXT15_SEL | When high, this signal disables the internal 1.5<br>V regulator, and 1.5 V must be applied<br>externally to all VDD15 pins and A_VDD15.                                                                                 | In                                    | None                         |

| NVM_PROTn | When low, this signal inhibits the programming of the internal FRAM (VA41630 only).                                                                                                                                     | In                                    | None                         |

| TEST_MODE | For factory use only. Must be tied to VSS with a 10k resistor.                                                                                                                                                          | In                                    | None                         |

|           | General-Purpose I/O Pins                                                                                                                                                                                                |                                       |                              |

**Product Datasheet**

| Pin Type    | Description                                                                                                                                                                                                          | Туре        | Internal<br>Pull-<br>up/down |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------------------------------|

| PORTA[15:0] | Software configurable general-purpose I/O<br>pins. Software configurable for direction,<br>interrupt sources, and counter/timer triggers.<br>These pins are configurable as UART, SPI,<br>Timers, and Ethernet pins. | Sync<br>I/O | Software<br>configurable     |

| PORTB[15:0] | Software configurable general-purpose I/O<br>pins. Software configurable for direction,<br>interrupt sources, and counter/timer triggers.<br>These pins are configurable as UART, SPI,<br>Timers, and Ethernet pins. | Sync<br>I/O | Software<br>configurable     |

| PORTC[15:0] | Software configurable general-purpose I/O<br>pins. Software configurable for direction,<br>interrupt sources, and counter/timer triggers.<br>These pins are configurable as UART, SPI,<br>Timers, and EBI pins.      | Sync<br>I/O | Software<br>configurable     |

| PORTD[15:0] | Software configurable general-purpose I/O<br>pins. Software configurable for direction,<br>interrupt sources, and counter/timer triggers.<br>These pins are configurable as UART, Timers,<br>and EBI pins.           | Sync<br>I/O | Software<br>configurable     |

| PORTE[15:0] | Software configurable general-purpose I/O<br>pins. Software configurable for direction,<br>interrupt sources, and counter/timer triggers.<br>These pins are configurable as UART, SPI,<br>Timers, and EBI pins.      | Sync<br>I/O | Software<br>configurable     |

| PORTF[15:0] | Software configurable general-purpose I/O<br>pins. Software configurable for direction,<br>interrupt sources, and counter/timer triggers.<br>These pins are configurable as UART, SPI,<br>Timers, and EBI pins.      | Sync<br>I/O | Software<br>configurable     |

| PORTG[7:0]  | Software configurable general-purpose I/O<br>pins. Software configurable for direction,<br>interrupt sources, and counter/timer triggers.<br>These pins are configurable as UART, SPI, and<br>Timer pins.            | Sync<br>I/O | Software<br>configurable     |

|             | SPI ROM pins                                                                                                                                                                                                         |             |                              |

| ROM_SCK     | SPI Clock to Boot ROM.                                                                                                                                                                                               | Sync<br>Out | None                         |

| Pin Type   | Description                                                                                      | Туре           | Internal<br>Pull-<br>up/down |  |

|------------|--------------------------------------------------------------------------------------------------|----------------|------------------------------|--|

| ROM_SS     | SPI Chip Select to Boot ROM (Active Low).                                                        | Sync<br>Out    | None                         |  |

| ROM_MOSI   | SPI Data Out to Boot ROM.                                                                        | Sync<br>Out    | None                         |  |

| ROM_MISO   | SPI Data In from Boot ROM (must be tied to<br>VSS for VA41630 devices with an internal<br>FRAM). | Sync In        | Pull-down                    |  |

|            | l <sup>2</sup> C Pins                                                                            |                |                              |  |

| I2C0_SCL   | l²C0 Clock                                                                                       | Open<br>drain  | None                         |  |

| I2C0_SDA   | l²C0 Data                                                                                        | Open<br>drain  | None                         |  |

| I2C1_SCL   | l²C1 Clock                                                                                       | Open<br>drain  | None                         |  |

| I2C1_SDA   | l <sup>2</sup> C1 Data Ope<br>drain                                                              |                | None                         |  |

| I2C2_SCL   | l²C2 Clock                                                                                       | Open<br>drain  | None                         |  |

| I2C2_SDA   | l <sup>2</sup> C2 Data                                                                           | Open<br>drain  | None                         |  |

|            | CAN Pins                                                                                         |                |                              |  |

| CAN0_RX    | CAN0 Receive                                                                                     | Sync In        | None                         |  |

| CAN0_TX    | CAN0 Transmit                                                                                    | Sync<br>Out    | None                         |  |

| CAN1_RX    | CAN1 Receive                                                                                     | Sync In        | None                         |  |

| CAN1_TX    | CAN1 Transmit                                                                                    | Sync<br>Out    | None                         |  |

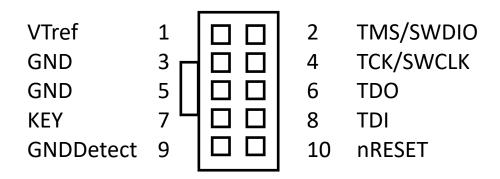

| SWD Pins   |                                                                                                  |                |                              |  |

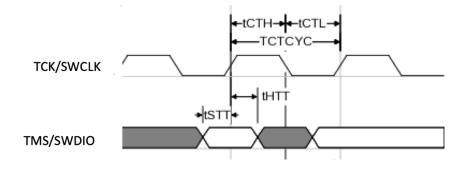

| TCK/SWCK   | Test Clock/Serial Wire Debug Clock                                                               | Clock          | None                         |  |

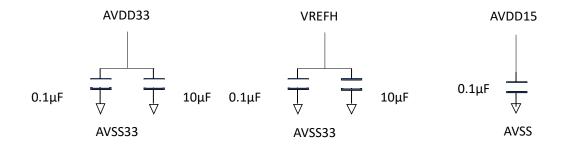

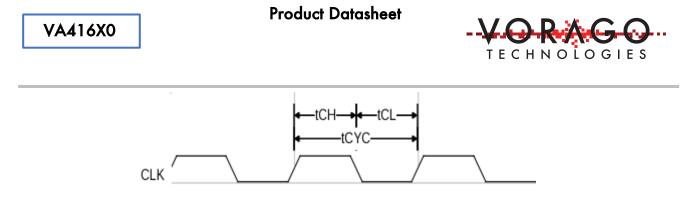

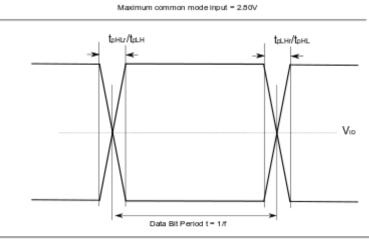

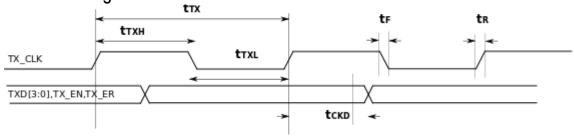

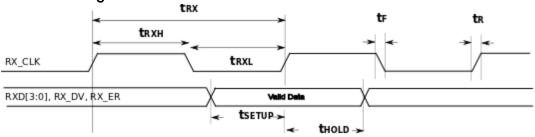

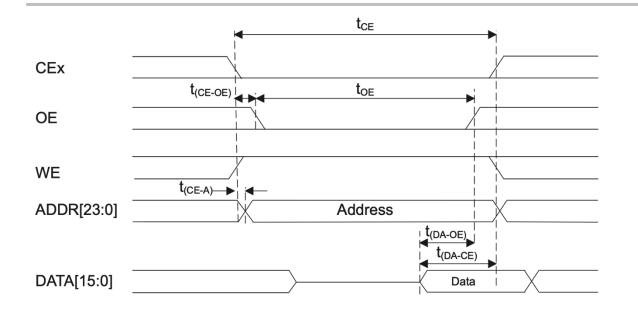

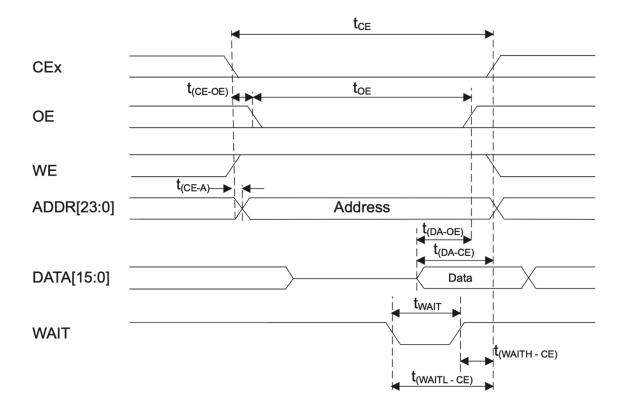

| TMS/SWDIO  | Test Mode Select/Serial Wire Debug Data IO                                                       | Sync<br>In/Out | Pull-up                      |  |