## CoreSight<sup>®</sup> ETM<sup>®</sup>-M4

Revision: r0p1

**Technical Reference Manual**

Copyright © 2009, 2010 ARM Limited. All rights reserved. ARM DDI 0440C (ID070610)

#### CoreSight ETM-M4 Technical Reference Manual

Copyright © 2009, 2010 ARM Limited. All rights reserved.

#### **Release Information**

The following changes have been made to this book.

Change history

| Date             | Issue | Confidentiality                     | Change                  |

|------------------|-------|-------------------------------------|-------------------------|

| 22 December 2009 | А     | Non-Confidential, Restricted Access | First release for r0p0  |

| 02 March 2010    | В     | Non-Confidential                    | Second release for r0p0 |

| 29 June 2010     | С     | Non-Confidential                    | Updated for r0p1        |

#### **Proprietary Notice**

Words and logos marked with  ${}^{\otimes}$  or  ${}^{\bowtie}$  are registered trademarks or trademarks of ARM Limited in the EU and other countries, except as otherwise stated below in this proprietary notice. Other brands and names mentioned herein may be the trademarks of their respective owners.

Neither the whole nor any part of the information contained in, or the product described in, this document may be adapted or reproduced in any material form except with the prior written permission of the copyright holder.

The product described in this document is subject to continuous developments and improvements. All particulars of the product and its use contained in this document are given by ARM in good faith. However, all warranties implied or expressed, including but not limited to implied warranties of merchantability, or fitness for purpose, are excluded.

This document is intended only to assist the reader in the use of the product. ARM Limited shall not be liable for any loss or damage arising from the use of any information in this document, or any error or omission in such information, or any incorrect use of the product.

Where the term ARM is used it means "ARM or any of its subsidiaries as appropriate".

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by ARM and the party that ARM delivered this document to.

Unrestricted Access is an ARM internal classification.

#### **Product Status**

The information in this document is final, that is for a developed product.

#### Web Address

http://www.arm.com

## Contents CoreSight ETM-M4 Technical Reference Manual

\_

|           | Prefa                                                        | ace                                                                                                                                                     |                                        |  |  |  |

|-----------|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--|--|--|

|           |                                                              | About this book                                                                                                                                         | viii                                   |  |  |  |

|           |                                                              | Feedback                                                                                                                                                | x                                      |  |  |  |

| Chapter 1 | Introduction                                                 |                                                                                                                                                         |                                        |  |  |  |

|           | 1.1                                                          | About the ETM-M4                                                                                                                                        | 1-2                                    |  |  |  |

|           | 1.2                                                          | Compliance                                                                                                                                              | 1-3                                    |  |  |  |

|           | 1.3                                                          | Features                                                                                                                                                |                                        |  |  |  |

|           | 1.4                                                          | Interfaces                                                                                                                                              | 1-5                                    |  |  |  |

|           | 1.5                                                          | Configurable options                                                                                                                                    | 1-6                                    |  |  |  |

|           | 1.6                                                          | Test features                                                                                                                                           |                                        |  |  |  |

|           | 1.7                                                          | Product documentation, design flow, and architecture                                                                                                    | 1-8                                    |  |  |  |

|           | 1.8                                                          | Product revisions                                                                                                                                       | 1-10                                   |  |  |  |

| Chanter 2 | <b>F</b>                                                     | ational Description                                                                                                                                     |                                        |  |  |  |

| Chapter 2 | Fund                                                         |                                                                                                                                                         |                                        |  |  |  |

| Chapter 2 | <b>FUN</b><br>2.1                                            | ctional Description<br>About the functions                                                                                                              |                                        |  |  |  |

| Chapter 2 |                                                              | About the functions                                                                                                                                     |                                        |  |  |  |

| Chapter 2 | 2.1                                                          |                                                                                                                                                         | 2-7                                    |  |  |  |

| ·         | 2.1<br>2.2<br>2.3                                            | About the functions<br>Interfaces<br>Operation                                                                                                          | 2-7                                    |  |  |  |

| Chapter 2 | 2.1<br>2.2<br>2.3<br><b>Prog</b>                             | About the functions<br>Interfaces<br>Operation                                                                                                          |                                        |  |  |  |

| ·         | 2.1<br>2.2<br>2.3<br><b>Prog</b><br>3.1                      | About the functions<br>Interfaces<br>Operation<br>grammers Model<br>About the programmers model                                                         |                                        |  |  |  |

| ·         | 2.1<br>2.2<br>2.3<br><b>Prog</b><br>3.1<br>3.2               | About the functions<br>Interfaces<br>Operation<br>grammers Model<br>About the programmers model<br>Modes of operation and execution                     | 2-7<br>2-8<br>                         |  |  |  |

| ·         | 2.1<br>2.2<br>2.3<br><b>Prog</b><br>3.1                      | About the functions<br>Interfaces<br>Operation<br>grammers Model<br>About the programmers model                                                         | 2-7<br>2-8<br>3-2<br>3-3<br>3-4        |  |  |  |

| Chapter 3 | 2.1<br>2.2<br>2.3<br><b>Prog</b><br>3.1<br>3.2<br>3.3<br>3.4 | About the functions                                                                                                                                     | 2-7<br>2-8<br>3-2<br>3-3<br>3-4        |  |  |  |

| ·         | 2.1<br>2.2<br>2.3<br><b>Prog</b><br>3.1<br>3.2<br>3.3<br>3.4 | About the functions<br>Interfaces<br>Operation<br>grammers Model<br>About the programmers model<br>Modes of operation and execution<br>Register summary | 2-7<br>2-8<br>3-2<br>3-3<br>3-4<br>3-6 |  |  |  |

Appendix B Revisions

Glossary

## List of Tables CoreSight ETM-M4 Technical Reference Manual

|            | Change history                          | ii   |

|------------|-----------------------------------------|------|

| Table 2-1  | Cortex-M4 resources                     |      |

| Table 2-2  | Boolean function encoding for events    |      |

| Table 2-3  | Resource identification encoding        |      |

| Table 3-1  | ETM registers                           |      |

| Table 3-2  | ETMCR bit assignments                   |      |

| Table 3-3  | ETMCCR bit assignments                  |      |

| Table 3-4  | ETMSCR bit assignments                  |      |

| Table 3-5  | ETMTECR1 bit assignments                |      |

| Table 3-6  | ETMIDR bit assignments                  |      |

| Table 3-7  | ETMCCER bit assignments                 |      |

| Table 3-8  | ETMTESSEICR bit assignments             | 3-13 |

| Table 3-9  | ETMPDSR bit assignments                 |      |

| Table 3-10 | ITMISCIN bit assignments                |      |

| Table 3-11 | ITTRIGOUT bit assignments               |      |

| Table 3-12 | ETM_ITATBCTR2 bit assignments           |      |

| Table 3-13 | ETM_ITATBCTR0 bit assignments           |      |

| Table A-1  | Input connections                       |      |

| Table A-2  | Trigger output connections              | A-2  |

| Table B-1  | issue A                                 | B-1  |

| Table B-2  | Differences between issue A and issue B |      |

| Table B-3  | Differences between issue B and issue C | B-1  |

# List of Figures CoreSight ETM-M4 Technical Reference Manual

| Cortex-M4 with ETM-M4 block diagram |                                                                                                                                                                                                                                                                                                                                     |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ETM block diagram                   | . 2-2                                                                                                                                                                                                                                                                                                                               |

| ETMCR bit assignments               | . 3-6                                                                                                                                                                                                                                                                                                                               |

| ETMCCR bit assignments              |                                                                                                                                                                                                                                                                                                                                     |

| ETMSCR bit assignments              | . 3-9                                                                                                                                                                                                                                                                                                                               |

|                                     |                                                                                                                                                                                                                                                                                                                                     |

| ETMIDR bit assignments              | 3-11                                                                                                                                                                                                                                                                                                                                |

| ETMCCER bit assignments             | 3-12                                                                                                                                                                                                                                                                                                                                |

| ETMTESSEICR bit assignments         | 3-13                                                                                                                                                                                                                                                                                                                                |

|                                     | 3-14                                                                                                                                                                                                                                                                                                                                |

| ITMISCIN bit assignments            | 3-14                                                                                                                                                                                                                                                                                                                                |

| ITTRIGOUT bit assignments           | 3-15                                                                                                                                                                                                                                                                                                                                |

| ETM_ITATBCTR2 bit assignments       | 3-16                                                                                                                                                                                                                                                                                                                                |

| ETM_ITATBCTR0 bit assignments       | 3-16                                                                                                                                                                                                                                                                                                                                |

|                                     | ETM block diagram<br>ETMCR bit assignments<br>ETMCCR bit assignments<br>ETMSCR bit assignments<br>ETMTECR1 bit assignments<br>ETMIDR bit assignments<br>ETMCCER bit assignments<br>ETMTESSEICR bit assignments<br>ETMPDSR bit assignments<br>ITMISCIN bit assignments<br>ITTRIGOUT bit assignments<br>ETM_ITATBCTR2 bit assignments |

### Preface

This preface introduces the *CoreSight ETM-M4 Technical Reference Manual*. It contains the following sections:

- About this book on page viii

- *Feedback* on page x.

#### About this book

This book is for the CoreSight Embedded Trace Macrocell<sup>™</sup> for the Cortex-M4 and Cortex-M4F processors, the CoreSight ETM-M4 macrocell.

You implement the ETM-M4 macrocell with either the Cortex-M4 processor or the Cortex-M4F processor. In this manual, in general:

- any reference to the processor applies to either the Cortex-M4 processor or the Cortex-M4F processor, as appropriate

- any reference to the Cortex-M4 processor applies also to the Cortex-M4F processor, as appropriate.

The context makes it clear if information applies to only one of the processor options.

#### **Product revision status**

The *rnpn* identifier indicates the revision status of the product described in this book, where:

- **r***n* Identifies the major revision of the product.

- **pn** Identifies the minor revision or modification status of the product.

#### Intended audience

This book is written for:

- Designers of development tools providing support for ETM functionality. Implementation-specific behavior is described in this document. You can find complementary information in the *Embedded Trace Macrocell Architecture Specification* (ARM IHI 0014).

- Hardware and software engineers integrating the macrocell into an ASIC that includes a Cortex<sup>™</sup>-M4 processor. You can find complementary information in the *Cortex-M4 Integration Manual* (ARM DII 0239).

#### Using this book

This book is organized into the following chapters:

#### Chapter 1 Introduction

Read this for an introduction to the functionality of the macrocell.

#### **Chapter 2** Functional Description

Read this for a description of the interfaces, operation, clocking and resets of the macrocell.

#### **Chapter 3** Programmers Model

Read this for a description of the programmers model for the macrocell.

#### Appendix A Signal Descriptions

Read this for a summary of ETM signals.

#### Appendix B Revisions

Read this for a description of the technical changes between released issues of this book.

#### Conventions

Conventions that this book can use are described in:

Typographical

#### Typographical

The typographical conventions are:

| italic            | Highlights important notes, introduces special terminology, denotes internal cross-references, and citations.                              |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| bold              | Highlights interface elements, such as menu names. Denotes signal names. Also used for terms in descriptive lists, where appropriate.      |

| monospace         | Denotes text that you can enter at the keyboard, such as commands, file<br>and program names, and source code.                             |

| <u>mono</u> space | Denotes a permitted abbreviation for a command or option. You can enter<br>the underlined text instead of the full command or option name. |

| monospace italic  | Denotes arguments to monospace text where the argument is to be replaced by a specific value.                                              |

| monospace bold    | Denotes language keywords when used outside example code.                                                                                  |

| < and >           | Enclose replaceable terms for assembler syntax where they appear in code or code fragments. For example:                                   |

|                   | <pre>MRC p15, 0 <rd>, <crn>, <crm>, <opcode_2></opcode_2></crm></crn></rd></pre>                                                           |

#### **Further reading**

This section lists publications by ARM and by third parties.

See http://infocenter.arm.com for access to ARM documentation.

#### **ARM** publications

This book contains information that is specific to this product. See the following documents for other relevant information:

- Cortex-M4 Technical Reference Manual (ARM DDI 0439)

- Cortex-M4 Integration and Implementation Manual (ARM DII 0239)

- Embedded Trace Macrocell<sup>TM</sup> Architecture Specification (ARM IHI 0014)

- CoreSight Components Technical Reference Manual (ARM DDI 0314)

- CoreSight Architecture Specification (ARM IHI 0020)

- CoreSight Technology System Design Guide (ARM DGI 0012)

- *AMBA<sup>™</sup> 3 APB Protocol Specification* (ARM IHI 0024)

- AMBA 3 ATB Protocol Specification (ARM IHI 0032).

#### Feedback

ARM welcomes feedback on this product and its documentation.

#### Feedback on this product

If you have any comments or suggestions about this product, contact your supplier and give:

- The product name.

- The product revision or version.

- An explanation with as much information as you can provide. Include symptoms if appropriate.

#### Feedback on this book

If you have any comments on this book, send an e-mail to errata@arm.com. Give:

- the title

- the number

- the relevant page number(s) to which your comments apply

- a concise explanation of your comments.

ARM also welcomes general suggestions for additions and improvements.

## Chapter 1 Introduction

This chapter introduces the ETM-M4 macrocell. It contains the following sections:

- *About the ETM-M4* on page 1-2

- *Compliance* on page 1-3

- *Features* on page 1-4

- *Interfaces* on page 1-5

- *Configurable options* on page 1-6

- *Test features* on page 1-7

- Product documentation, design flow, and architecture on page 1-8

- *Product revisions* on page 1-10.

#### 1.1 About the ETM-M4

The Cortex-M4 *Embedded Trace Macrocell* (ETM-M4) is an optional debug component that enables a debugger to reconstruct program execution. The CoreSight ETM-M4 supports only instruction trace. You can use it either with the Cortex-M4 *Trace Port Interface Unit* (M4-TPIU), or as part of a CoreSight system.

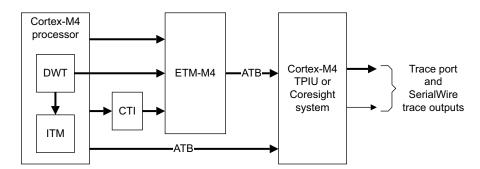

Figure 1-1 shows a typical Cortex-M4 system in a System-on-Chip (SoC) that includes a CoreSight ETM-M4 macrocell.

Figure 1-1 Cortex-M4 with ETM-M4 block diagram

#### 1.2 Compliance

ETM-M4 is compatible with the CoreSight architecture.

ETM-M4 implements version 3.5 of the ETM architecture, ETMv3.5. See the *Embedded Trace Macrocell Architecture Specification* for more information.

For more information about architectural compliance, see *Architecture and protocol information* on page 1-9.

#### 1.3 Features

ETM-M4 provides:

- tracing of 16-bit and 32-bit Thumb instructions

- four EmbeddedICE watchpoint inputs

- a Trace Start/Stop block with EmbeddedICE inputs

- one reduced function counter

- two external inputs

- a 24-byte FIFO queue

- global timestamping.

See the Embedded Trace Macrocell Architecture Specification for information about:

- the trace protocol

- controlling tracing using triggering and filtering resources.

See the *Cortex-M4 Integration and Implementation Manual* for information about the macrocell signals.

#### 1.4 Interfaces

The system connections to the ETM-M4 are supported using a Cross Trigger Interface (CTI):

- 0-2 external inputs

- trigger output.

See *Configurable options* on page 1-6 and *Interfaces* on page 2-7 for more information about the external inputs and external outputs.

#### 1.5 Configurable options

The ETM-M4 macrocell includes the following configuration inputs:

- the maximum number of external inputs, see *External inputs* on page 2-5

- whether the system supports the FIFOFULL mechanism for stalling the processor, see Table 2-1 on page 2-3.

#### 1.6 Test features

The ETM-M4 does not include any specific Design For Test (DFT) features.

#### **1.7 Product documentation, design flow, and architecture**

This section describes the ETM-M4 books, how they relate to the design flow, and the relevant architectural standards and protocols.

See Further reading on page ix for more information about the books described in this section.

#### 1.7.1 Documentation

The ETM-M4 documentation is as follows:

#### **Technical Reference Manual**

The *Technical Reference Manual* (TRM) describes the functionality and the effects of functional options on the behavior of the ETM-M4. It is required at all stages of the design flow. Some behavior described in the TRM might not be relevant because of the way that the ETM-M4 is implemented and integrated.

#### **Integration and Implementation Manual**

For both the processor and the ETM, the *Cortex-M4 Integration and Implementation Manual* (IIM) describes:

- The available build configuration options and related issues in selecting them.

- How to configure the *Register Transfer Level* (RTL) with the build configuration options.

- How to integrate the processor into a SoC. This includes a description of the integration kit and describes the pins that the integrator must tie off to configure the macrocell for the required integration.

- How to implement the processor and ETM in your design. This includes floorplanning guidelines, Design for Test (DFT) information, and how to perform netlist dynamic verification on the processor.

- The processes to sign off the integration and implementation of the design.

The ARM product deliverables include reference scripts and information about using the scripts to implement your design.

Reference methodology documentation from your EDA tools vendor complements the IIM.

The IIM is a confidential book that is only available to licensees.

#### 1.7.2 Design flow

The ETM-M4 is delivered as synthesizable RTL. Before it can be used in a product, it must go through the following process:

- 1. Implementation. The implementer synthesizes the RTL, usually in combination with the processor, then places and routes the netlist to produce a hard macrocell.

- 2. Integration. The integrator instantiates the macrocell of the combined processor and ETM into a SoC. This includes testing its integration with the other SoC components to which it is connected.

- 3. Programming. The debug software developer programs the ETM and tests any trace software required for use with a SoC.

For more information see the Cortex-M4 Integration and Implementation Manual.

#### 1.7.3 Architecture and protocol information

The ETM-M4 complies with, or implements, the specifications described in:

- Trace macrocell

- Advanced Microcontroller Bus Architecture.

This TRM complements architecture reference manuals, architecture specifications, protocol specifications, and relevant external standards. It does not duplicate information from these sources.

#### Trace macrocell

The ETM-M4 implements the ETM architecture version 3.5. See *Embedded Trace Macrocell Architecture Specification*.

#### Advanced Microcontroller Bus Architecture

This ETM-M4 complies with the Advanced Microcontroller Bus Architecture (AMBA) 3 Advanced Peripheral Bus (APB) and Advanced Trace Bus (ATB) protocols. See AMBA 3 APB Protocol Specification and AMBA 3 ATB Protocol Specification.

#### 1.8 **Product revisions**

This section describes the differences in functionality between product revisions:

- r0p0 First release.

- **r0p1** There are no differences in fuctionality for this release.

## Chapter 2 Functional Description

This chapter describes the interfaces, operation, clocking and resets of the macrocell. It contains the following sections:

- *About the functions* on page 2-2

- Interfaces on page 2-7

- *Operation* on page 2-8.

#### 2.1 About the functions

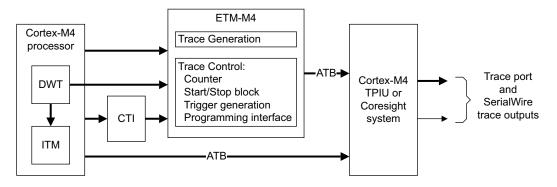

Figure 2-1 shows a block diagram of the ETM, and shows how the ETM interfaces to the *Trace Port Interface Unit* (TPIU).

#### Figure 2-1 ETM block diagram

The Cortex-M4 system can perform low-bandwidth data tracing using the *Data Watchpoint and Trace* (DWT) and *Instruction Trace Macrocell* (ITM) components.

The ETM trace output is compatible with the *AMBA Trace Bus* (ATB) protocol, irrespective of the configuration of the trace port size and trace port mode within the ETM programmers model. The TPIU exports trace information from the processor. An implementation can replace the TPIU with other CoreSight trace components.

For more information see:

- Cortex-M4 Technical Reference Manual

- Embedded Trace Macrocell Architecture Specification.

The ETM provides a trace ID register for systems that use multiple trace sources. You must configure this register even if only a single trace source is in use.

The following sections provide information on features of the ETM:

- Resources

- *Timestamp format* on page 2-5

- *Periodic synchronization* on page 2-5

- Data and instruction address compare resources on page 2-5

- External inputs on page 2-5

- Start/stop block on page 2-5

- *Triggering* on page 2-6.

#### 2.1.1 Resources

Because the ETM does not generate data trace information, the lower bandwidth reduces the requirement for complex triggering capabilities. This means that the ETM only includes a small sub-set of the possible resources allowed by the ETM architecture.

Table 2-1 lists the Cortex-M4 resources.

#### Table 2-1 Cortex-M4 resources

| Feature                                   | Present on ETM-M4                       |  |

|-------------------------------------------|-----------------------------------------|--|

| Architecture version                      | ETMv3.5                                 |  |

| Address comparator pairs                  | 0                                       |  |

| Data comparators                          | 0                                       |  |

| Context ID comparators                    | 0                                       |  |

| Memory Map Decoders (MMDs)                | 0                                       |  |

| Counters                                  | 1, reduced function counter only        |  |

| Sequencer                                 | No                                      |  |

| Start/stop block                          | Yes                                     |  |

| Embedded ICE comparators                  | 4                                       |  |

| External inputs                           | 2                                       |  |

| External outputs                          | 0                                       |  |

| Extended external inputs                  | 0                                       |  |

| Extended external input selectors         | 0                                       |  |

| FIFOFULL                                  | Yes                                     |  |

| FIFOFULL level setting                    | Yes                                     |  |

| Branch broadcasting                       | Yes                                     |  |

| ASIC Control Register                     | No                                      |  |

| Data suppression                          | No                                      |  |

| Software access to registers              | Yes                                     |  |

| Readable registers                        | Yes                                     |  |

| FIFO size                                 | 24 bytes                                |  |

| Minimum port size                         | 8 bits                                  |  |

| Maximum port size                         | 8 bits                                  |  |

| Normal port mode                          | -                                       |  |

| Normal half-rate clocking, 1:1            | Yes - asynchronous                      |  |

| Demux port mode                           | -                                       |  |

| Demux half-rate clocking, 1:2             | No                                      |  |

| Mux port mode, 2:1                        | No                                      |  |

| 1:4 port mode                             | No                                      |  |

| Dynamic port mode, including stalling     | No. Supported by asynchronous port mode |  |

| Coprocessor Register Transfer (CPRT) data | No                                      |  |

|                   | Υ                 |

|-------------------|-------------------|

| Feature           | Present on ETM-M4 |

| Load PC first     | No                |

| Fetch comparisons | No                |

| Load data traced  | No                |

#### Table 2-1 Cortex-M4 resources (continued)

#### **Resource identification encoding**

You configure the trace enable event, timestamp event, and trigger event using the same mechanism. For each event, a 17-bit register is used to define the event. This register provides:

- Resource A, bits [6:0]

- Resource B, bits [13:7]

- a Boolean function, bits [16:14].

Table 2-2 shows the encodings used for the Boolean function.

#### Table 2-2 Boolean function encoding for events

| Encoding | Function           |

|----------|--------------------|

| 0b000    | А                  |

| 0b001    | NOT(A)             |

| 0b010    | A AND B            |

| 0b011    | NOT(A) AND B       |

| 0b100    | NOT(A) AND NOT (B) |

| 0b101    | A OR B             |

| 0b110    | NOT (A) OR B       |

| 0b111    | NOT (A) OR NOT (B) |

|          |                    |

Table 2-3 shows the encodings used for Resource identification.

#### Table 2-3 Resource identification encoding

| Resource type <sup>a</sup> | Index range <sup>b</sup> | Description of resource type |

|----------------------------|--------------------------|------------------------------|

| 0b010                      | 0-3                      | DWT Comparator inputs (0-3)  |

| 0b100                      | 0                        | Counter 1 at zero            |

| 0b101                      | 15                       | Trace Start/Stop resource    |

| 0b110                      | 0-1                      | ExtIn (0-1)                  |

| 0b110                      | 15                       | HardWired (always True)      |

|                            |                          |                              |

a. For Resource A, bits [6:4]. For Resource B, bits [13:11]

b. For Resource A, bits [3:0]. For Resource B, bits [10:7].

#### 2.1.2 Timestamp format

Timestamps are encoded as 48-bit natural binary numbers. A system implementation may provide a timestamp count which can be used by several trace sources as an aid to correlating the trace streams.

#### 2.1.3 Periodic synchronization

The ETM uses a fixed synchronization packet generation frequency of every 1024 bytes of trace.

#### 2.1.4 Data and instruction address compare resources

The DWT provides four address comparators on the data bus that provide debug functionality. Within the DWT unit, you can specify the functions triggered by a match, and one of these functions is to generate an ETM match input. These inputs are presented to the ETM as Embedded *In Circuit Emulator* (ICE) comparator inputs.

A single DWT resource can trigger an ETM event and also generate instrumentation trace directly from the same event.

You can configure the four DWT comparators individually to compare with the address of the current executing instruction to permit the ETM access to an instruction address compare resource. These inputs are presented to the ETM as Embedded ICE comparator inputs. The DWT provides either 1 or 4 comparators, depending on the implementation of the processor.

```

—— Note ———

```

Using a DWT comparator as an instruction address comparator reduces the number of available data address comparisons.

See the Cortex-M4 Technical Reference Manual for more information about the DWT unit.

#### 2.1.5 External inputs

Two external inputs, **ETMEXTIN**[1:0], enable additional components to generate trigger and enable signals for the ETM.

#### 2.1.6 Start/stop block

The start/stop block provides a single-bit resource that can be used as an input to other parts of the resource logic, including the trace enable logic. The start/stop block can only be controlled by using the EmbeddedICE inputs to the ETM. The DWT controls these inputs.

The start/stop block is set to the start state if any of the EmbeddedICE watchpoint inputs selected as start resources in ETMTESSEICR go HIGH. The start/stop block is set to the stop state if any of the EmbeddedICE watchpoint inputs selected as stop resources in ETMTESSEICR go LOW.

If bit [25] of ETMTECR1 is 1, tracing will only be enabled when the start/stop block is in the start state.

Tracing is also only enabled when the result of evaluating the Trace Enable Event is TRUE. This event can be set to always be TRUE by programming a value of 0x6F to ETMTEEVR. For more information see the *Embedded Trace Macrocell Architecture Specification*.

#### 2.1.7 Triggering

The ETM provides a trigger resource that can be used to identify a point within a trace run. The generation of a trigger does not affect the tracing in any way, but the trigger will be output in the trace stream, and can also be passed to other trace components or used to halt the processor. An external trace port analyzer can use the trigger to determine when to start and stop capture of trace.

#### 2.2 Interfaces

The ETM-M4 has the following external interfaces:

- **ATB** A 32-bit *Advanced Trace Bus* provides trace output from the macrocell. See the *AMBA 3 ATB Protocol Specification* for more information about this interface.

- **APB** An *Advanced Peripheral Bus* provides the control interface for the macrocell. See the *AMBA 3 APB Protocol Specification* for more information about this interface.

- CTI Your implementation can provide a *Cross Trigger Interface* to manage the interconnection of trigger and control signals between the processor core, ETM, and TPIU. The implementation of your Cortex-M4 processor determines which ETM functions are visible to the CTI. See Appendix A *Signal Descriptions* for details of recommended CTI connections for Cortex-M4 systems.

#### 2.3 Operation

ETM-M4 implements version 3.5 of the ARM Embedded Trace Macrocell protocol. See the *Embedded Trace Macrocell Architecture Specification*.

## Chapter 3 Programmers Model

This chapter describes the programmers model. It contains the following sections:

- *About the programmers model* on page 3-2

- *Modes of operation and execution* on page 3-3

- Register summary on page 3-4

- *Register descriptions* on page 3-6.

#### 3.1 About the programmers model

This chapter describes the mechanisms for programming the registers used to set up the trace and triggering facilities of the macrocell. The programmers model enables you to use the ETM registers to control the macrocell.

#### 3.2 Modes of operation and execution

ETM-M4 implements ETMv3.5 for tracing 16-bit and 32-bit Thumb instructions.

The Embedded Trace Macrocell Architecture Specification describes the features of ETMv3.5.

See Features on page 1-4 for information on the trace features of the ETM-M4.

When the ETM is powered up or reset, you must program all of the registers that do not have an architected reset state before you enable tracing. If you do not do so, the trace results are UNPREDICTABLE.

When programming the ETM registers you must enable all the changes at the same time. To achieve this, the Programming bit in ETMCR should be used. See *Main Control Register*, *ETMCR* on page 3-6.

When the Programming bit is set to 0 you must not write to registers other than ETMCR, because this can lead to UNPREDICTABLE behavior.

When setting the Programming bit, you must not change any other bits of ETMCR. You must only change the value of bits other than the Programming bit of ETMCR when bit [1] of ETMSR is set to 1. ARM recommends that you use a read-modify-write procedure when changing ETMCR.

#### 3.3 Register summary

This section describes the ETM registers. Table 3-1 provides cross references to individual registers.

#### Table 3-1 ETM registers

| Address    | Name          | Reset      | Туре | Description                                                                      |

|------------|---------------|------------|------|----------------------------------------------------------------------------------|

| 0xE0041000 | ETMCR         | 0x00000411 | RW   | Main Control Register, ETMCR on page 3-6                                         |

| 0xE0041004 | ETMCCR        | 0x8C802000 | RO   | Configuration Code Register, ETMCCR on page 3-8                                  |

| 0xE0041008 | ETMTRIGGER    | -          | RW   | Trigger Event Register                                                           |

| 0xE0041010 | ETMSR         | -          | RW   | ETM Status Register                                                              |

| 0xE0041014 | ETMSCR        | 0x00020D09 | RO   | System Configuration Register, ETMSCR on page 3-9                                |

| 0xE0041020 | ETMTEEVR      | -          | RW   | TraceEnable Event Register                                                       |

| 0xE0041024 | ETMTECR1      | -          | RW   | TraceEnable Control 1 Register, ETMTECR1 on page 3-10                            |

| 0xE0041028 | ETMFFLR       | -          | RW   | FIFOFULL Level Register                                                          |

| 0xE0041140 | ETMCNTRLDVR1  | -          | RW   | Free-running counter reload value                                                |

| 0xE00411E0 | ETMSYNCFR     | 0x00000400 | RO   | Synchronization Frequency Register                                               |

| 0xE00411E4 | ETMIDR        | 0x4114F250 | RO   | ID Register, ETMIDR on page 3-11                                                 |

| 0xE00411E8 | ETMCCER       | 0x18541800 | RO   | Configuration Code Extension Register, ETMCCER on page 3-12                      |

| 0xE00411F0 | ETMTESSEICR   | -          | RW   | TraceEnable Start/Stop EmbeddedICE Control Register,<br>ETMTESSEICR on page 3-13 |

| 0xE00411F8 | ETMTSEVR      | -          | RW   | Timestamp Event Register                                                         |

| 0xE0041200 | ETMTRACEIDR   | 0x00000000 | RW   | CoreSight Trace ID Register                                                      |

| 0xE0041208 | ETMIDR2       | 0×00000000 | RO   | ETM ID Register 2                                                                |

| 0xE0041314 | ETMPDSR       | 0x00000001 | RO   | Device Power-Down Status Register, ETMPDSR on page 3-13                          |

| 0xE0041EE0 | ITMISCIN      | -          | RO   | Integration Test Miscellaneous Inputs, ITMISCIN on page 3-14                     |

| 0xE0041EE8 | ITTRIGOUT     | -          | WO   | Integration Test Trigger Out, ITTRIGOUT on page 3-15                             |

| 0xE0041EF0 | ETM_ITATBCTR2 | -          | RO   | <i>ETM Integration Test ATB Control 2, ETM_ITATBCTR2</i> on page 3-15            |

| 0xE0041EF8 | ETM_ITATBCTR0 | -          | WO   | <i>ETM Integration Test ATB Control 0, ETM_ITATBCTR0</i> on page 3-16            |

| 0xE0041F00 | ETMITCTRL     | 0x00000000 | RW   | Integration Mode Control Register                                                |

| 0xE0041FA0 | ETMCLAIMSET   | -          | RW   | Claim Tag Set Register                                                           |

| 0xE0041FA4 | ETMCLAIMCLR   | -          | RW   | Claim Tag Clear Register                                                         |

| 0xE0041FB0 | ETMLAR        | -          | RW   | Lock Access Register                                                             |

| 0xE0041FB4 | ETMLSR        | -          | RO   | Lock Status Register                                                             |

| 0xE0041FB8 | ETMAUTHSTATUS | -          | RO   | Authentication Status Register                                                   |

| 0xE0041FCC | ETMDEVTYPE    | 0x00000013 | RO   | CoreSight Device Type Register                                                   |

#### Table 3-1 ETM registers (continued)

| Address    | Name     | Reset      | Туре | Description                         |

|------------|----------|------------|------|-------------------------------------|

| 0xE0041FD0 | ETMPIDR4 | 0x00000004 | RO   | Peripheral Identification Registers |

| 0xE0041FD4 | ETMPIDR5 | 0x00000000 | RO   | -                                   |

| 0xE0041FD8 | ETMPIDR6 | 0x00000000 | RO   | -                                   |

| 0xE0041FDC | ETMPIDR7 | 0x00000000 | RO   | -                                   |

| 0xE0041FE0 | ETMPIDR0 | 0x00000025 | RO   | -                                   |

| 0xE0041FE4 | ETMPIDR1 | 0x000000B9 | RO   | -                                   |

| 0xE0041FE8 | ETMPIDR2 | 0x0000000B | RO   | -                                   |

| 0xE0041FEC | ETMPIDR3 | 0x00000000 | RO   | -                                   |

| 0xE0041FF0 | ETMCIDR0 | 0x0000000D | RO   | Component Identification Registers  |

| 0xE0041FF4 | ETMCIDR1 | 0x00000090 | RO   | -                                   |

| 0xE0041FF8 | ETMCIDR2 | 0x00000005 | RO   | -                                   |

| 0xE0041FFC | ETMCIDR3 | 0x000000B1 | RO   | -                                   |

#### 3.4 Register descriptions

The following sections describe those registers whose implementation is specific to this product. Other registers are described in the *Embedded Trace Macrocell Architecture Specification*.

#### 3.4.1 Main Control Register, ETMCR

The ETMCR characteristics are:

| Purpose           | Controls general operation of the ETM, such as whether tracing is enabled.     |

|-------------------|--------------------------------------------------------------------------------|

| Usage constraints | There are no usage constraints.                                                |

| Configurations    | This register is only available if the processor is configured to use the ETM. |

| Attributes        | See the ETM register summary in Table 3-1 on page 3-4.                         |

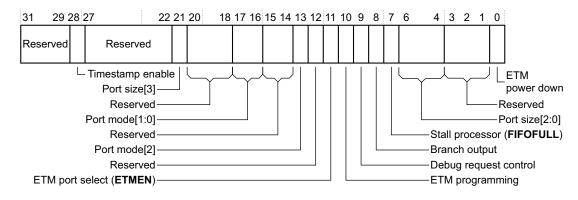

Figure 3-1 shows the ETMCR bit assignments.

Figure 3-1 ETMCR bit assignments

Table 3-2 shows the ETMCR bit assignments.

#### Table 3-2 ETMCR bit assignments

| Bits    | Name             | Function                                                                               |  |

|---------|------------------|----------------------------------------------------------------------------------------|--|

| [31:29] | -                | RAZ                                                                                    |  |

| [28]    | Timestamp enable | When set, this bit enables timestamping. An ETM reset sets this bit to 0.              |  |

| [27:22] | -                | RAZ                                                                                    |  |

| [21]    | Port size[3]     | This bit is implemented but has no function.<br>An ETM reset sets this bit to 0.       |  |

| [20:18] | -                | Reserved                                                                               |  |

| [17:16] | Port mode [1:0]  | These bits are implemented but have no function.<br>An ETM reset sets these bits to 0. |  |

| [15:14] | -                | Reserved                                                                               |  |

| [13]    | Port mode[2]     | This bit is implemented but has no function.<br>An ETM reset sets this bit to 0.       |  |

| [12]    | -                | Reserved                                                                               |  |

#### Table 3-2 ETMCR bit assignments (continued)

| Bits  | Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| [11]  | ETM port selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | This bit can be used to control other trace components in an implementation. The possible values are:         0       ETMEN is LOW.         1       ETMEN is HIGH.         This bit must be set by the trace software tools to ensure that trace output is enabled from this ETM.         An ETM reset sets this bit to 0.                                                                                                                                                                                                                                                         |  |

| [10]  | ETM programming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | This bit must be set to 1 at the start of the ETM programming sequence. Tracing is prevented while this bit is set to 1.<br>On an ETM reset this bit is set to 0b1.                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| [9]   | Debug request control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | When set to 1 and the trigger event occurs, the <b>ETMDBGRQ</b> output is asserted until <b>HALTED</b> is observed. This enables the ARM processor to be forced into Debug state.<br>An ETM reset sets this bit to 0.                                                                                                                                                                                                                                                                                                                                                              |  |

| [8]   | Branch output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | When set to 1 all branch addresses are output, even if the branch was because of a direct branch<br>instruction. Setting this bit enables reconstruction of the program flow without having access to<br>the memory image of the code being executed.<br>When this bit is set to 1, more trace data is generated, and this may affect the performance of the<br>trace system. Information about the execution of a branch is traced regardless of the state of this<br>bit.<br>An ETM reset sets this bit to 0.                                                                    |  |

| [7]   | Stall processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | The <b>FIFOFULL</b> output can be used to stall the processor to prevent overflow. The <b>FIFOFULL</b> output is only enabled when the stall processor bit is set to 1. When the bit is 0 the <b>FIFOFULL</b> output remains LOW at all times and the FIFO overflows if there are too many trace packets. Trace resumes without corruption once the FIFO has drained, if overflow does occur. An ETM reset sets this bit to 0.<br>For information about the interaction of this bit with the ETMFFLR register see the <i>Embedded Trace Macrocell Architecture Specification</i> . |  |

| [6:4] | Port size [2:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | The ETM-M4 has no influence over the external pins used for trace. These bits are implemented but not used.<br>On an ETM reset these bits reset to 0b001.                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| [3:1] | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| [0]   | <ul> <li>ETM power down</li> <li>This bit can be used by an implementation to control if the ETM is in a low power state. This must be cleared by the trace software tools at the beginning of a debug session. When this bit is set to 1, writes to some registers and fields might be ignored. You can always to the following registers and fields: <ul> <li>ETMCR bit [0]</li> <li>ETMLAR</li> <li>ETMCLAIMSET register</li> <li>ETMCLAIMCLR register</li> </ul> </li> <li>When the ETMCR is written with this bit set to 1, bits other than bit [0] might be ignored. On an ETM reset this bit is set to 1.</li> </ul> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

#### 3.4.2 Configuration Code Register, ETMCCR

The ETM Configuration Code Register characteristics are:

| Purpose | Enables software to read the implementation-specific configuration of the |

|---------|---------------------------------------------------------------------------|

|         | ETM.                                                                      |

| Usage constraints | There are no usage constraints. |

|-------------------|---------------------------------|

|                   |                                 |

**Configurations** This register is only available if the processor is configured to use the ETM.

Attributes See the ETM register summary in Table 3-1 on page 3-4.

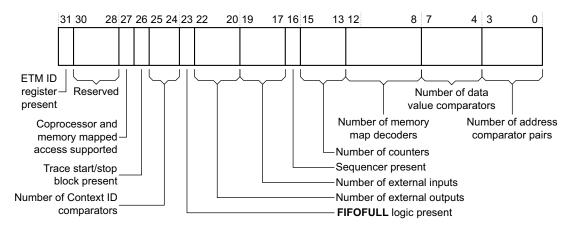

Figure 3-2 shows the ETMCCR bit assignments.

#### Figure 3-2 ETMCCR bit assignments

Table 3-3 shows the ETMCCR bit assignments.

#### Table 3-3 ETMCCR bit assignments

| Bits    | Name                             | Function                                                                                                                                                                                                                                                   |

|---------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [31]    | ETM ID register present          | The value of this bit is 1, indicating that the ETMIDR, register 0x79, is present and defines the ETM architecture version in use.                                                                                                                         |

| [30:28] | -                                | Reserved.                                                                                                                                                                                                                                                  |

| [27]    | Coprocessor and memory access    | The value of this bit is 1, indicating that memory-mapped access to registers is supported.                                                                                                                                                                |

| [26]    | Trace start/stop block present   | The value of this bit is 1, indicating that the Trace start/stop block is present.                                                                                                                                                                         |

| [25:24] | Number of Context ID comparators | The value of these bits is 0b00, indicating that Context ID comparators are not implemented.                                                                                                                                                               |

| [23]    | FIFOFULL logic present           | The value of this bit is 1, indicating that <b>FIFOFULL</b> logic is present in the ETM.<br>To use FIFOFULL the system must also support the function, as indicated by bit<br>[8] of ETMSCR, see <i>System Configuration Register, ETMSCR</i> on page 3-9. |

| [22:20] | Number of external outputs       | The value of these bits is 0b000, indicating that no external outputs are supported.                                                                                                                                                                       |

| [19:17] | Number of external inputs        | The value of these bits is between 0b000 and 0b010, indicating the number of external inputs, from 0 to 2, implemented in the system.                                                                                                                      |

| [16]    | Sequencer present                | The value of this bit is 0, indicating that the sequencer is not implemented.                                                                                                                                                                              |

#### Table 3-3 ETMCCR bit assignments (continued)

| Bits    | Name                               | Function                                                                                           |

|---------|------------------------------------|----------------------------------------------------------------------------------------------------|

| [15:13] | Number of counters                 | The value of these bits is 0b001, indicating that one counter is implemented.                      |

| [12:8]  | Number of memory map decoders      | The value of these bits is 0b00000, indicating that memory map decoder inputs are not implemented. |

| [7:4]   | Number of data value comparators   | The value of these bits is 0b0000, indicating that data value comparators are not implemented.     |

| [3:0]   | Number of address comparator pairs | The value of these bits is 0b0000, indicating that address comparator pairs are not implemented.   |

#### 3.4.3 System Configuration Register, ETMSCR

The ETMSCR characteristics are:

| Purpose           | Shows the ETM features supported by the implementation of the ETM macrocell.   |

|-------------------|--------------------------------------------------------------------------------|

| Usage constraints | There are no usage constraints.                                                |

| Configurations    | This register is only available if the processor is configured to use the ETM. |

| Attributes        | See the register summary in Table 3-1 on page 3-4.                             |

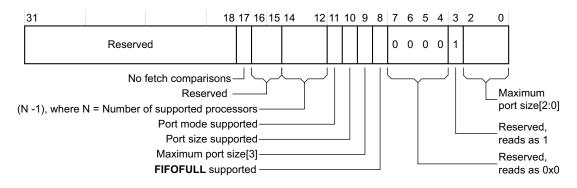

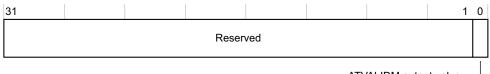

Figure 3-3 shows the ETMSCR bit assignments.

Figure 3-3 ETMSCR bit assignments

Table 3-4 shows the ETMSCR bit assignments.

#### Table 3-4 ETMSCR bit assignments

| Bits    | Name                 | Function                                                                                                                                             |

|---------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| [31:18] | -                    | Reserved.                                                                                                                                            |

| [17]    | No Fetch comparisons | The value of this bit is 1, indicating that fetch comparisons are not implemented.                                                                   |

| [16:15] | -                    | Reserved.                                                                                                                                            |

| [14:12] | (N-1)                | These bits give the number of supported processors minus 1. The value of these bits is 0b000, indicating that there is only one processor connected. |

| [11]    | Port mode supported  | This bit reads as 1 if the currently selected port mode is supported. This has no effect on the TPIU trace port.                                     |

#### Table 3-4 ETMSCR bit assignments (continued)

| Bits  | Name                    | Function                                                                                                                                   |

|-------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| [10]  | Port size supported     | This bit reads as 1 if the currently selected port size is supported. This has no effect on the TPIU trace port.                           |

| [9]   | Maximum port size [3]   | Maximum ETM port size bit [3]. This bit is used in conjunction with bits [2:0]. Its value is 0. This has no effect on the TPIU trace port. |

| [8]   | FIFOFULL supported      | The value of this bit is 1, indicating that <b>FIFOFULL</b> is supported. This bit is used in conjunction with bit [23] of the ETMCCR.     |

| [7:4] | -                       | Reserved, Read-As-Zero.                                                                                                                    |

| [3]   | -                       | Reserved, Read-As-One.                                                                                                                     |

| [2:0] | Maximum port size [2:0] | Maximum ETM port size bits [2:0]. These bits are used in conjunction with bit [9]. The value of these bits is 0b001.                       |

#### 3.4.4 TraceEnable Control 1 Register, ETMTECR1

The ETMTECR1 characteristics are:

Usage constraints There are no usage constraints.

| Configurations | This register is only available if the processor is configured to use the |

|----------------|---------------------------------------------------------------------------|

|                | ETM.                                                                      |

|                |                                                                           |

| Attributes | See the register summary | in Table 3-1 on page 3-4. |

|------------|--------------------------|---------------------------|

|------------|--------------------------|---------------------------|

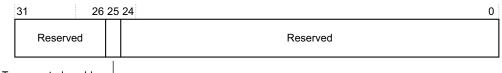

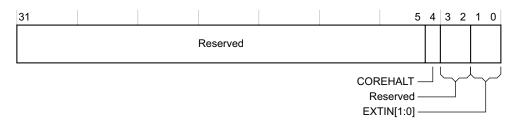

Figure 3-4 shows the ETMTECR1 bit assignments.

#### Figure 3-4 ETMTECR1 bit assignments

Table 3-5 shows the ETMTECR1 bit assignments.

#### Table 3-5 ETMTECR1 bit assignments

| Bits    | Name                 | Function                                                                                             |  |

|---------|----------------------|------------------------------------------------------------------------------------------------------|--|

| [31:26] | -                    | Reserved.                                                                                            |  |

| [25]    | Trace control enable | Trace start/stop enable. The possible values of this bit are:                                        |  |

|         |                      | 0 Tracing is unaffected by the trace start/stop logic.                                               |  |

|         |                      | 1 Tracing is controlled by the trace on and off addresses configured for the trace start/stop logic. |  |

|         |                      | The trace start/stop resource, resource 0x5F, is unaffected by the value of this bit.                |  |

| [24:0]  | -                    | Reserved.                                                                                            |  |

#### 3.4.5 ID Register, ETMIDR

The ETMIDR characteristics are:

| Purpose           | Holds the ETM architecture variant, and defines the programmers model for the ETM. |

|-------------------|------------------------------------------------------------------------------------|

| Usage constraints | There are no usage constraints.                                                    |

| Configurations    | This register is only available if the processor is configured to use the ETM.     |

Attributes See the register summary in Table 3-1 on page 3-4.

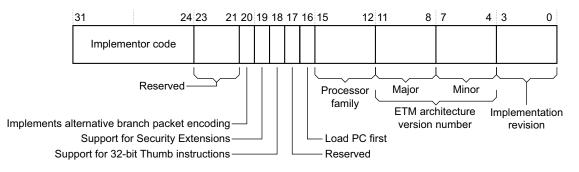

Figure 3-5 shows the ETMIDR bit assignments.

#### Figure 3-5 ETMIDR bit assignments

Table 3-6 shows the ETMIDR bit assignments.

#### Table 3-6 ETMIDR bit assignments

| Bits    | Name                             | Function                                                                                                         |

|---------|----------------------------------|------------------------------------------------------------------------------------------------------------------|

| [31:24] | Implementer code                 | These bits identify ARM as the implementer of the processor. The value of these bits is 0b1000001.               |

| [23:21] | -                                | Reserved.                                                                                                        |

| [20]    | Branch packet encoding           | The value of this bit is 1, indicating that alternative branch packet encoding is implemented.                   |

| [19]    | Security Extensions support      | The value of this bit is 0, indicating that the ETM behaves as if the processor is in Secure state at all times. |

| [18]    | 32-bit Thumb instruction tracing | The value of this bit is 1, indicating that a 32-bit Thumb instruction is traced as a single instruction.        |

| [17]    | -                                | Reserved.                                                                                                        |

| [16]    | Load PC first                    | The value of this bit is 0, indicating that data tracing is not supported.                                       |

| [15:12] | Processor family                 | The value of these bits is 0b1111, indicating that the processor family is not identified in this register.      |

| [11:8]  | Major ETM architecture version   | The value of these bits is 0b0010, indicating major architecture version number 3, ETMv3.                        |

| [7:4]   | Minor ETM architecture version   | The value of these bits is 0b0101, indicating minor architecture version number 5.                               |

| [3:0]   | Implementation revision          | The value of these bits is 0b0000, indicating implementation revision, 0.                                        |

#### 3.4.6 Configuration Code Extension Register, ETMCCER

The ETMCCER characteristics are:

| Purpose           | Holds ETM configuration information additional to that in the ETMCCR.<br>See <i>Configuration Code Register, ETMCCR</i> on page 3-8. |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| Usage constraints | There are no usage constraints.                                                                                                      |

| Configurations    | This register is only available if the processor is configured to use the ETM.                                                       |

Attributes See the register summary in Table 3-1 on page 3-4.

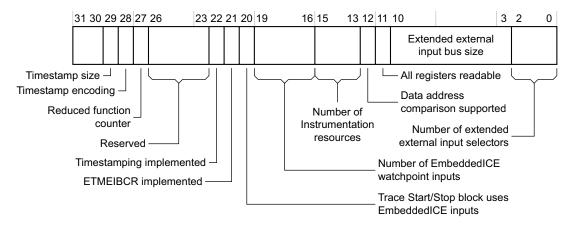

Figure 3-6 shows the ETMCCER bit assignments.

#### Figure 3-6 ETMCCER bit assignments

#### Table 3-7 shows the ETMCCER bit assignments.

#### Table 3-7 ETMCCER bit assignments

| Bits    | Name                                                            | Function                                                                                                                                                                                       |

|---------|-----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [31:30] | -                                                               | Reserved. Read-As-Zero.                                                                                                                                                                        |

| [29]    | Timestamp size                                                  | Set to 0 to indicate a size of 48 bits.                                                                                                                                                        |

| [28]    | Timestamp encoding                                              | Set to 1 to indicate that the timestamp is encoded as a natural binary number.                                                                                                                 |

| [27]    | Reduced function counter                                        | Set to 1 to indicate that Counter 1 is a reduced function counter.                                                                                                                             |