# Intel<sup>®</sup> MAX<sup>®</sup> 10 High-Speed LVDS I/O User Guide

Updated for Intel<sup>®</sup> Quartus<sup>®</sup> Prime Design Suite: **17.1**

## Contents

| 1 Intel <sup>®</sup> MAX <sup>®</sup> 10 High-Speed LVDS I/O Overview                                                                                                                                                  | . 4                                                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| 1.1 Altera Soft LVDS Implementation Overview                                                                                                                                                                           | 4                                                                                                 |

| 2 Intel MAX 10 High-Speed LVDS Architecture and Features                                                                                                                                                               | . 6                                                                                               |

| <ul> <li>2.1 Intel MAX 10 LVDS Channels Support</li></ul>                                                                                                                                                              | 6<br>11<br>12<br>.13                                                                              |

| 3 Intel MAX 10 LVDS Transmitter Design                                                                                                                                                                                 | 16                                                                                                |

| <ul> <li>3.1 High-Speed I/O Transmitter Circuitry</li></ul>                                                                                                                                                            | 16<br>16<br>17<br>.18<br>18<br>.18<br>.19<br>20<br>20<br>23<br>.23<br>.24<br>24<br>24<br>25<br>25 |

| 4 Intel MAX 10 LVDS Receiver Design.                                                                                                                                                                                   |                                                                                                   |

| 4.1 High-Speed I/O Receiver Circuitry                                                                                                                                                                                  | 26                                                                                                |

| <ul> <li>4.1.1 Soft Deserializer</li> <li>4.1.2 Data Realignment Block (Bit Slip)</li> <li>4.2 LVDS Receiver I/O Termination Schemes</li> <li>4.2.1 LVDS, Mini-LVDS, and RSDS Receiver External Termination</li> </ul> | .27<br>.27                                                                                        |

| <ul><li>4.2.2 SLVS Receiver External Termination</li><li>4.2.3 Sub-LVDS Receiver External Termination</li><li>4.2.4 TMDS Receiver External Termination</li></ul>                                                       | .28<br>.28<br>.29                                                                                 |

| 4.2.5 HiSpi Receiver External Termination<br>4.2.6 LVPECL External Termination<br>4.3 LVDS Receiver FPGA Design Implementation                                                                                         | 30                                                                                                |

| 4.3.1 Altera Soft LVDS IP Core in Receiver Mode<br>4.3.2 High-Speed I/O Timing Budget<br>4.3.3 Guidelines: Floating LVDS Input Pins                                                                                    | 31<br>34                                                                                          |

| 4.3.4 Guidelines: LVDS Receiver Channels Placement                                                                                                                                                                     |                                                                                                   |

| 4.3.5 Guidelines: LVDS Channels PLL Placement           |              |

|---------------------------------------------------------|--------------|

| 4.3.6 Guidelines: LVDS Receiver Logic Placement         |              |

| 4.4 LVDS Receiver Debug and Troubleshooting             |              |

| 4.4.1 Perform RTL Simulation Before Hardware Deb        | Jg 39        |

| 4.4.2 Geometry-Based and Physics-Based I/O Rules        |              |

| 5 Intel MAX 10 LVDS Transmitter and Receiver Design     | 40           |

| 5.1 Transmitter-Receiver Interfacing                    | 40           |

| 5.2 LVDS Transmitter and Receiver FPGA Design Implemer  |              |

| 5.2.1 LVDS Transmitter and Receiver PLL Sharing In      | plementation |

| 5.2.2 Initializing the Altera Soft LVDS IP Core         |              |

| 5.3 LVDS Transmitter and Receiver Debug and Troubleshoo | ting 42      |

| 5.3.1 Perform RTL Simulation Before Hardware Deb        | Jg 42        |

| 5.3.2 Geometry-Based and Physics-Based I/O Rules        |              |

| 6 Intel MAX 10 High-Speed LVDS Board Design Considerat  | ons          |

| 6.1 Guidelines: Improve Signal Quality                  |              |

| 6.2 Guidelines: Control Channel-to-Channel Skew         |              |

| 6.3 Guidelines: Determine Board Design Constraints      |              |

| 6.4 Guidelines: Perform Board Level Simulations         |              |

| 7 Altera Soft LVDS IP Core References                   | 46           |

| 7.1 Altera Soft LVDS Parameter Settings                 |              |

| 7.2 Altera Soft LVDS Interface Signals                  |              |

| 8 Intel MAX 10 High-Speed LVDS I/O User Guide Archives. | 52           |

|                                                         |              |

| 9 Document Revision History for Intel MAX 10 High-Speed |              |

## **1** Intel<sup>®</sup> MAX<sup>®</sup> **10** High-Speed LVDS I/O Overview

The Intel<sup>®</sup> MAX<sup>®</sup> 10 device family supports high-speed LVDS protocols through the LVDS I/O banks and the Altera Soft LVDS IP core.

The LVDS I/O banks in Intel MAX 10 devices feature true and emulated LVDS buffers:

- True LVDS buffers support LVDS using true differential buffers.

- Emulated LVDS buffers use a pair of single-ended pins to emulate differential buffers.

#### Table 1. Summary of LVDS I/O Buffers Support in Intel MAX 10 I/O Banks

| I/O Buffer Type             | I/O Bank Support      |

|-----------------------------|-----------------------|

| True LVDS input buffer      | All I/O banks         |

| True LVDS output buffer     | Only bottom I/O banks |

| Emulated LVDS output buffer | All I/O banks         |

The Intel MAX 10 D (dual supply) and S (single supply) device variants support different LVDS I/O standards. For a list of LVDS I/O standards supported by the Intel MAX 10 D and S variants, refer to the related information.

#### **Related Links**

- Intel MAX 10 High-Speed LVDS Architecture and Features on page 6

Provides information about the high-speed LVDS architecture and the features

supported by the device.

- Altera Soft LVDS IP Core References on page 46

Lists the parameters and signals of Altera Soft LVDS IP core for Intel MAX 10 devices.

- Intel MAX 10 LVDS SERDES I/O Standards Support on page 11 Lists the supported LVDS I/O standards and the support in different Intel MAX 10 device variants.

- Intel MAX 10 High-Speed LVDS I/O User Guide Archives on page 52

Provides a list of user guides for previous versions of the Altera Soft LVDS IP

core.

## **1.1 Altera Soft LVDS Implementation Overview**

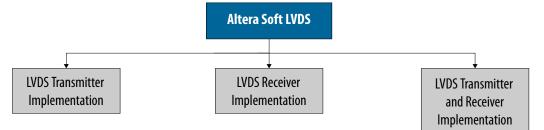

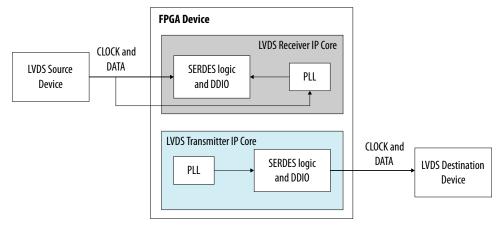

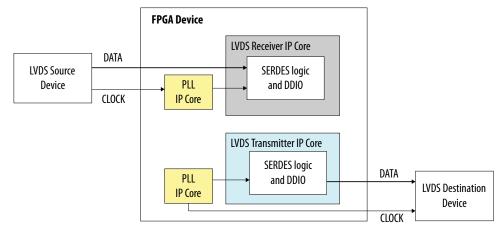

You can implement LVDS applications in Intel MAX 10 devices as transmitter-only, receiver-only, or a combination of transmitters and receivers.

Intel Corporation. All rights reserved. Intel, the Intel logo, Altera, Arria, Cyclone, Enpirion, MAX, Nios, Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

#### Figure 1. Intel MAX 10 LVDS Implementation Overview

#### **Related Links**

- Intel MAX 10 LVDS Transmitter Design on page 16 Provides information and guidelines for implementing LVDS transmitter in Intel MAX 10 devices using the Altera Soft LVDS IP core.

- Intel MAX 10 LVDS Receiver Design on page 26 Provides information and guidelines for implementing LVDS receiver in Intel MAX 10 devices using the Altera Soft LVDS IP core.

- Intel MAX 10 LVDS Transmitter and Receiver Design on page 40 Provides design guidelines for implementing both LVDS transmitters and receivers in the same Intel MAX 10 device.

# 2 Intel MAX 10 High-Speed LVDS Architecture and Features

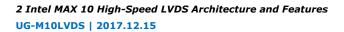

The Intel MAX 10 devices use registers and logic in the core fabric to implement LVDS input and output interfaces.

- For LVDS transmitters and receivers, Intel MAX 10 devices use the the double data rate I/O (DDIO) registers that reside in the I/O elements (IOE). This architecture improves performance with regards to the receiver input skew margin (RSKM) or transmitter channel-to-channel skew (TCCS).

- For the LVDS serializer/deserializer (SERDES), Intel MAX 10 devices use logic elements (LE) registers.

## 2.1 Intel MAX 10 LVDS Channels Support

The LVDS channels available vary among Intel MAX 10 devices. All I/O banks in Intel MAX 10 devices support true LVDS input buffers and emulated LVDS output buffers. However, only the bottom I/O banks support true LVDS output buffers.

#### Table 2.LVDS Buffers in Intel MAX 10 Devices

This table lists the LVDS buffer support for I/O banks on each side of the devices.

| Product Line | Package | Device Power | Side   | True LVI | DS Pairs | Emulated   |

|--------------|---------|--------------|--------|----------|----------|------------|

|              |         | Supply       |        | тх       | RX       | LVDS Pairs |

| 10M02        | V36     | Dual         | Тор    | 0        | 1        | 1          |

|              |         |              | Right  | 0        | 3        | 3          |

|              |         |              | Left   | 0        | 3        | 3          |

|              |         |              | Bottom | 3        | 3        | 3          |

| -            | M153    | Single       | Тор    | 0        | 12       | 12         |

|              |         |              | Right  | 0        | 12       | 12         |

|              |         |              | Left   | 0        | 12       | 12         |

|              |         |              | Bottom | 9        | 13       | 13         |

| -            | U169    | Single       | Тор    | 0        | 12       | 12         |

|              |         |              | Right  | 0        | 17       | 17         |

|              |         |              | Left   | 0        | 15       | 15         |

|              |         |              | Bottom | 9        | 14       | 14         |

| -            | U324    | Single       | Тор    | 0        | 27       | 27         |

|              |         |              | Right  | 0        | 31       | 31         |

|              |         |              | Left   | 0        | 28       | 28         |

|              |         |              |        |          |          | continued  |

Intel Corporation. All rights reserved. Intel, the Intel logo, Altera, Arria, Cyclone, Enpirion, MAX, Nios, Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

\*Other names and brands may be claimed as the property of others.

| Product Line | Package | e Device Power<br>Supply | Side Tru |    | True LVDS Pairs |            |  |

|--------------|---------|--------------------------|----------|----|-----------------|------------|--|

|              |         |                          |          | ТХ | RX              | LVDS Pairs |  |

|              |         |                          | Bottom   | 15 | 28              | 28         |  |

|              |         | Dual                     | Тор      | 0  | 13              | 13         |  |

|              |         |                          | Right    | 0  | 24              | 24         |  |

|              |         |                          | Left     | 0  | 20              | 20         |  |

|              |         |                          | Bottom   | 9  | 16              | 16         |  |

|              | E144    | Single                   | Тор      | 0  | 10              | 10         |  |

|              |         |                          | Right    | 0  | 12              | 12         |  |

|              |         |                          | Left     | 0  | 11              | 11         |  |

|              |         |                          | Bottom   | 7  | 12              | 12         |  |

| 10M04        | M153    | Single                   | Тор      | 0  | 12              | 12         |  |

|              |         |                          | Right    | 0  | 12              | 12         |  |

|              |         |                          | Left     | 0  | 12              | 12         |  |

|              |         |                          | Bottom   | 9  | 13              | 13         |  |

|              | U169    | Single                   | Тор      | 0  | 12              | 12         |  |

| U324         |         | Right                    | 0        | 17 | 17              |            |  |

|              |         | Left                     | 0        | 15 | 15              |            |  |

|              |         | Bottom                   | 9        | 14 | 14              |            |  |

|              | Single  | Тор                      | 0        | 27 | 27              |            |  |

|              |         |                          | Right    | 0  | 31              | 31         |  |

|              |         |                          | Left     | 0  | 28              | 28         |  |

|              |         |                          | Bottom   | 15 | 28              | 28         |  |

|              |         | Dual                     | Тор      | 0  | 27              | 27         |  |

|              |         |                          | Right    | 0  | 31              | 31         |  |

|              |         |                          | Left     | 0  | 28              | 28         |  |

|              |         |                          | Bottom   | 15 | 28              | 28         |  |

| -            | F256    | Dual                     | Тор      | 0  | 19              | 19         |  |

|              |         |                          | Right    | 0  | 22              | 22         |  |

|              |         |                          | Left     | 0  | 19              | 19         |  |

|              |         |                          | Bottom   | 13 | 20              | 20         |  |

| -            | E144    | Single                   | Тор      | 0  | 8               | 8          |  |

|              |         |                          | Right    | 0  | 12              | 12         |  |

|              |         |                          | Left     | 0  | 11              | 11         |  |

|              |         |                          | Bottom   | 10 | 10              | 10         |  |

| 10M08        | V81     | Dual                     | Тор      | 0  | 5               | 5          |  |

|              |         |                          | Right    | 0  | 7               | 7          |  |

|              |         |                          |          | l  | 1               | continued  |  |

| Product Line | Package | Device Power | Side   | True LV | DS Pairs | Emulated   |

|--------------|---------|--------------|--------|---------|----------|------------|

|              |         | Supply       |        | тх      | RX       | LVDS Pairs |

|              |         |              | Left   | 0       | 6        | 6          |

|              |         |              | Bottom | 7       | 7        | 7          |

|              | M153    | Single       | Тор    | 0       | 12       | 12         |

|              |         |              | Right  | 0       | 12       | 12         |

|              |         |              | Left   | 0       | 12       | 12         |

|              |         |              | Bottom | 9       | 13       | 13         |

|              | U169    | Single       | Тор    | 0       | 12       | 12         |

|              |         |              | Right  | 0       | 17       | 17         |

|              |         |              | Left   | 0       | 15       | 15         |

|              |         |              | Bottom | 9       | 14       | 14         |

|              | U324    | Single       | Тор    | 0       | 27       | 27         |

|              |         |              | Right  | 0       | 31       | 31         |

|              |         |              | Left   | 0       | 28       | 28         |

|              |         |              | Bottom | 15      | 28       | 28         |

|              |         | Dual         | Тор    | 0       | 27       | 27         |

|              |         |              | Right  | 0       | 31       | 31         |

|              |         |              | Left   | 0       | 28       | 28         |

|              |         |              | Bottom | 15      | 28       | 28         |

|              | F256    | Dual         | Тор    | 0       | 19       | 19         |

|              |         |              | Right  | 0       | 22       | 22         |

|              |         |              | Left   | 0       | 19       | 19         |

|              |         |              | Bottom | 13      | 20       | 20         |

|              | E144    | Single       | Тор    | 0       | 8        | 8          |

|              |         |              | Right  | 0       | 12       | 12         |

|              |         |              | Left   | 0       | 11       | 11         |

|              |         |              | Bottom | 10      | 10       | 10         |

|              | F484    | Dual         | Тор    | 0       | 27       | 27         |

|              |         |              | Right  | 0       | 33       | 33         |

|              |         |              | Left   | 0       | 28       | 28         |

|              |         |              | Bottom | 15      | 28       | 28         |

| 10M16        | U169    | Single       | Тор    | 0       | 12       | 12         |

|              |         |              | Right  | 0       | 17       | 17         |

|              |         |              | Left   | 0       | 15       | 15         |

|              |         |              | Bottom | 9       | 14       | 14         |

|              | U324    | Single       | Тор    | 0       | 27       | 27         |

| Product Line | Package | Device Power<br>Supply |        |    | True LVDS Pairs |            |  |

|--------------|---------|------------------------|--------|----|-----------------|------------|--|

|              |         |                        |        | тх | RX              | LVDS Pairs |  |

|              |         |                        | Right  | 0  | 31              | 31         |  |

|              |         |                        | Left   | 0  | 28              | 28         |  |

|              |         |                        | Bottom | 15 | 28              | 28         |  |

|              |         | Dual                   | Тор    | 0  | 27              | 27         |  |

|              |         |                        | Right  | 0  | 31              | 31         |  |

|              |         |                        | Left   | 0  | 28              | 28         |  |

|              |         |                        | Bottom | 15 | 28              | 28         |  |

|              | F256    | Dual                   | Тор    | 0  | 19              | 19         |  |

|              |         |                        | Right  | 0  | 22              | 22         |  |

|              |         |                        | Left   | 0  | 19              | 19         |  |

|              |         |                        | Bottom | 13 | 20              | 20         |  |

|              | E144    | Single                 | Тор    | 0  | 8               | 8          |  |

|              |         |                        | Right  | 0  | 12              | 12         |  |

|              |         |                        | Left   | 0  | 11              | 11         |  |

|              |         |                        | Bottom | 10 | 10              | 10         |  |

|              | F484    | Dual                   | Тор    | 0  | 39              | 39         |  |

|              |         |                        | Right  | 0  | 38              | 38         |  |

|              |         |                        | Left   | 0  | 32              | 32         |  |

|              |         |                        | Bottom | 22 | 42              | 42         |  |

| 10M25        | F256    | Dual                   | Тор    | 0  | 19              | 19         |  |

|              |         |                        | Right  | 0  | 22              | 22         |  |

|              |         |                        | Left   | 0  | 19              | 19         |  |

|              |         |                        | Bottom | 13 | 20              | 20         |  |

|              | E144    | Single                 | Тор    | 0  | 8               | 8          |  |

|              |         |                        | Right  | 0  | 12              | 12         |  |

|              |         |                        | Left   | 0  | 11              | 11         |  |

|              |         |                        | Bottom | 10 | 10              | 10         |  |

|              | F484    | Dual                   | Тор    | 0  | 41              | 41         |  |

|              |         |                        | Right  | 0  | 48              | 48         |  |

|              |         | Γ                      | Left   | 0  | 36              | 36         |  |

|              |         | Ē                      | Bottom | 24 | 46              | 46         |  |

| 10M40        | F256    | Dual                   | Тор    | 0  | 19              | 19         |  |

|              |         |                        | Right  | 0  | 22              | 22         |  |

|              |         | ļ Ē                    | Left   | 0  | 19              | 19         |  |

|              |         |                        | Bottom | 13 | 20              | 20         |  |

| Product Line | Package | Device Power | Side   | True LVI | DS Pairs | Emulated   |

|--------------|---------|--------------|--------|----------|----------|------------|

|              |         | Supply       |        | тх       | RX       | LVDS Pairs |

|              | E144    | Single       | Тор    | 0        | 9        | 9          |

|              |         |              | Right  | 0        | 12       | 12         |

|              |         |              | Left   | 0        | 11       | 11         |

|              |         |              | Bottom | 10       | 10       | 10         |

|              | F484    | Dual         | Тор    | 0        | 41       | 41         |

|              |         |              | Right  | 0        | 48       | 48         |

|              |         |              | Left   | 0        | 36       | 36         |

|              |         |              | Bottom | 24       | 46       | 46         |

|              | F672    | Dual         | Тор    | 0        | 53       | 53         |

|              |         |              | Right  | 0        | 70       | 70         |

|              |         |              | Left   | 0        | 60       | 60         |

|              |         |              | Bottom | 30       | 58       | 58         |

| 10M50        | F256    | Dual         | Тор    | 0        | 19       | 19         |

|              |         |              | Right  | 0        | 22       | 22         |

|              |         |              | Left   | 0        | 19       | 19         |

|              |         |              | Bottom | 13       | 20       | 20         |

|              | E144    | Single       | Тор    | 0        | 9        | 9          |

|              |         |              | Right  | 0        | 12       | 12         |

|              |         |              | Left   | 0        | 11       | 11         |

|              |         |              | Bottom | 10       | 10       | 10         |

|              | F484    | Dual         | Тор    | 0        | 41       | 41         |

|              |         |              | Right  | 0        | 48       | 48         |

|              |         |              | Left   | 0        | 36       | 36         |

|              |         |              | Bottom | 24       | 46       | 46         |

|              | F672    | Dual         | Тор    | 0        | 53       | 53         |

|              |         |              | Right  | 0        | 70       | 70         |

|              |         |              | Left   | 0        | 60       | 60         |

|              |         |              | Bottom | 30       | 58       | 58         |

#### **Related Links**

- Intel MAX 10 Device Pin-Out Files Provides pin-out files for each Intel MAX 10 device.

- Intel MAX 10 High-Speed LVDS I/O Location on page 13

## 2.2 Intel MAX 10 LVDS SERDES I/O Standards Support

The Intel MAX 10 D and S device variants support different LVDS I/O standards. All I/O banks in Intel MAX 10 devices support true LVDS input buffers and emulated LVDS output buffers. However, only the bottom I/O banks support true LVDS output buffers.

#### Table 3. Intel MAX 10 LVDS I/O Standards Support

Single and dual supply Intel MAX 10 devices support different I/O standards. For more information about single and dual supply devices, refer to the device overview.

| I/O Standard                            | I/O Bank | тх                      | RX  | Intel MAX<br>Sup         |                            | Notes                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------------------------------|----------|-------------------------|-----|--------------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                         |          |                         |     | Dual<br>Supply<br>Device | Single<br>Supply<br>Device |                                                                                                                                                                                                                                                                                                                                                                                                                 |

| True LVDS                               | All      | Bottom<br>banks<br>only | Yes | Yes                      | Yes                        | <ul> <li>All I/O banks support true LVDS input buffers.</li> <li>Only the bottom I/O banks support true LVDS output buffers.</li> </ul>                                                                                                                                                                                                                                                                         |

| Emulated LVDS (three resistors)         | All      | Yes                     | —   | Yes                      | Yes                        | All I/O banks support emulated LVDS output buffers.                                                                                                                                                                                                                                                                                                                                                             |

| True RSDS                               | Bottom   | Yes                     | -   | Yes                      | Yes                        | _                                                                                                                                                                                                                                                                                                                                                                                                               |

| Emulated RSDS<br>(single resistor)      | All      | Yes                     | -   | Yes                      | _                          | All I/O banks support emulated RSDS output buffers.                                                                                                                                                                                                                                                                                                                                                             |

| Emulated RSDS (three resistors)         | All      | Yes                     | -   | Yes                      | Yes                        | All I/O banks support emulated RSDS output buffers.                                                                                                                                                                                                                                                                                                                                                             |

| True Mini-LVDS                          | Bottom   | Yes                     | -   | Yes                      | —                          | —                                                                                                                                                                                                                                                                                                                                                                                                               |

| Emulated Mini-LVDS<br>(three resistors) | All      | Yes                     | _   | Yes                      | _                          | All I/O banks support emulated<br>Mini-LVDS output buffers.                                                                                                                                                                                                                                                                                                                                                     |

| PPDS                                    | Bottom   | Yes                     | _   | Yes                      | —                          | _                                                                                                                                                                                                                                                                                                                                                                                                               |

| Emulated PPDS (three resistors)         | All      | Yes                     | _   | Yes                      | —                          | _                                                                                                                                                                                                                                                                                                                                                                                                               |

| Bus LVDS                                | All      | Yes                     | Yes | Yes                      | Yes                        | <ul> <li>Bus LVDS (BLVDS) output uses<br/>two single-ended outputs with<br/>the second output programmed<br/>as inverted.</li> <li>BLVDS input uses LVDS input<br/>buffer.</li> <li>You can tristate BLVDS output.</li> </ul>                                                                                                                                                                                   |

| LVPECL                                  | All      | _                       | Yes | Yes                      | Yes                        | Supported only on dual function clock input pins.                                                                                                                                                                                                                                                                                                                                                               |

| TMDS                                    | All      | _                       | Yes | Yes                      | _                          | <ul> <li>Requires external termination<br/>but does not require V<sub>REF</sub>.</li> <li>Requires external level shifter<br/>to support 3.3 V TMDS input.<br/>This level shifter must convert<br/>the TMDS signal from AC-<br/>coupled to DC-coupled before<br/>you connect it to the Intel MAX<br/>10 input buffer.</li> <li>TMDS receiver support uses<br/>dedicated 2.5 V LVDS input<br/>buffer.</li> </ul> |

|                                         |          |                         |     |                          |                            | continued                                                                                                                                                                                                                                                                                                                                                                                                       |

| I/O Standard | I/O Bank | тх  | RX  | Intel MAX 10 Device<br>Support |                            | Notes                                                                                                                                                                                                                                                                                                            |

|--------------|----------|-----|-----|--------------------------------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              |          |     |     | Dual<br>Supply<br>Device       | Single<br>Supply<br>Device | -                                                                                                                                                                                                                                                                                                                |

| Sub-LVDS     | All      | Yes | Yes | Yes                            | _                          | <ul> <li>Transmitter supports only<br/>emulated Sub-LVDS using<br/>emulated 1.8 V differential<br/>signal as output.</li> <li>Requires external output<br/>termination.</li> <li>Does not require V<sub>REF</sub>.</li> <li>Sub-LVDS receiver support<br/>uses dedicated 2.5 V LVDS<br/>input buffer.</li> </ul> |

| SLVS         | All      | Yes | Yes | Yes                            | _                          | <ul> <li>SLVS transmitter support uses<br/>emulated LVDS output.</li> <li>Requires external termination<br/>but does not require V<sub>REF</sub>.</li> <li>SLVS receiver support uses<br/>dedicated 2.5 V LVDS input<br/>buffer.</li> </ul>                                                                      |

| HiSpi        | All      | _   | Yes | Yes                            | _                          | <ul> <li>Only input is supported<br/>because HiSpi is a<br/>unidirectional I/O standard.</li> <li>Requires external termination<br/>but does not require V<sub>REF</sub>.</li> <li>HiSpi receiver support uses<br/>dedicated 2.5 V LVDS input<br/>buffer.</li> </ul>                                             |

#### **Related Links**

- Intel MAX 10 FPGA Device Overview

- Emulated LVDS External Termination on page 18

- Emulated RSDS, Emulated Mini-LVDS, and Emulated PPDS Transmitter External Termination on page 19

- TMDS Receiver External Termination on page 29

- Sub-LVDS Transmitter External Termination on page 18

- Sub-LVDS Receiver External Termination on page 28

- SLVS Transmitter External Termination on page 19

- SLVS Receiver External Termination on page 28

- HiSpi Receiver External Termination on page 29

## 2.3 Intel MAX 10 High-Speed LVDS Circuitry

The LVDS solution uses the I/O elements and registers in the Intel MAX 10 devices. The Altera Soft LVDS IP core implements the serializer and deserializer as soft SERDES blocks in the core logic.

The Intel MAX 10 devices do not contain dedicated serialization or deserialization circuitry:

- You can use I/O pins and core fabric to implement a high-speed differential interface in the device.

- The Intel MAX 10 solution uses shift registers, internal PLLs, and I/O elements to perform the serial-to-parallel and parallel-to-serial conversions of incoming and outgoing data.

- The Intel Quartus<sup>®</sup> Prime software uses the parameter settings of the Altera Soft LVDS IP core to automatically construct the differential SERDES in the core fabric.

#### Figure 2. Soft LVDS SERDES

This figure shows a transmitter and receiver block diagram for the soft LVDS SERDES circuitry with the interface signals of the transmitter and receiver data paths.

#### **Related Links**

Intel MAX 10 Clocking and PLL User Guide Provides more information about the PLL and the PLL output counters.

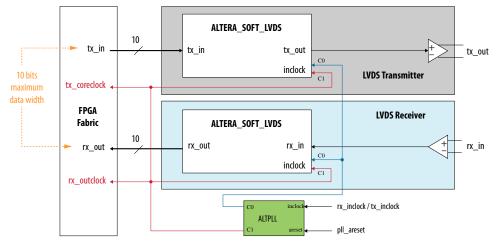

## 2.4 Intel MAX 10 High-Speed LVDS I/O Location

The I/O banks in Intel MAX 10 devices support true LVDS input and emulated LVDS output on all I/O banks. Only the bottom I/O banks support true LVDS output.

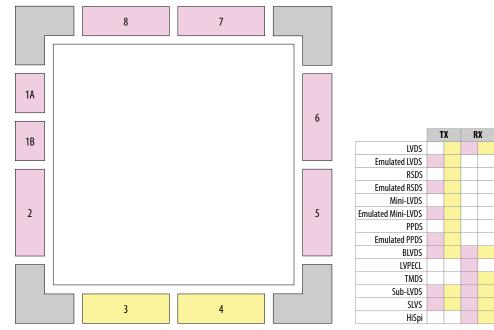

## Figure 3. LVDS Support in I/O Banks of 10M02 Devices (Except Single Power Supply U324 Package)

This figure shows a top view of the silicon die. Each bank is labeled with the actual bank number. LVPECL support only in banks 2 and 6.

## Figure 4. LVDS Support in I/O Banks of 10M02 (Single Power Supply U324 Package), 10M04, and 10M08 Devices

This figure shows a top view of the silicon die. Each bank is labeled with the actual bank number. LVPECL support only in banks 2 and 6.

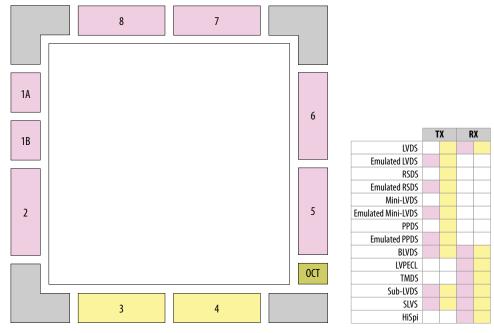

#### Figure 5. LVDS Support in I/O Banks of 10M16, 10M25, 10M40, and 10M50 Devices

This figure shows a top view of the silicon die. Each bank is labeled with the actual bank number. LVPECL support only in banks 2, 3, 6, and 8.

#### **Related Links**

- PLL Specifications Provides PLL performance information for Intel MAX 10 devices.

- High-Speed I/O Specifications

Provides minimum and maximum data rates for different data widths in Intel MAX 10 devices.

## 2.5 Differential I/O Pins in Low Speed Region

Some of the differential I/O pins are located in the low speed region of the Intel MAX 10 device.

- For each user I/O pin (excluding configuration pin) that you place in the low speed region, the Intel Quartus Prime software generates an informational warning message.

- Refer to the device pinout to identify the low speed I/O pins.

- Refer to the device datasheet for the performance information of these I/O pins.

#### **Related Links**

- Intel MAX 10 Device Pin-Out Files Provides pin-out files for each Intel MAX 10 device.

- Intel MAX 10 Device Datasheet

- MAX 10 I/O Banks Locations, MAX 10 General Purpose I/O User Guide Shows the locations of the high speed and low speed I/O banks.

## **3 Intel MAX 10 LVDS Transmitter Design**

You can implement transmitter-only applications using the Intel MAX 10 LVDS solution. You can use the Altera Soft LVDS IP core to instantiate soft SERDES circuitry. The soft SERDES circuitry works with the clocks and differential I/O pins to create a high-speed differential transmitter circuit.

## 3.1 High-Speed I/O Transmitter Circuitry

The LVDS transmitter circuitry uses the I/O elements and registers in the Intel MAX 10 devices. The Altera Soft LVDS IP core implements the serializer as a soft SERDES block in the core logic.

#### **Related Links**

Intel MAX 10 High-Speed LVDS Circuitry on page 12

## **3.2 LVDS Transmitter Programmable I/O Features**

You can program some features of the I/O buffers and pins in Intel MAX 10 devices according to your design requirements. For high-speed LVDS transmitter applications, you can program the pre-emphasis setting.

#### 3.2.1 Programmable Pre-Emphasis

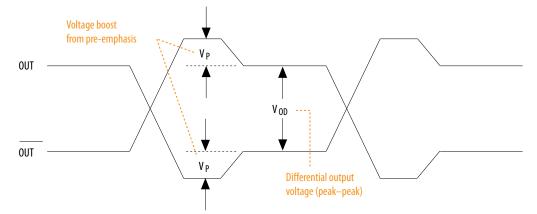

The differential output voltage ( $V_{OD}$ ) setting and the output impedance of the driver set the output current limit of a high-speed transmission signal. At a high frequency, the slew rate may not be fast enough to reach the full  $V_{OD}$  level before the next edge, producing pattern-dependent jitter. Pre-emphasis momentarily boosts the output current during switching to increase the output slew rate.

Pre-emphasis increases the amplitude of the high-frequency component of the output signal. This increase compensates for the frequency-dependent attenuation along the transmission line.

The overshoot introduced by the extra current occurs only during change of state switching. This overshoot increases the output slew rate but does not ring, unlike the overshoot caused by signal reflection. The amount of pre-emphasis required depends on the attenuation of the high-frequency component along the transmission line.

Intel Corporation. All rights reserved. Intel, the Intel logo, Altera, Arria, Cyclone, Enpirion, MAX, Nios, Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

#### Figure 6. LVDS Output with Programmable Pre-Emphasis

#### Table 4. Intel Quartus Prime Software Assignment for Programmable Pre-Emphasis

| Field           | Assignment                               |

|-----------------|------------------------------------------|

| То              | tx_out                                   |

| Assignment name | Programmable Pre-emphasis                |

| Allowed values  | 0 (disabled), 1 (enabled). Default is 1. |

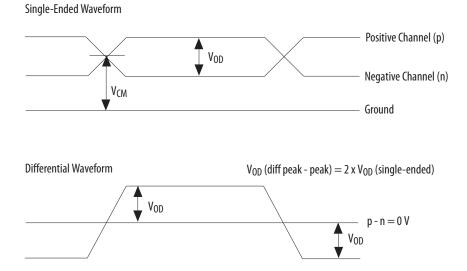

#### 3.2.2 Programmable Differential Output Voltage

The programmable  $V_{\text{OD}}$  settings allow you to adjust the output eye opening to optimize the trace length and power consumption. A higher  $V_{\text{OD}}$  swing improves voltage margins at the receiver end, and a smaller  $V_{\text{OD}}$  swing reduces power consumption.

#### Figure 7. Differential V<sub>OD</sub>

This figure shows the  $V_{OD}$  of the differential LVDS output.

You can statically adjust the  $V_{OD}$  of the differential signal by changing the  $V_{OD}$  settings in the Intel Quartus Prime software Assignment Editor.

#### Table 5. Intel Quartus Prime Software Assignment Editor—Programmable Vop

| Field           | Assignment                                            |

|-----------------|-------------------------------------------------------|

| То              | tx_out                                                |

| Assignment name | Programmable Differential Output Voltage ( $V_{OD}$ ) |

| Allowed values  | 0 (low), 1 (medium), 2 (high). Default is 2.          |

## 3.3 LVDS Transmitter I/O Termination Schemes

For transmitter applications in Intel MAX 10 devices, you must implement external termination for some I/O standards.

## **3.3.1 Emulated LVDS External Termination**

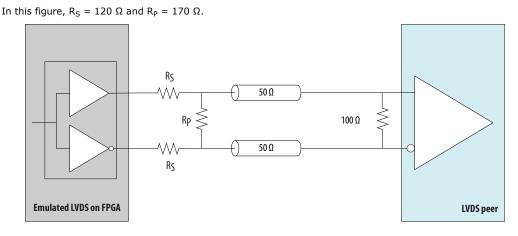

The emulated LVDS transmitter requires a three-resistor external termination scheme.

Figure 8. External Termination for Emulated LVDS Transmitter

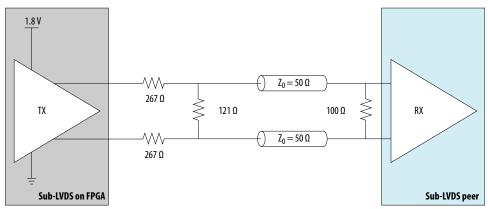

## **3.3.2 Sub-LVDS Transmitter External Termination**

The Sub-LVDS transmitter requires a three-resistor external termination scheme.

#### Figure 9. External Termination for Sub-LVDS Transmitter

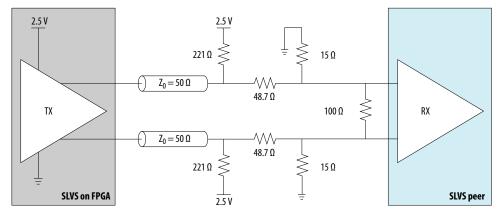

## **3.3.3 SLVS Transmitter External Termination**

The SLVS transmitter requires a three-resistor external termination scheme.

#### Figure 10. External Termination for SLVS Transmitter

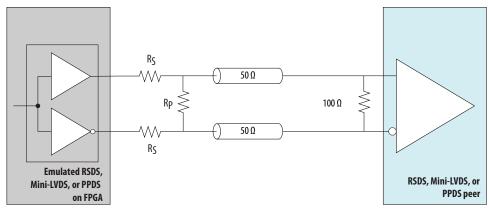

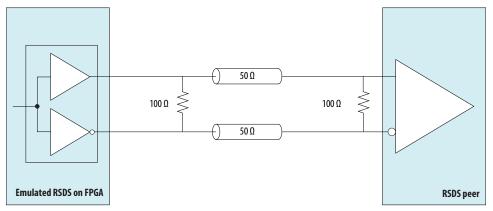

#### **3.3.4 Emulated RSDS, Emulated Mini-LVDS, and Emulated PPDS Transmitter External Termination**

The emulated RSDS, emulated mini-LVDS, or emulated PPDS transmitter requires a three-resistor external termination scheme. You can also use a single-resistor external termination for the emulated RSDS transmitter.

#### Figure 11. External Termination for Emulated RSDS, Mini-LVDS, or PPDS Transmitter

In this figure,  $R_S$  is 120  $\Omega$  and  $R_P$  is 170  $\Omega$ .

#### Figure 12. Single-Resistor External Termination for Emulated RSDS Transmitter

## **3.4 LVDS Transmitter FPGA Design Implementation**

Intel MAX 10 devices use a soft SERDES architecture to support high-speed I/O interfaces. The Intel Quartus Prime software creates the SERDES circuits in the core fabric by using the Altera Soft LVDS IP core. To improve the timing performance and support the SERDES, Intel MAX 10 devices use the I/O registers and LE registers in the core fabric.

## 3.4.1 Altera Soft LVDS IP Core in Transmitter Mode

In the Intel Quartus Prime software, you can design your high-speed transmitter interfaces using the Altera Soft LVDS IP core. This IP core uses the resources optimally in the Intel MAX 10 devices to create the high-speed I/O interfaces.

- You can use the Altera Soft LVDS parameter editor to customize your serializer based on your design requirements.

- The high-speed I/O interface created using the Altera Soft LVDS IP core always sends the most significant bit (MSB) of your parallel data first.

#### **Related Links**

- Altera Soft LVDS Parameter Settings on page 46

- Introduction to Intel FPGA IP Cores Provides general information about all Intel FPGA IP cores, including parameterizing, generating, upgrading, and simulating IP cores.

- Creating Version-Independent IP and Qsys Simulation Scripts Create simulation scripts that do not require manual updates for software or IP version upgrades.

- Project Management Best Practices Guidelines for efficient management and portability of your project and IP files.

#### 3.4.1.1 PLL Source Selection for Altera Soft LVDS IP Core

You can create the LVDS interface components by instantiating the Altera Soft LVDS IP core with an internal or external PLL.

#### **3.4.1.1.1 Instantiate Altera Soft LVDS IP Core with Internal PLL**

You can set the Altera Soft LVDS IP core to build the SERDES components and instantiate the PLL internally.

- To use this method, turn off the Use external PLL option in the PLL Settings tab and set the necessary settings in the PLL Settings and Transmitter Settings tab.

- The Altera Soft LVDS IP core integrates the PLL into the LVDS block.

- The drawback of this method is that you can use the PLL only for the particular LVDS instance.

#### 3.4.1.1.2 Instantiate Altera Soft LVDS IP Core with External PLL

You can set the Altera Soft LVDS IP core to build only the SERDES components but use an external PLL source.

- To use this method, turn on the **Use external PLL** option in the **PLL Settings** tab.

- Follow the required clock setting to the input ports as listed in the notification panel.

- You can create your own clocking source using the ALTPLL IP core.

- Use this method to optimize PLL usage with other functions in the core.

#### **Related Links**

- Intel MAX 10 Clocking and PLL User Guide Provides more information about the PLL and the PLL output counters.

- Intel MAX 10 Clocking and PLL User Guide Provides more information about the PLL and the PLL output counters.

#### 3.4.1.2 Guidelines: LVDS TX Interface Using External PLL

You can instantiate the Altera Soft LVDS IP core with the **Use External PLL** option. Using external PLL, you can control the PLL settings. For example, you can dynamically reconfigure the PLL to support different data rates and dynamic phase shifts. To use this option, you must instantiate the ALTPLL IP core to generate the various clock signals.

If you turn on the **Use External PLL** option for the Altera Soft LVDS transmitter, you require the following signals from the ALTPLL IP core:

- Serial clock input to the tx\_inclock port of the Altera Soft LVDS transmitter.

- Parallel clock used to clock the transmitter FPGA fabric logic and connected to the tx\_syncclock port.

#### **Related Links**

Intel MAX 10 Clocking and PLL User Guide Provides more information about the PLL and the PLL output counters.

#### 3.4.1.2.1 ALTPLL Signal Interface with Altera Soft LVDS Transmitter

You can choose any of the PLL output clock ports to generate the LVDS interface clocks.

If you use the ALTPLL IP core as the external PLL source of the Altera Soft LVDS transmitter, use the source-synchronous compensation mode.

#### Table 6. Example: Signal Interface between ALTPLL and Altera Soft LVDS Transmitter

| From the ALTPLL IP Core                                                                      | To the Altera Soft LVDS Transmitter |  |  |

|----------------------------------------------------------------------------------------------|-------------------------------------|--|--|

| Fast clock output (c0)                                                                       | tx_inclock                          |  |  |

| The fast clock output (c0) can only drive $tx\_inclock$ on the Altera Soft LVDS transmitter. |                                     |  |  |

| Slow clock output (c1)                                                                       | tx_syncclock                        |  |  |

#### 3.4.1.2.2 Determining External PLL Clock Parameters for Altera Soft LVDS Transmitter

To determine the ALTPLL IP core clock parameter for the Altera Soft LVDS IP core transmitter, follow these steps in your design:

- 1. Instantiate the Altera Soft LVDS IP core transmitter using internal PLL.

- 2. Compile the design up to TimeQuest timing analysis.

- 3. In the **Table of Contents** section of the **Compilation Report** window, navigate to **TimeQuest Timing Analyzer ≻ Clocks**.

- 4. Note the clock parameters used by the internal PLL for the Altera Soft LVDS IP core transmitter.

In the list of clocks, clk0 is the fast clock.

#### Figure 13. Clock Parameters Example for Altera Soft LVDS Transmitter

| Clocks |                                     |           |        |           |            |       |

|--------|-------------------------------------|-----------|--------|-----------|------------|-------|

|        | Clock Name                          | Туре      | Period | Frequency | Duty Cycle | Phase |

| 1      | inst lvdstx_inst lvds_tx_pll clk[0] | Generated | 2.500  | 400.0 MHz | 50.00      | -90.0 |

| 2      | inst lvdstx_inst lvds_tx_pll clk[1] | Generated | 12.500 | 80.0 MHz  | 50.00      | -18.0 |

| 3      | tx_inclock                          | Base      | 10.000 | 100.0 MHz |            |       |

Configure the ALTPLL output clocks with the parameters you noted in this procedure and connect the clock outputs to the correct Altera Soft LVDS clock input ports.

#### 3.4.1.3 Initializing the Altera Soft LVDS IP Core

The PLL locks to the reference clock before the Altera Soft LVDS IP core implements the SERDES blocks for data transfer.

During device initialization the PLL starts to lock to the reference clock and becomes operational when it achieves lock during user mode. If the clock reference is not stable, it corrupts the phase shifts of the PLL output clock. This phase shifts corruption can cause failure and corrupt data transfer between the high-speed LVDS domain and the low-speed parallel domain.

To avoid data corruption, follow these steps when initializing the Altera Soft LVDS IP core:

- 1. Assert the pll\_areset signal for at least 10 ns.

- 2. After at least 10 ns, deassert the pll\_areset signal.

- 3. Wait until the PLL lock becomes stable.

After the PLL lock port asserts and is stable, the SERDES blocks are ready for operation.

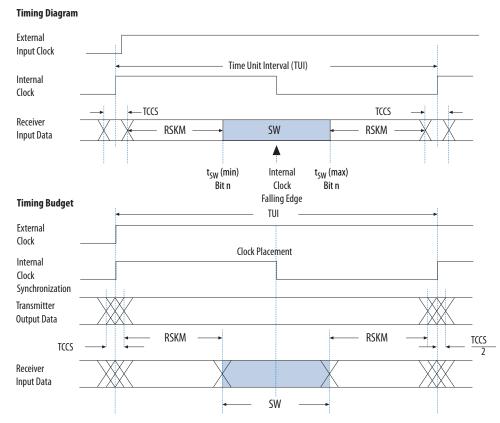

## 3.4.2 High-Speed I/O Timing Budget

The LVDS I/O standard enables high-speed transmission of data. To take advantage of the fast performance, analyze the timing of high-speed signals. The basis of the source synchronous timing analysis is the skew between the data and the clock signals instead of the clock-to-output setup times. Use the timing parameters provided by IC vendors. High-speed differential data transmission is strongly influenced by board skew, cable skew, and clock jitter.

Intel MAX 10 devices implement the SERDES in LEs. You must set proper timing constraints to indicate whether the SERDES captures the data as expected or otherwise. You can set the timing contraints using the Timing Analyzer tool in the Intel Quartus Prime software or manually in the Synopsys\* Design Constraints (.sdc) file.

#### 3.4.2.1 Transmitter Channel-to-Channel Skew

The receiver input skew margin (RSKM) calculation uses the transmitter channel-tochannel skew (TCCS)—an important parameter based on the Intel MAX 10 transmitter in a source-synchronous differential interface. You can get the TCCS value from the device datasheet.

#### **Related Links**

Intel MAX 10 Device Datasheet

## 3.4.3 Guidelines: LVDS Transmitter Channels Placement

To maintain an acceptable noise level on the  $V_{CCIO}$  supply, observe the placement restrictions for single-ended I/O pins in relation to differential pads.

Intel recommends that you create a Intel Quartus Prime design, specify your device I/O assignments, and compile your design to validate your pin placement. The Intel Quartus Prime software verifies your pin connections against the I/O assignment and placement rules to ensure that the device will operate properly.

You can use the Intel Quartus Prime Pin Planner Package view to ease differential I/O assignment planning:

- On the **View** menu, click **Show Differential Pin Pair Connections** to highlight the differential pin pairing. The differential pin pairs are connected with red lines.

- For differential pins, you only need to assign the signal to a positive pin. The Intel Quartus Prime software automatically assigns the negative pin if the positive pin is assigned with a differential I/O standard.

In Intel MAX 10 devices, the routing of each differential pin pair is matched. Consequently, the skew between the positive and the negative pins is minimal. The internal routes of both pins in a differential pair are matched even if the pins are nonadjacent.

The Altera Soft LVDS IP core for Intel MAX 10 devices supports a maximum of 18 channels per IP instantiation. Each channel can support deserialization factor (parallel data width) from one to ten bits. When you are grouping channels for an application, you must consider the channel to channel skew during Fitter placement. To minimize

skew, place all LVDS channels in the group side by side. For your PCB design, Intel recommends that you perform package skew compensation to minimize skew and maximize performance.

*Note:* For Intel MAX 10 devices, the Intel Quartus Prime software does not provide a package skew compensation report.

## 3.4.4 Guidelines: LVDS Channels PLL Placement

Each PLL in the Intel MAX 10 device can drive only the LVDS channels in I/O banks on the same edge as the PLL.

#### Table 7. Examples of Usable PLL to Drive I/O Banks in Intel MAX 10 Devices

| I/O Bank Edge | Input refclk GCLK mux               |  | Usable PLL                  |

|---------------|-------------------------------------|--|-----------------------------|

| Left          | Left Left                           |  | Top left or bottom left     |

| Bottom        | Bottom Bottom Bottom left or bottom |  | Bottom left or bottom right |

| Right         | Right Right                         |  | Top right or bottom right   |

| Тор           | Тор Тор                             |  | Top left or top right       |

## 3.4.5 Guidelines: LVDS Transmitter Logic Placement

The Intel Quartus Prime software automatically optimizes the SERDES logic placement to meet the timing requirements. Therefore, you do not have to perform placement constraints on the Altera Soft LVDS IP core logic.

To improve the performance of the Intel Quartus Prime Fitter, you can create  $LogicLock^{TM}$  regions in the device floorplan to confine the transmitter SERDES logic placement.

- The TCCS parameter is guaranteed per datasheet specification to the entire bank of differential I/Os that are located in the same side. This guarantee applies if the transmitter SERDES logic is placed within the LAB adjacent to the output pins.

- Constrain the transmitter SERDES logic to the LAB adjacent to the data output pins and clock output pins to improve the TCCS performance.

#### **Related Links**

Intel Quartus Prime Incremental Compilation for Hierarchical and Team-Based Design chapter, Volume 1: Design and Synthesis, Intel Quartus Prime Handbook

Provides step by step instructions about creating a design floorplan with LogicLock location assignments.

#### 3.4.6 Guidelines: Enable LVDS Pre-Emphasis for E144 Package

For Intel MAX 10 devices in the E144 package, Intel recommends that you enable LVDS pre-emphasis to achieve optimum signal integrity (SI) performance. If you do not enable pre-emphasis, undesirable SI condition may be induced in the device resulting in LVDS eye height sensitivity.

## **3.5 LVDS Transmitter Debug and Troubleshooting**

You can obtain useful information about the LVDS interface performance with boardlevel verification using the FPGA prototype.

Although the focus of the board-level verification is to verify the FPGA functionality in your end system, you can take additional steps to examine the margins. Using oscilloscopes, you can examine the margins to verify the predicted size of the data-valid window, and the setup and hold margins at the I/O interface.

You can also use the Intel SignalTap<sup>®</sup> II Logic Analyzer to perform system level verification to correlate the system against your design targets.

#### **Related Links**

In-System Debugging Using External Logic Analyzers chapter, Volume 3: Verification, Intel Quartus Prime Handbook

#### 3.5.1 Perform RTL Simulation Before Hardware Debug

Before you debug on hardware, Intel recommends that you perform an RTL simulation. Using the RTL simulation, you can check the code functionality before testing in real hardware.

For example, you can use the RTL simulation to verify that when you send a training pattern from a remote transmitter, the bitslipping mechanism in your LVDS receiver works.

#### 3.5.2 Geometry-Based and Physics-Based I/O Rules

You need to consider the I/O placement rules related to LVDS. The Intel Quartus Prime software generates critical warning or error messages if the I/O placements rules are violated.

For more information, refer to the related information.

#### **Related Links**

Intel MAX 10 General Purpose I/O User Guide

## 4 Intel MAX 10 LVDS Receiver Design

You can implement receiver-only applications using the Intel MAX 10 LVDS solution. You can use the Altera Soft LVDS IP core to instantiate soft SERDES circuitry. The soft SERDES circuitry works with the clocks and differential I/O pins to create a high-speed differential receiver circuit.

## 4.1 High-Speed I/O Receiver Circuitry

The LVDS receiver circuitry uses the I/O elements and registers in the Intel MAX 10 devices. The deserializer is implemented in the core logic as a soft SERDES blocks.

In the receiver mode, the following blocks are available in the differential receiver datapath:

- Deserializer

- Data realignment block (bit slip)

#### **Related Links**

Intel MAX 10 High-Speed LVDS Circuitry on page 12

#### 4.1.1 Soft Deserializer

The soft deserializer converts a 1-bit serial data stream into a parallel data stream based on the deserialization factor.

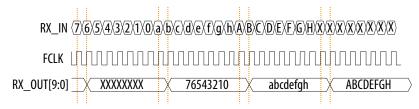

#### Figure 14. LVDS x8 Deserializer Waveform

| Signal      | Description                                                                  |  |  |

|-------------|------------------------------------------------------------------------------|--|--|

| rx_in       | LVDS data stream, input to the Altera Soft LVDS channel.                     |  |  |

| fclk        | Clock used for receiver.                                                     |  |  |

| loaden      | Enable signal for deserialization generated by the Altera Soft LVDS IP core. |  |  |

| rx_out[9:0] | Deserialized data.                                                           |  |  |

Intel Corporation. All rights reserved. Intel, the Intel logo, Altera, Arria, Cyclone, Enpirion, MAX, Nios, Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

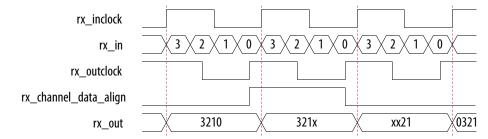

## 4.1.2 Data Realignment Block (Bit Slip)

Skew in the transmitted data and skew added by the transmision link cause channelto-channel skew on the received serial data streams. To compensate for channel-tochannel skew and establish the correct received word boundary at each channel, each receiver channel contains a data realignment circuit. The data realignment circuit realigns the data by inserting bit latencies into the serial stream.

To align the data manually, use the data realignment circuit to insert a latency of one RxFCLK cycle . The data realignment circuit slips the data one bit for every RX\_DATA\_ALIGN pulse. You must wait at least two core clock cycles before checking to see if the data is aligned. This wait is necessary because it takes at least two core clock cycles to purge the corrupted data.

An optional RX\_CHANNEL\_DATA\_ALIGN port controls the bit insertion of each receiver independently of the internal logic. The data slips one bit on the rising edge of RX\_CHANNEL\_DATA\_ALIGN.

The RX\_CHANNEL\_DATA\_ALIGN signal has these requirements:

- The minimum pulse width is one period of the parallel clock in the logic array.

- The minimum low time between pulses is one period of the parallel clock.

- The signal is edge-triggered.

- The valid data is available two parallel clock cycles after the rising edge of RX\_CHANNEL\_DATA\_ALIGN.

#### Figure 15. Data Realignment Timing

This figure shows receiver output (RX\_OUT) after one bit slip pulse with the deserialization factor set to 4.

## 4.2 LVDS Receiver I/O Termination Schemes

All LVDS receiver channels require termination to achieve better signal quality and ensure impedance matching with the transmission line and driver.

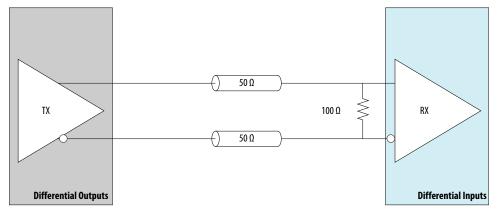

## 4.2.1 LVDS, Mini-LVDS, and RSDS Receiver External Termination

The LVDS, mini-LVDS, or RSDS receiver requires a single resistor external termination scheme.

#### Figure 16. External Termination for LVDS I/O Standard

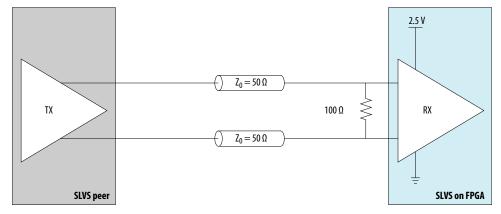

## 4.2.2 SLVS Receiver External Termination

The SLVS receiver requires a single-resistor external termination scheme.

#### Figure 17. External Termination for SLVS Receiver

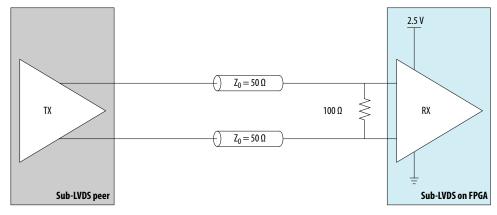

## 4.2.3 Sub-LVDS Receiver External Termination

The Sub-LVDS receiver requires a single-resistor external termination scheme.

#### Figure 18. External Termination for Sub-LVDS Receiver

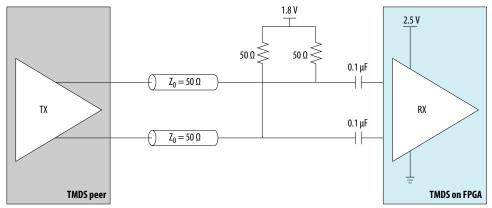

## **4.2.4 TMDS Receiver External Termination**

#### Figure 19. External Termination for TMDS Receiver

This diagram shows the external level shifter that is required for the TMDS input standards support in Intel MAX 10 devices.

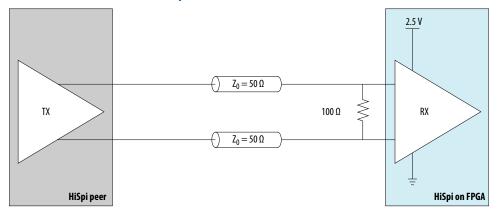

## 4.2.5 HiSpi Receiver External Termination

The HiSpi receiver requires a single-resistor external termination scheme.

#### Figure 20. External Termination for HiSpi Receiver

## 4.2.6 LVPECL External Termination

The Intel MAX 10 devices support the LVPECL I/O standard on input clock pins only.

- LVDS input buffers support LVPECL input operation.

- LVPECL output operation is not supported.

Use AC coupling if the LVPECL common-mode voltage of the output buffer does not match the LVPECL input common-mode voltage.

*Note:* Intel recommends that you use IBIS models to verify your LVPECL AC/DC-coupled termination.

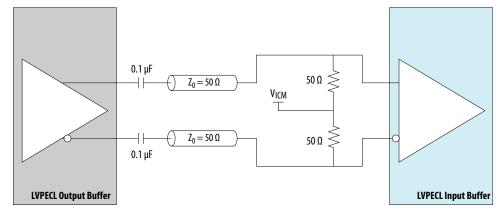

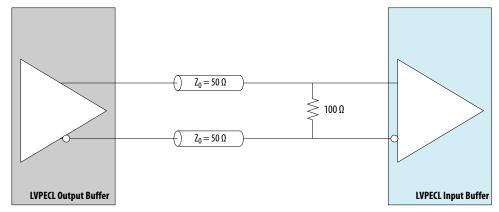

#### Figure 21. LVPECL AC-Coupled Termination

Support for DC-coupled LVPECL is available if the LVPECL output common mode voltage is within the Intel MAX 10 LVPECL input buffer specification.

#### Figure 22. LVPECL DC-Coupled Termination

For information about the  $V_{\rm ICM}$  specification, refer to the device datasheet.

#### **Related Links**

Intel MAX 10 Device Datasheet

## 4.3 LVDS Receiver FPGA Design Implementation

Intel MAX 10 devices use a soft SERDES architecture to support high-speed I/O interfaces. The Intel Quartus Prime software creates the SERDES circuits in the core fabric by using the Altera Soft LVDS IP core. To improve the timing performance and support the SERDES, Intel MAX 10 devices use the I/O registers and LE registers in the core fabric.

#### 4.3.1 Altera Soft LVDS IP Core in Receiver Mode

In the Intel Quartus Prime software, you can design your high-speed receiver interfaces using the Altera Soft LVDS IP core. This IP core uses the resources in the Intel MAX 10 devices optimally to create the high-speed I/O interfaces.

- You can use the Altera Soft LVDS parameter editor to customize your deserializer based on your design requirements.

- The Altera Soft LVDS IP core implements the high-speed deserializer in the core fabric.

#### **Related Links**

- Altera Soft LVDS Parameter Settings on page 46

- Introduction to Intel FPGA IP Cores Provides general information about all Intel FPGA IP cores, including parameterizing, generating, upgrading, and simulating IP cores.

- Creating Version-Independent IP and Qsys Simulation Scripts Create simulation scripts that do not require manual updates for software or IP version upgrades.

- Project Management Best Practices Guidelines for efficient management and portability of your project and IP files.

### 4.3.1.1 PLL Source Selection for Altera Soft LVDS IP Core

You can create the LVDS interface components by instantiating the Altera Soft LVDS IP core with an internal or external PLL.

#### 4.3.1.1.1 Instantiate Altera Soft LVDS IP Core with Internal PLL

You can set the Altera Soft LVDS IP core to build the SERDES components and instantiate the PLL internally.

- To use this method, turn off the **Use external PLL** option in the **PLL Settings** tab.

- The Altera Soft LVDS IP core integrates the PLL into the LVDS block.

- The drawback of this method is that you can use the PLL only for the particular LVDS instance.

#### 4.3.1.1.2 Instantiate Altera Soft LVDS IP Core with External PLL

You can set the Altera Soft LVDS IP core to build only the SERDES components but use an external PLL source.

- To use this method, turn on the Use external PLL option in the PLL Settings tab.

- Follow the required clock setting to the input ports as listed in the notification panel.

- You can create your own clocking source using the ALTPLL IP core.

- Use this method to optimize PLL usage with other functions in the core.

#### **Related Links**

- Intel MAX 10 Clocking and PLL User Guide Provides more information about the PLL and the PLL output counters.

- Intel MAX 10 Clocking and PLL User Guide Provides more information about the PLL and the PLL output counters.

#### 4.3.1.2 Guidelines: LVDS RX Interface Using External PLL

You can instantiate the Altera Soft LVDS IP core with the **Use External PLL** option. Using external PLL, you can control the PLL settings. For example, you can dynamically reconfigure the PLL to support different data rates and dynamic phase shifts. To use this option, you must instantiate the ALTPLL IP core to generate the various clock signals.

If you turn on the **Use External PLL** option for the Altera Soft LVDS receiver, you require the following signals from the ALTPLL IP core:

- Serial clock input to the rx\_inclock port of the Altera Soft LVDS receiver.

- Parallel clock used to clock the receiver FPGA fabric logic.

- The locked signal for Altera Soft LVDS PLL reset port.

#### **Related Links**

#### Intel MAX 10 Clocking and PLL User Guide

Provides more information about the PLL and the PLL output counters.

#### 4.3.1.2.1 ALTPLL Signal Interface with Altera Soft LVDS Receiver

You can choose any of the PLL output clock ports to generate the LVDS interface clocks.

If you use the ALTPLL IP core as the external PLL source of the Altera Soft LVDS receiver, use the source-synchronous compensation mode.

## Table 8. Example: Signal Interface Between ALTPLL and Altera Soft LVDS Receiver with Even Deserialization Factor

| From the ALTPLL IP Core                                                                  | To the Altera Soft LVDS Receiver |  |  |  |

|------------------------------------------------------------------------------------------|----------------------------------|--|--|--|

| Fast clock output (c0)                                                                   | rx_inclock                       |  |  |  |

| The serial clock output (c0) can only drive rx_inclock on the Altera Soft LVDS receiver. |                                  |  |  |  |

## Table 9. Example: Signal Interface Between ALTPLL and Altera Soft LVDS Receiver with Odd Deserialization Factor

| From the ALTPLL IP Core                                                                                               | To the Altera Soft LVDS Receiver                                                             |  |  |

|-----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--|--|

| Fast clock output (c0)<br>The serial clock output (c0) can only drive rx_inclock on<br>the Altera Soft LVDS receiver. | rx_inclock                                                                                   |  |  |

| Slow clock output (c1)                                                                                                | rx_syncclock                                                                                 |  |  |

| Read clock (c2) output from the PLL                                                                                   | rx_readclock<br>(clock input port for reading operation from RAM buffer and<br>read counter) |  |  |

#### 4.3.1.2.2 Determining External PLL Clock Parameters for Altera Soft LVDS Receiver

To determine the ALTPLL IP core clock parameter for the Altera Soft LVDS IP core receiver, follow these steps in your design:

- 1. Instantiate the Altera Soft LVDS IP core receiver using internal PLL.

- 2. Compile the design up to TimeQuest timing analysis.

- 3. In the **Table of Contents** section of the **Compilation Report** window, navigate to **TimeQuest Timing Analyzer ≻ Clocks**.

- 4. Note the clock parameters used by the internal PLL for the Altera Soft LVDS IP core receiver.

In the list of clocks, clk[0] is the fast clock, clk[1] is the slow clock, and clk[2] is the read clock.

#### Figure 23. Clock Parameters Example for Altera Soft LVDS Receiver

| Clocks |                                     |           |        |           |            |       |

|--------|-------------------------------------|-----------|--------|-----------|------------|-------|

|        | Clock Name                          | Туре      | Period | Frequency | Duty Cycle | Phase |

| 1      | inst lvdsrx_inst lvds_rx_pll clk[0] | Generated | 2.500  | 400.0 MHz | 50.00      | -90.0 |

| 2      | inst lvdsrx_inst lvds_rx_pll clk[1] | Generated | 12.500 | 80.0 MHz  | 50.00      | -18.0 |

| 3      | inst lvdsrx_inst lvds_rx_pll clk[2] | Generated | 6.250  | 160.0 MHz | 50.00      | -36.0 |

| 4      | rx_inclock                          | Base      | 10.000 | 100.0 MHz |            |       |

Configure the ALTPLL output clocks with the parameters you noted in this procedure and connect the clock outputs to the correct Altera Soft LVDS clock input ports.

### 4.3.1.3 Initializing the Altera Soft LVDS IP Core

The PLL locks to the reference clock before the Altera Soft LVDS IP core implements the SERDES blocks for data transfer.

During device initialization the PLL starts to lock to the reference clock and becomes operational when it achieves lock during user mode. If the clock reference is not stable, it corrupts the phase shifts of the PLL output clock. This phase shifts corruption can cause failure and corrupt data transfer between the high-speed LVDS domain and the low-speed parallel domain.

To avoid data corruption, follow these steps when initializing the Altera Soft LVDS IP core:

- 1. Assert the pll\_areset signal for at least 10 ns.

- 2. After at least 10 ns, deassert the pll\_areset signal.