# Intel<sup>®</sup> MAX<sup>®</sup> 10 FPGA Device Overview

M10-OVERVIEW | 2017.12.15 Latest document on the web: PDF | HTML

Downloaded from Arrow.com.

| Intel <sup>®</sup> MAX <sup>®</sup> 10 FPGA Device Overview     | 3    |

|-----------------------------------------------------------------|------|

| Key Advantages of Intel MAX 10 Devices                          | 3    |

| Summary of Intel MAX 10 Device Features                         |      |

| Intel MAX 10 Device Ordering Information                        | 5    |

| Intel MAX 10 Device Feature Options                             | 6    |

| Intel MAX 10 Device Maximum Resources                           | 6    |

| Intel MAX 10 Devices I/O Resources Per Package                  | 7    |

| Intel MAX 10 Vertical Migration Support                         |      |

| Intel MAX 10 I/O Vertical Migration Support                     | 8    |

| Intel MAX 10 ADC Vertical Migration Support                     | 8    |

| Logic Elements and Logic Array Blocks                           |      |

| Analog-to-Digital Converter                                     | 9    |

| User Flash Memory                                               |      |

| Embedded Multipliers and Digital Signal Processing Support      |      |

| Embedded Memory Blocks                                          |      |

| Clocking and PLL                                                |      |

| FPGA General Purpose I/O                                        |      |

| External Memory Interface                                       |      |

| Configuration                                                   |      |

| Power Management                                                |      |

| Document Revision History for Intel MAX 10 FPGA Device Overview | . 13 |

# Intel<sup>®</sup> MAX<sup>®</sup> 10 FPGA Device Overview

Intel<sup>®</sup> MAX<sup>®</sup> 10 devices are single-chip, non-volatile low-cost programmable logic devices (PLDs) to integrate the optimal set of system components.

The highlights of the Intel MAX 10 devices include:

- Internally stored dual configuration flash

- User flash memory

- Instant on support

- Integrated analog-to-digital converters (ADCs)

- Single-chip Nios II soft core processor support

Intel MAX 10 devices are the ideal solution for system management, I/O expansion, communication control planes, industrial, automotive, and consumer applications.

#### **Related Links**

Intel MAX 10 FPGA Device Datasheet

### **Key Advantages of Intel MAX 10 Devices**

### Table 1.Key Advantages of Intel MAX 10 Devices

| Advantage                      | Supporting Feature                                                                                                                                                                                                                             |

|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Simple and fast configuration  | Secure on-die flash memory enables device configuration in less than 10 ms                                                                                                                                                                     |

| Flexibility and integration    | <ul> <li>Single device integrating PLD logic, RAM, flash memory, digital signal processing (DSP), ADC, phase-locked loop (PLL), and I/Os</li> <li>Small packages available from 3 mm × 3 mm</li> </ul>                                         |

| Low power                      | <ul> <li>Sleep mode—significant standby power reduction and resumption in less than 1 ms</li> <li>Longer battery life—resumption from full power-off in less than 10 ms</li> </ul>                                                             |

| 20-year-estimated life cycle   | Built on TSMC's 55 nm embedded flash process technology                                                                                                                                                                                        |

| High productivity design tools | <ul> <li>Intel Quartus<sup>®</sup> Prime Lite edition (no cost license)</li> <li>Platform Designer (Standard) system integration tool</li> <li>DSP Builder for Intel FPGAs</li> <li>Nios<sup>®</sup> II Embedded Design Suite (EDS)</li> </ul> |

Intel Corporation. All rights reserved. Intel, the Intel logo, Altera, Arria, Cyclone, Enpirion, MAX, Nios, Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

### **Summary of Intel MAX 10 Device Features**

### Table 2. Summary of Features for Intel MAX 10 Devices

| Feature                                         | Description                                                                                                                                                                                                                                                                    |

|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Technology                                      | 55 nm TSMC Embedded Flash (Flash + SRAM) process technology                                                                                                                                                                                                                    |

| Packaging                                       | <ul> <li>Low cost, small form factor packages—support multiple packaging technologies and pin pitches</li> <li>Multiple device densities with compatible package footprints for seamless migration between different device densities</li> <li>RoHS6-compliant</li> </ul>      |

| Core architecture                               | <ul> <li>4-input look-up table (LUT) and single register logic element (LE)</li> <li>LEs arranged in logic array block (LAB)</li> <li>Embedded RAM and user flash memory</li> <li>Clocks and PLLs</li> <li>Embedded multiplier blocks</li> <li>General purpose I/Os</li> </ul> |

| Internal memory blocks                          | <ul> <li>M9K—9 kilobits (Kb) memory blocks</li> <li>Cascadable blocks to create RAM, dual port, and FIFO functions</li> </ul>                                                                                                                                                  |

| User flash memory (UFM)                         | <ul> <li>User accessible non-volatile storage</li> <li>High speed operating frequency</li> <li>Large memory size</li> <li>High data retention</li> <li>Multiple interface option</li> </ul>                                                                                    |

| Embedded multiplier blocks                      | <ul> <li>One 18 × 18 or two 9 × 9 multiplier modes</li> <li>Cascadable blocks enabling creation of filters, arithmetic functions, and image processing pipelines</li> </ul>                                                                                                    |

| ADC                                             | <ul> <li>12-bit successive approximation register (SAR) type</li> <li>Up to 17 analog inputs</li> <li>Cumulative speed up to 1 million samples per second (MSPS)</li> <li>Integrated temperature sensing capability</li> </ul>                                                 |

| Clock networks                                  | <ul><li>Global clocks support</li><li>High speed frequency in clock network</li></ul>                                                                                                                                                                                          |

| Internal oscillator                             | Built-in internal ring oscillator                                                                                                                                                                                                                                              |

| PLLs                                            | <ul> <li>Analog-based</li> <li>Low jitter</li> <li>High precision clock synthesis</li> <li>Clock delay compensation</li> <li>Zero delay buffering</li> <li>Multiple output taps</li> </ul>                                                                                     |

| General-purpose I/Os (GPIOs)                    | <ul> <li>Multiple I/O standards support</li> <li>On-chip termination (OCT)</li> <li>Up to 830 megabits per second (Mbps) LVDS receiver, 800 Mbps LVDS transmitter</li> </ul>                                                                                                   |

| External memory interface (EMIF) <sup>(1)</sup> | Supports up to 600 Mbps external memory interfaces:<br>continued                                                                                                                                                                                                               |

<sup>&</sup>lt;sup>(1)</sup> EMIF is only supported in selected Intel MAX 10 device density and package combinations. Refer to the *External Memory Interface User Guide* for more information.

| Feature                       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                               | <ul> <li>DDR3, DDR3L, DDR2, LPDDR2 (on 10M16, 10M25, 10M40, and 10M50.)</li> <li>SRAM (Hardware support only)</li> <li>Note: For 600 Mbps performance, -6 device speed grade is required.<br/>Performance varies according to device grade (commercial, industrial, or automotive) and device speed grade (-6 or -7). Refer to the Intel MAX 10 FPGA Device Datasheet or External Memory Interface Spec Estimator for more details.</li> </ul> |

| Configuration                 | <ul> <li>Internal configuration</li> <li>JTAG</li> <li>Advanced Encryption Standard (AES) 128-bit encryption and compression options</li> <li>Flash memory data retention of 20 years at 85 °C</li> </ul>                                                                                                                                                                                                                                      |

| Flexible power supply schemes | <ul> <li>Single- and dual-supply device options</li> <li>Dynamically controlled input buffer power down</li> <li>Sleep mode for dynamic power reduction</li> </ul>                                                                                                                                                                                                                                                                             |

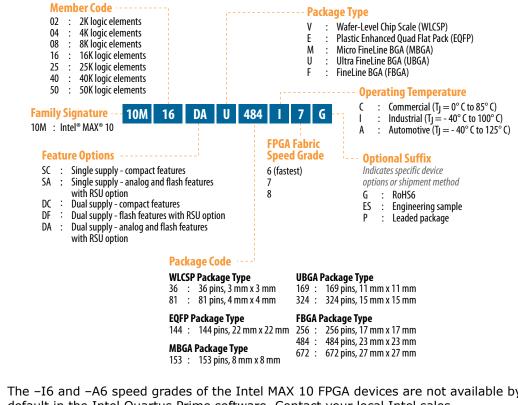

# **Intel MAX 10 Device Ordering Information**

#### Figure 1. Sample Ordering Code and Available Options for Intel MAX 10 Devices

*Note:* The –I6 and –A6 speed grades of the Intel MAX 10 FPGA devices are not available by default in the Intel Quartus Prime software. Contact your local Intel sales representatives for support.

#### Related Links

#### Intel FPGA Product Selector

Provides the latest information about Intel FPGAs.

### **Intel MAX 10 Device Feature Options**

### Table 3. Feature Options for Intel MAX 10 Devices

| Option  | Feature                                                                                                                                                                                                                             |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Compact | Devices with core architecture featuring single configuration image with self-configuration capability                                                                                                                              |

| Flash   | Devices with core architecture featuring: <ul> <li>Dual configuration image with self-configuration capability</li> <li>Remote system upgrade capability</li> <li>Memory initialization</li> </ul>                                  |

| Analog  | <ul> <li>Devices with core architecture featuring:</li> <li>Dual configuration image with self-configuration capability</li> <li>Remote system upgrade capability</li> <li>Memory initialization</li> <li>Integrated ADC</li> </ul> |

### Intel MAX 10 Device Maximum Resources

### Table 4. Maximum Resource Counts for Intel MAX 10 Devices

|                    | Resource                     | Device |       |       |       |       |       |       |

|--------------------|------------------------------|--------|-------|-------|-------|-------|-------|-------|

|                    |                              | 10M02  | 10M04 | 10M08 | 10M16 | 10M25 | 10M40 | 10M50 |

| Logic Eler         | ments (LE) (K)               | 2      | 4     | 8     | 16    | 25    | 40    | 50    |

| M9K Mem            | iory (Kb)                    | 108    | 189   | 378   | 549   | 675   | 1,260 | 1,638 |

| User Flas          | h Memory (Kb) <sup>(2)</sup> | 96     | 1,248 | 1,376 | 2,368 | 3,200 | 5,888 | 5,888 |

| 18 × 18 Multiplier |                              | 16     | 20    | 24    | 45    | 55    | 125   | 144   |

| PLL                |                              | 2      | 2     | 2     | 4     | 4     | 4     | 4     |

| GPIO               |                              | 246    | 246   | 250   | 320   | 360   | 500   | 500   |

| LVDS               | Dedicated<br>Transmitter     | 15     | 15    | 15    | 22    | 24    | 30    | 30    |

|                    | Emulated<br>Transmitter      | 114    | 114   | 116   | 151   | 171   | 241   | 241   |

| Dedicated Receiver |                              | 114    | 114   | 116   | 151   | 171   | 241   | 241   |

| Internal C         | Configuration Image          | 1      | 2     | 2     | 2     | 2     | 2     | 2     |

| ADC                |                              | _      | 1     | 1     | 1     | 2     | 2     | 2     |

<sup>&</sup>lt;sup>(2)</sup> The maximum possible value including user flash memory and configuration flash memory. For more information, refer to Intel MAX 10 User Flash Memory User Guide.

### Intel MAX 10 Devices I/O Resources Per Package

#### Table 5. Package Plan for Intel MAX 10 Single Power Supply Devices

| Device | Package          |                      |                      |                      |                      |  |  |

|--------|------------------|----------------------|----------------------|----------------------|----------------------|--|--|

|        | Туре             | M153<br>153-pin MBGA | U169<br>169-pin UBGA | U324<br>324-pin UBGA | E144<br>144-pin EQFP |  |  |

|        | Size 8 mm × 8 mm |                      | 11 mm × 11 mm        | 15 mm × 15 mm        | 22 mm × 22 mm        |  |  |

|        | Ball Pitch       | 0.5 mm               | 0.8 mm               | 0.8 mm               | 0.5 mm               |  |  |

| 10M02  |                  | 112                  | 130                  | 246                  | 101                  |  |  |

| 10M04  |                  | 112                  | 130                  | 246                  | 101                  |  |  |

| 10M08  |                  | 112                  | 130                  | 246                  | 101                  |  |  |

| 10M16  |                  | —                    | 130                  | 246                  | 101                  |  |  |

| 10M25  |                  | _                    | -                    | —                    | 101                  |  |  |

| 10M40  |                  | —                    | -                    | -                    | 101                  |  |  |

| 10M50  |                  | _                    | _                    | _                    | 101                  |  |  |

### Table 6. Package Plan for Intel MAX 10 Dual Power Supply Devices

| Device |            | Package             |                     |                      |                      |                      |                      |  |  |

|--------|------------|---------------------|---------------------|----------------------|----------------------|----------------------|----------------------|--|--|

|        | Туре       | V36<br>36-pin WLCSP | V81<br>81-pin WLCSP | U324<br>324-pin UBGA | F256<br>256-pin FBGA | F484<br>484-pin FBGA | F672<br>672-pin FBGA |  |  |

|        | Size       | 3 mm × 3 mm         | 4 mm × 4 mm         | 15 mm × 15<br>mm     | 17 mm × 17<br>mm     | 23 mm × 23<br>mm     | 27 mm × 27<br>mm     |  |  |

|        | Ball Pitch | 0.4 mm              | 0.4 mm              | 0.8 mm               | 1.0 mm               | 1.0 mm               | 1.0 mm               |  |  |

| 10M02  |            | 27                  | -                   | 160                  | -                    | -                    | —                    |  |  |

| 10M04  |            | —                   | -                   | 246                  | 178                  | —                    | —                    |  |  |

| 10M08  |            | —                   | 56                  | 246                  | 178                  | 250                  | _                    |  |  |

| 10M16  |            | _                   | -                   | 246                  | 178                  | 320                  | _                    |  |  |

| 10M25  |            | —                   | -                   | -                    | 178                  | 360                  | —                    |  |  |

| 10M40  |            | _                   | _                   | _                    | 178                  | 360                  | 500                  |  |  |

| 10M50  |            | _                   | _                   | _                    | 178                  | 360                  | 500                  |  |  |

#### **Related Links**

- Intel MAX 10 General Purpose I/O User Guide

- Intel MAX 10 High-Speed LVDS I/O User Guide

### **Intel MAX 10 Vertical Migration Support**

Vertical migration supports the migration of your design to other Intel MAX 10 devices of different densities in the same package with similar I/O and ADC resources.

### **Intel MAX 10 I/O Vertical Migration Support**

#### Figure 2. Migration Capability Across Intel MAX 10 Devices

- The arrows indicate the migration paths. The devices included in each vertical migration path are shaded. Non-migratable devices are omitted. Some packages have several migration paths. Devices with lesser I/O resources in the same path have lighter shades.

- To achieve the full I/O migration across product lines in the same migration path, restrict I/Os usage to match the product line with the lowest I/O count.

| During | Package                                             |     |      |      |      |      |      |      |      |

|--------|-----------------------------------------------------|-----|------|------|------|------|------|------|------|

| Device | V36                                                 | V81 | M153 | U169 | U324 | F256 | E144 | F484 | F672 |

| 10M02  |                                                     |     | •    | 1    |      |      |      |      |      |

| 10M04  |                                                     |     |      |      |      | 4    |      |      |      |

| 10M08  |                                                     |     |      |      |      |      |      | 4    |      |

| 10M16  |                                                     |     |      | •    | • •  |      |      |      |      |

| 10M25  |                                                     |     |      |      |      |      |      |      |      |

| 10M40  |                                                     |     |      |      |      |      |      |      |      |

| 10M50  |                                                     |     |      |      |      | •    |      |      |      |

| Du     | al Power Supply Devices Single Power Supply Devices |     |      |      |      |      |      |      |      |

*Note:* To verify the pin migration compatibility, use the Pin Migration View window in the Intel Quartus Prime software Pin Planner.

### **Intel MAX 10 ADC Vertical Migration Support**

#### Figure 3. ADC Vertical Migration Across Intel MAX 10 Devices

The arrows indicate the ADC migration paths. The devices included in each vertical migration path are shaded.

|        | Package |      |      |      |      |      |      |  |  |

|--------|---------|------|------|------|------|------|------|--|--|

| Device | M153    | U169 | U324 | F256 | E144 | F484 | F672 |  |  |

| 10M04  | 1       | 1    | 1    | 1    | 1    |      |      |  |  |

| 10M08  | •       |      |      |      |      |      |      |  |  |

| 10M16  |         | •    | •    |      |      |      |      |  |  |

| 10M25  |         |      |      |      |      |      |      |  |  |

| 10M40  |         |      |      |      |      |      |      |  |  |

| 10M50  |         |      |      |      |      |      |      |  |  |

Single ADC Device: Single ADC that supports 1 dedicated analog input pin and 8 dual function pins.

| Source            | Target            | Migratable Pins                                                                                             |

|-------------------|-------------------|-------------------------------------------------------------------------------------------------------------|

| Single ADC device | Single ADC device | You can migrate all ADC input pins                                                                          |

| Dual ADC device   | Dual ADC device   |                                                                                                             |

| Single ADC device | Dual ADC device   | One dedicated analog input pin.                                                                             |

| Dual ADC device   | Single ADC device | • Eight dual function pins from the ADC1 block of the source device to the ADC1 block of the target device. |

#### Table 7. Pin Migration Conditions for ADC Migration

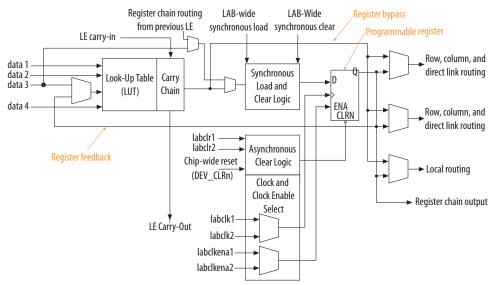

# Logic Elements and Logic Array Blocks

The LAB consists of 16 logic elements (LE) and a LAB-wide control block. An LE is the smallest unit of logic in the Intel MAX 10 device architecture. Each LE has four inputs, a four-input look-up table (LUT), a register, and output logic. The four-input LUT is a function generator that can implement any function with four variables.

#### Figure 4. Intel MAX 10 Device Family LEs

### **Analog-to-Digital Converter**

Intel MAX 10 devices feature up to two ADCs. You can use the ADCs to monitor many different signals, including on-chip temperature.

#### Table 8.ADC Features

| Feature                    | Description                                                                                                                                                                                                                |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12-bit resolution          | <ul> <li>Translates analog signal to digital data for information processing, computing, data transmission, and control systems</li> <li>Provides a 12-bit digital representation of the observed analog signal</li> </ul> |

| Up to 1 MSPS sampling rate | Monitors single-ended external inputs with a cumulative sampling rate of 25 kilosamples per second to 1 MSPS in normal mode                                                                                                |

|                            | continued                                                                                                                                                                                                                  |

| Feature                                                      | Description                                                                                                                                                     |  |

|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Up to 17 single-ended external inputs for single ADC devices | One dedicated analog and 16 dual function input pins                                                                                                            |  |

| Up to 18 single-ended external inputs for dual ADC devices   | <ul> <li>One dedicated analog and eight dual-function input pins in each ADC block</li> <li>Simultaneous measurement capability for dual ADC devices</li> </ul> |  |

| On-chip temperature sensor                                   | Monitors external temperature data input with a sampling rate of up to 50 kilosamples per second                                                                |  |

# **User Flash Memory**

The user flash memory (UFM) block in Intel MAX 10 devices stores non-volatile information.

UFM provides an ideal storage solution that you can access using Avalon Memory-Mapped (Avalon-MM) slave interface protocol.

#### Table 9. UFM Features

| Features            | Capacity                                                                 |

|---------------------|--------------------------------------------------------------------------|

| Endurance           | Counts to at least 10,000 program/erase cycles                           |

| Data retention      | <ul> <li>20 years at 85 °C</li> <li>10 years at 100 °C</li> </ul>        |

| Operating frequency | Maximum 116 MHz for parallel interface and 7.25 MHz for serial interface |

| Data length         | Stores data up to 32 bits length in parallel                             |

### **Embedded Multipliers and Digital Signal Processing Support**

Intel MAX 10 devices support up to 144 embedded multiplier blocks. Each block supports one individual  $18 \times 18$ -bit multiplier or two individual  $9 \times 9$ -bit multipliers.

With the combination of on-chip resources and external interfaces in Intel MAX 10 devices, you can build DSP systems with high performance, low system cost, and low power consumption.

You can use the Intel MAX 10 device on its own or as a DSP device co-processor to improve price-to-performance ratios of DSP systems.

You can control the operation of the embedded multiplier blocks using the following options:

- Parameterize the relevant IP cores with the Intel Quartus Prime parameter editor

- Infer the multipliers directly with VHDL or Verilog HDL

System design features provided for Intel MAX 10 devices:

- DSP IP cores:

- Common DSP processing functions such as finite impulse response (FIR), fast Fourier transform (FFT), and numerically controlled oscillator (NCO) functions

- Suites of common video and image processing functions

- Complete reference designs for end-market applications

- DSP Builder for Intel FPGAs interface tool between the Intel Quartus Prime software and the MathWorks Simulink and MATLAB design environments

- DSP development kits

### **Embedded Memory Blocks**

The embedded memory structure consists of M9K memory blocks columns. Each M9K memory block of a Intel MAX 10 device provides 9 Kb of on-chip memory capable of operating at up to 284 MHz. The embedded memory structure consists of M9K memory blocks columns. Each M9K memory block of a Intel MAX 10 device provides 9 Kb of on-chip memory. You can cascade the memory blocks to form wider or deeper logic structures.

You can configure the M9K memory blocks as RAM, FIFO buffers, or ROM.

The Intel MAX 10 device memory blocks are optimized for applications such as high throughput packet processing, embedded processor program, and embedded data storage.

| Operation Modes  | Port Widths                                |

|------------------|--------------------------------------------|

| Single port      | ×1, ×2, ×4, ×8, ×9, ×16, ×18, ×32, and ×36 |

| Simple dual port | ×1, ×2, ×4, ×8, ×9, ×16, ×18, ×32, and ×36 |

| True dual port   | ×1, ×2, ×4, ×8, ×9, ×16, and ×18           |

#### Table 10. M9K Operation Modes and Port Widths

### **Clocking and PLL**

Intel MAX 10 devices offer the following resources: global clock (GCLK) networks and phase-locked loops (PLLs) with a 116-MHz built-in oscillator.

Intel MAX 10 devices support up to 20 global clock (GCLK) networks with operating frequency up to 450 MHz. The GCLK networks have high drive strength and low skew.

The PLLs provide robust clock management and synthesis for device clock management, external system clock management, and I/O interface clocking. The high precision and low jitter PLLs offers the following features:

- Reduction in the number of oscillators required on the board

- Reduction in the device clock pins through multiple clock frequency synthesis from a single reference clock source

- Frequency synthesis

- On-chip clock de-skew

- Jitter attenuation

- Dynamic phase-shift

- Zero delay buffer

- Counter reconfiguration

- Bandwidth reconfiguration

- Programmable output duty cycle

- PLL cascading

- Reference clock switchover

- Driving of the ADC block

# **FPGA General Purpose I/O**

The Intel MAX 10 I/O buffers support a range of programmable features.

These features increase the flexibility of I/O utilization and provide an alternative to reduce the usage of external discrete components such as a pull-up resistor and a PCI clamp diode.

### **External Memory Interface**

Dual-supply Intel MAX 10 devices feature external memory interfaces solution that uses the I/O elements on the right side of the devices together with the UniPHY IP.

With this solution, you can create external memory interfaces to 16-bit SDRAM components with error correction coding (ECC).

*Note:* The external memory interface feature is available only for dual-supply Intel MAX 10 devices.

#### Table 11. External Memory Interface Performance

| External Memory<br>Interface <sup>(3)</sup> | I/O Standard | Maximum Width      | Maximum Frequency (MHz) |

|---------------------------------------------|--------------|--------------------|-------------------------|

| DDR3 SDRAM                                  | SSTL-15      | 16 bit + 8 bit ECC | 303                     |

| DDR3L SDRAM                                 | SSTL-135     | 16 bit + 8 bit ECC | 303                     |

| DDR2 SDRAM                                  | SSTL-18      | 16 bit + 8 bit ECC | 200                     |

| LPDDR2 SDRAM                                | HSUL-12      | 16 bit without ECC | 200 <sup>(4)</sup>      |

### **Related Links**

External Memory Interface Spec Estimator

Provides a parametric tool that allows you to find and compare the performance of the supported external memory interfaces in Intel FPGAs.

<sup>&</sup>lt;sup>(3)</sup> The device hardware supports SRAM. Use your own design to interface with SRAM devices.

<sup>&</sup>lt;sup>(4)</sup> To achieve the specified performance, constrain the memory device I/O and core power supply variation to within  $\pm 3\%$ . By default, the frequency is 167 MHz.

# Configuration

### Table 12.Configuration Features

| Feature                        | Description                                                                                                                                                                                                              |  |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Dual configuration             | <ul><li>Stores two configuration images in the configuration flash memory (CFM)</li><li>Selects the first configuration image to load using the CONFIG_SEL pin</li></ul>                                                 |  |

| Design security                | <ul> <li>Supports 128-bit key with non-volatile key programming</li> <li>Limits access of the JTAG instruction during power-up in the JTAG secure mode</li> <li>Unique device ID for each Intel MAX 10 device</li> </ul> |  |

| SEU Mitigation                 | <ul> <li>Auto-detects cyclic redundancy check (CRC) errors during configuration</li> <li>Provides optional CRC error detection and identification in user mode</li> </ul>                                                |  |

| Dual-purpose configuration pin | <ul> <li>Functions as configuration pins prior to user mode</li> <li>Provides options to be used as configuration pin or user I/O pin in user mode</li> </ul>                                                            |  |

| Configuration data compression | <ul> <li>Decompresses the compressed configuration bitstream data in real-time during configuration</li> <li>Reduces the size of configuration image stored in the CFM</li> </ul>                                        |  |

| Instant-on                     | Provides the fastest power-up mode for Intel MAX 10 devices.                                                                                                                                                             |  |

#### Table 13. Configuration Schemes for Intel MAX 10 Devices

| Configuration Scheme   | Compression | Encryption | Dual Image<br>Configuration | Data Width |

|------------------------|-------------|------------|-----------------------------|------------|

| Internal Configuration | Yes         | Yes        | Yes                         | _          |

| JTAG                   | _           | _          | -                           | 1          |

### **Power Management**

### Table 14.Power Options

| Power Options                         | Advantage                                                                                                                                                    |  |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Single-supply device                  | Saves board space and costs.                                                                                                                                 |  |

| Dual-supply device                    | <ul><li>Consumes less power</li><li>Offers higher performance</li></ul>                                                                                      |  |

| Power management<br>controller scheme | <ul> <li>Reduces dynamic power consumption when certain applications are in standby mode</li> <li>Provides a fast wake-up time of less than 1 ms.</li> </ul> |  |

# **Document Revision History for Intel MAX 10 FPGA Device Overview**

| Date          | Version    | Changes                                                                                                                                                                                                                                                               |

|---------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| December 2017 | 2017.12.15 | <ul> <li>Added the U324 package for the Intel MAX 10 single power supply devices.</li> <li>Updated the 10M02 GPIO and LVDS count in the <i>Maximum Resource Counts for Intel MAX 10 Devices</i> table.</li> <li>Updated the I/O vertical migration figure.</li> </ul> |

| February 2017 | 2017.02.21 | Rebranded as Intel.                                                                                                                                                                                                                                                   |

|               |            | continued                                                                                                                                                                                                                                                             |

#### Intel<sup>®</sup> MAX<sup>®</sup> 10 FPGA Device Overview M10-OVERVIEW | 2017.12.15

| Date           | Version    | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| December 2016  | 2016.12.20 | <ul> <li>Updated EMIF information in the Summary of Features for Intel MAX 10 Devices table. EMIF is only supported in selected Intel MAX 10 device density and package combinations, and for 600 Mbps performance, -6 device speed grade is required.</li> <li>Updated the device ordering information to include P for leaded package.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| May 2016       | 2016.05.02 | <ul> <li>Removed all preliminary marks.</li> <li>Update the ADC sampling rate description. The ADC feature monitors single-ended external inputs with a cumulative sampling rate of 25 kilosamples per second to 1 MSPS in normal mode.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| November 2015  | 2015.11.02 | <ul> <li>Removed SF feature from the device ordering information figure.</li> <li>Changed instances of <i>Quartus II</i> to <i>Intel Quartus Prime</i>.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| May 2015       | 2015.05.04 | <ul> <li>Added clearer descriptions for the feature options listed in the device ordering information figure.</li> <li>Updated the maximum dedicated LVDS transmitter count of 10M02 device from 10 to 9.</li> <li>Removed the F672 package of the Intel MAX 10 10M25 device : <ul> <li>Updated the devices I/O resources per package.</li> <li>Updated the I/O vertical migration support.</li> <li>Updated the ADC vertical migration support.</li> </ul> </li> <li>Updated the maximum resources for 10M25 device: <ul> <li>Maximum GPIO from 380 to 360.</li> <li>Maximum dedicated LVDS transmitter from 26 to 24.</li> <li>Maximum dedicated LVDS receiver from 181 to 171.</li> <li>Added ADC information for the E144 package of the 10M04 device.</li> </ul> </li> <li>Updated the note about contacting Altera for DDR3, DDR3L, DDR2, and LPDDR2 external memory interface support. The Intel Quartus Prime software supports these external memory interfaces from version 15.0.</li> </ul> |

| December 2014  | 2014.12.15 | <ul> <li>Changed terms:         <ul> <li>"dual image" to "dual configuration image"</li> <li>"dual-image configuration" to dual configuration"</li> </ul> </li> <li>Added memory initialization feature for Flash and Analog devices.</li> <li>Added maximum data retention capacity of up to 20 years for UFM feature.</li> <li>Added maximum operating frequency of 7.25 MHz for serial interface for UFM feature.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| September 2014 | 2014.09.22 | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |