# MAX1000 RTL Simulation Lab

Software and hardware requirements to complete all exercises

Software Requirements: Quartus® Prime Lite or Standard Edition version 18.0 or 18.1

ModelSim – Intel FPGA Starter Edition 10.5b

Hardware Requirements: ARROW MAX1000 Board

### 1. Introduction

This tutorial provides comprehensive information to help you understand how to simulate your FPGA design in the ModelSim – Intel FPGA Editor simulator. Design simulation verifies your design before programming.

Lab Notes: Many of the names that the lab asks you to choose for files, components, and other objects in this exercise must be spelled exactly as directed. This nomenclature is necessary because the pre-written software application includes variables that use the names of the hardware peripherals. Naming the components differently can cause errors. There are also other similar dependencies within the project that require you to enter the correct names.

### 2. Getting Started

The first objective is to ensure that you have all the necessary hardware items and software installed so that the lab can be completed successfully. Below is a list of items required to complete this lab:

- MAX1000 Board (10M08SAU169C8G)

- USB Cable

- Lab files: RTL\_Simulation\_lab\_template: Template files are required to complete the lab. Includes: rtl\_simulation\_lab.vhd, rtl\_simulation\_lab\_tb.vhd

- Quartus Prime 18.0 Lite was used for this lab. Previous/newer versions should work (If no Quartus Prime is installed, refer to MAX1000 User Guide for instructions)

- ModelSim Intel FPGA Starter Edition 10.5b was used for this lab. Previous/newer versions should work (If no Quartus Prime is installed, refer to MAX1000 User Guide for instructions)

- Installed Arrow USB Drivers (If not, refer to MAX1000 User Guide for instructions)

- Personal computer or laptop running 64-bit Linux / Windows 7 or later with at least an Intel i3 core (or equivalent), 4GB RAM and 12 GB of free hard disk space

- A desire to learn!

# wow

### 3. Design Flow

The Quartus Prime design software provides a complete, multiplatform design environment that easily adapts to your specific design needs. It is a comprehensive environment for system-on-a-programmable-chip (SOPC) design. The Quartus Prime software includes solutions for all phases of FPGA and CPLD design.

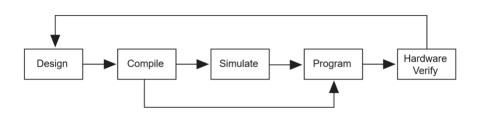

The standard FPGA design flow starts with design entry using schematics or hardware description language (HDL), such as Verilog HDL or VHDL. In this step, you create the digital circuit that is implemented inside the FPGA. The flow then proceeds through compilation, simulation, programming, and verification in the FPGA hardware.

The above diagram shows the typical design flow for the system design.

The ModelSim supports HDL design simulation at register transfer (RTL) and gate levels. You can use the Quartus Prime NativeLink feature to integrate your ModelSim simulator within the Quartus design flow and streamline simulation processing steps.

Because MAX10 devices do not support the gate level simulation, this tutorial only demonstrates the functional, RTL simulation and does not cover the gate level simulation.

### 4. Project with MAX1000

### 4.1 Quartus Prime project

#### 4.1.1 Create a new Quartus Prime project

- 4.1.1.1 If not already open, from the Start menu or the Desktop, open the Quartus Prime 18.0 Lite software.

- 4.1.1.2 Create a new project using the New Project Wizard: **File** → **New Project Wizard**.

| New Project Wizard                                                                                                                                                                                                                                                     | × |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Introduction                                                                                                                                                                                                                                                           |   |

| The New Project Wizard helps you create a new project and preliminary project settings, including the following:                                                                                                                                                       |   |

| <ul> <li>Project name and directory</li> <li>Name of the top-level design entity</li> <li>Project files and libraries</li> <li>Target device family and device</li> </ul>                                                                                              |   |

| • EDA tool settings<br>You can change the settings for an existing project and specify additional project-wide settings with the Settings command<br>(Assignments menu). You can use the various pages of the Settings dialog box to add functionality to the project. |   |

|                                                                                                                                                                                                                                                                        |   |

|                                                                                                                                                                                                                                                                        |   |

|                                                                                                                                                                                                                                                                        |   |

|                                                                                                                                                                                                                                                                        |   |

| Don't show me this introduction again                                                                                                                                                                                                                                  |   |

| < Back Next > Finish Cancel Help                                                                                                                                                                                                                                       | , |

#### 4.1.1.3 Click Next.

4.1.1.4 Configure the New Project Wizard directory, name and top-level entity information:

- Enter a directory in which you will store your Quartus project files for this design, for example, C:/MAX1000/RTL\_Simulation\_lab

- Specify the name of the project: rtl\_simulation\_lab

- Specify the name of the top-level entity: rtl\_simulation\_lab

| 🕥 New Project Wizard                                                                      | ×                                                                |

|-------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| Directory, Name, Top-Level Entity                                                         |                                                                  |

| What is the working directory for this project?                                           |                                                                  |

| C:/MAX1000/RTL_Simulation_lab                                                             |                                                                  |

| What is the name of this project?                                                         |                                                                  |

| rtl_simulation_lab                                                                        |                                                                  |

| What is the name of the top-level design entity for this project name in the design file. | t? This name is case sensitive and must exactly match the entity |

| rtl_simulation_lab                                                                        |                                                                  |

| Use Existing Project Settings                                                             |                                                                  |

|                                                                                           |                                                                  |

|                                                                                           |                                                                  |

|                                                                                           |                                                                  |

|                                                                                           |                                                                  |

|                                                                                           |                                                                  |

|                                                                                           |                                                                  |

|                                                                                           |                                                                  |

|                                                                                           |                                                                  |

|                                                                                           |                                                                  |

| <                                                                                         | Back Next > Finish Cancel Help                                   |

|                                                                                           |                                                                  |

#### 4.1.1.5 Click Next.

4.1.1.6 On the Project Type page, select **"Empty project"** and click **Next**.

|                                                                                                                                                                                                  | _ |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| New Project Wizard                                                                                                                                                                               |   |

| Project Type                                                                                                                                                                                     |   |

| Select the type of project to create.                                                                                                                                                            |   |

| Empty project                                                                                                                                                                                    |   |

| Create new project by specifying project files and libraries, target device family and device, and EDA tool settings.                                                                            |   |

| O Project template                                                                                                                                                                               |   |

| Create a project from an existing design template. You can choose from design templates installed with the Quartus Prim<br>software, or download design templates from the <u>Design Store</u> . | 2 |

|                                                                                                                                                                                                  |   |

|                                                                                                                                                                                                  |   |

|                                                                                                                                                                                                  |   |

|                                                                                                                                                                                                  |   |

|                                                                                                                                                                                                  |   |

|                                                                                                                                                                                                  |   |

|                                                                                                                                                                                                  |   |

|                                                                                                                                                                                                  |   |

|                                                                                                                                                                                                  |   |

|                                                                                                                                                                                                  |   |

|                                                                                                                                                                                                  |   |

|                                                                                                                                                                                                  |   |

| < Back Next > Finish Cancel Help                                                                                                                                                                 |   |

| < Back Next > Finish Cancel Help                                                                                                                                                                 |   |

# WUW

- 4.1.1.7 On the Add Files page, add source files to the project by clicking on the button and browse into the lab files folder where you will locate the provided design files and add:

- rtl\_simulation\_lab\_tb.vhd

- rtl\_simulation\_lab.vhd

| 🔇 New Project Wizard                                                                                                                                                                                          | ×                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| Add Files<br>Select the design files you want to include in the project. Click Add All to add all design files in the project dire<br>project.<br>Note: you can always add design files to the project later. | ctory to the                       |

| File name:                                                                                                                                                                                                    | Add                                |

| File Name     Type     Library     Design Entry/Synthesis Tool     HDL Version       rtl_simulation_lab_tb.vhd     VHDL File     Default       rtl_simulation_lab.vhd     VHDL File     Default               | Remove<br>Up<br>Down<br>Properties |

| Specify the path names of any non-default libraries. User Libraries                                                                                                                                           |                                    |

| < Back Next > Finish Cance                                                                                                                                                                                    | el Help                            |

#### 4.1.1.8 Click Next.

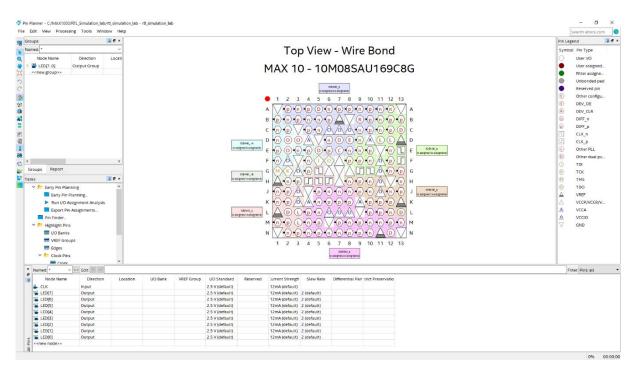

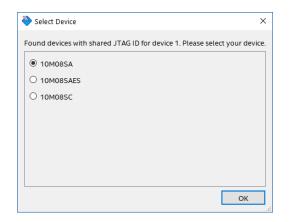

4.1.1.9 Specify Family and Device Settings. Use pull-down menus to select MAX10 family or enter the part number in the Name Filter text box. The part number is **10M08SAU169C8G**.

| h the Ins   | mpilation.<br>stall Devices com<br>are in which you |                            | is supp                                                    | orted, refer                                                                                                              | r to the <u>Device Support List</u> webp                |

|-------------|-----------------------------------------------------|----------------------------|------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| h the Ins   | tall Devices com                                    | r target device            | is supp                                                    | orted, refer                                                                                                              |                                                         |

| ne softwa   | are in which you                                    |                            |                                                            | -                                                                                                                         |                                                         |

|             | •                                                   | Show in 'Ava               | ailable                                                    | devices' list                                                                                                             |                                                         |

|             | •                                                   |                            |                                                            |                                                                                                                           |                                                         |

|             |                                                     | Package:                   |                                                            | UFBGA                                                                                                                     |                                                         |

|             | •                                                   | Pin count: 169             |                                                            |                                                                                                                           |                                                         |

|             |                                                     | Core speed                 | eed grade: 8                                               |                                                                                                                           |                                                         |

|             |                                                     | Name filter:               | r: 10M08SAU169C8G                                          |                                                                                                                           |                                                         |

| vices' list |                                                     | Show advanced devices      |                                                            |                                                                                                                           |                                                         |

|             |                                                     |                            |                                                            |                                                                                                                           |                                                         |

|             |                                                     |                            |                                                            |                                                                                                                           |                                                         |

| LES         | Total I/Os                                          | GPIOs                      | Mer                                                        | nory Bits                                                                                                                 | Embedded multiplier 9-bit e                             |

| 8064        | 130                                                 | 130                        | 38707                                                      | 2                                                                                                                         | 48                                                      |

| 8064        | 130                                                 | 130                        | 38707                                                      | 2                                                                                                                         | 48                                                      |

|             | 1                                                   |                            |                                                            |                                                                                                                           | 10                                                      |

|             | <b>LEs</b><br>3064                                  | LEs Total I/Os<br>3064 130 | Name filter:<br>Show ad<br>LEs Total I/Os GPIOs<br>130 130 | Ilst     Name filter:       Image: Show advanced       ILEs     Total I/Os       GPIOs     Men       3064     130     130 | LEs Total I/Os GPIOs Memory Bits<br>3064 130 130 387072 |

MAX1000 RTL Simulation Lab

#### 4.1.1.10 Click Next.

4.1.1.11 On the EDA Tool Settings select **ModelSim-Altera** from the pull-down menu for the Simulation tool and select VHDL as format.

| DA tools:        |                   |               |                                                              |  |

|------------------|-------------------|---------------|--------------------------------------------------------------|--|

| Tool Type        | Tool Name         | Format(s)     | Run Tool Automatically                                       |  |

| Design Entry/Syn | <none> •</none>   | <none></none> | Run this tool automatically to synthesize the current design |  |

| Simulation       | ModelSim-Altera 🔹 | VHDL          | Run gate-level simulation automatically after compilation    |  |

| Board-Level      | Timing            | <none></none> | •                                                            |  |

|                  | Symbol            | <none></none> | •                                                            |  |

|                  | Signal Integrity  | <none></none> | •                                                            |  |

|                  | Boundary Scan     | <none></none> | 7                                                            |  |

|                  |                   |               |                                                              |  |

|                  |                   |               |                                                              |  |

|                  |                   |               |                                                              |  |

|                  |                   |               |                                                              |  |

|                  |                   |               |                                                              |  |

|                  |                   |               |                                                              |  |

|                  |                   |               |                                                              |  |

4.1.1.12 Click Finish.

### 4.2 Design entry

**Overview:** In this module you will setup the environment for simulation and add missing component to your design.

#### 4.2.1 Add PLL to the Quartus project

4.2.1.1 From the IP Catalog panel on the left side, expand the menus for the **Basic Functions** → **Clocks; PLLs and Resets** → **PLL** and double click on **ALTPLL**.

If the IP catalog is not visible, then right click on the toolbar and select IP catalog.

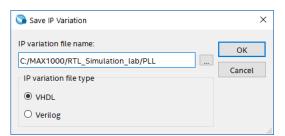

4.2.1.2 On the Save IP Variation window, enter the following information.

- IP variation file name: <project\_directory>/PLL

- IP variation file type: VHDL

4.2.1.3 Click **OK**.

MAX1000 RTL Simulation Lab

# WUW

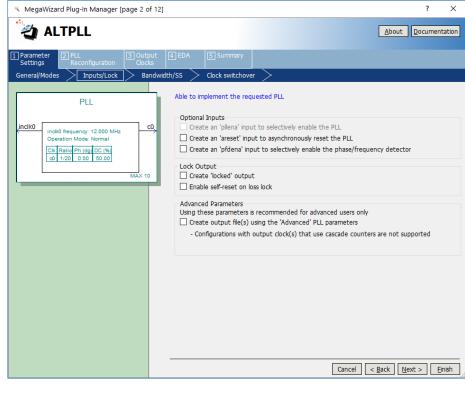

4.2.1.4 Under General/Modes tab (page 1 of 12) of PLL MegaWizard change the frequency of clock input to **12 MHz.** This source is provided by the internal oscillator in the MAX10 FPGA.

| × MegaWizard Plug-In Manager [page 1 of 12]                                                                        | ? ×                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                    | About Documentation                                                                                                                                                                                                                                                                                                                                          |

| Parameter         PLL         Output         F           Settings         Reconfiguration         Clocks         F | EDA 5 Summary                                                                                                                                                                                                                                                                                                                                                |

| General/Modes                                                                                                      | S > Clock switchover >                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                    | Currently selected device family: MAX 10                                                                                                                                                                                                                                                                                                                     |

| PLL                                                                                                                | Match project/default                                                                                                                                                                                                                                                                                                                                        |

| inclk0<br>areset<br>Operation Mode: Normal<br>Citi Ratio Ph (dg) DC (%)<br>co 1/1 0.00 50.00<br>MAX 10             | Able to implement the requested PLL  General  Which device speed grade will you be using? Use military temperature range devices only  What is the frequency of the inck0 input? Set up PLL in LVDS mode Data rate: Not Available 	Mbps  PLL Type Which PLL type will you be using? Fast PLL Enhanced PLL ® Select the PLL type automatically Operation Mode |

|                                                                                                                    | How will the PLL outputs be generated?                                                                                                                                                                                                                                                                                                                       |

- 4.2.1.5 Click Next.

- 4.2.1.6 Under Input/Lock tab (page 2 of 12) uncheck 'areset' input and locked output option.

MAX1000 RTL Simulation Lab

- 4.2.1.7 Click Next until you reach the Output Clocks tab (page 6 of 12).

- 4.2.1.8 Under the clk c0 tab (page 6 of 12) select "Enter output clock parameters" and set Clock division factor to **80**. Leave the rest as default.

| 🌂 MegaWizard Plug-In Manager [page 6 of 12]                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ? ×                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| altpll                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <u>About</u> <u>Documentation</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Parameter     2 PLL     3 Output       Settings     Clocks       Ck c0     ck c1     ck c2     ck c3                      | EDA 5 Summary                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| PLL<br>Incik0 Trequency: 12:000 MHz<br>Operation Mode: Normal<br>Clk Ratio Ph (dg) DC (%)<br>c0 1780 0:00 50:00<br>MAX 10 | CO - Core/External Output (<br>Able to implement the requested PLL<br>Use this clock<br>Clock Tap Settings<br>○ Enter output clock frequency:<br>④ Enter output clock parameters:<br>Clock multiplication factor<br>Clock division factor<br>Clock division factor<br>Clock division factor<br>Clock division factor<br>Clock duty cycle (%)<br>Note: The displayed internal settings of<br>the PLL is recommended for use by<br>advanced users only | Requested Settings       Actual Settings         100.00000000       HIZ         100.00000000       HIZ         100.0000000       HIZ         100.000000       HIZ         100.000000       HIZ         100.000000       HIZ         100.000000       HIZ         100.000000       HIZ         100.000000       HIZ         100.0000000       HIZ         100.0000000       HIZ         100.00000000       HIZ         100.000000000       HIZ         100.0000000000000000000000000000000000 |

| -                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Cancel < Back Next > Enish                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

- 4.2.1.9 Click **Finish.** This will take you to the Summary tab (page 12 of 12). Click **Finish** again to close ALTPLL MegaWizard Manager.

- 4.2.1.10 In the pop-up Quartus Prime IP Files accept all defaults and click Yes.

| 🕥 Quartus Prime IP Files                                                                                                                                                                                                     | ×  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| When you create an Intel IP variation, a Quartus Prime IP File is<br>generated. Quartus Prime IP Files are used to represent the Intel IP in<br>your design. Do you want to add the Quartus Prime IP File to the<br>project? | 1  |

| C:\MAX1000\RTL_Simulation_lab\PLL.qip                                                                                                                                                                                        |    |

|                                                                                                                                                                                                                              |    |

| Automatically add Quartus Prime IP Files to all projects                                                                                                                                                                     |    |

| (Note: Turning on this option permanently suppresses this dialog bo                                                                                                                                                          | х. |

| You can change this setting in the Options dialog box)                                                                                                                                                                       |    |

| Yes No Help                                                                                                                                                                                                                  |    |

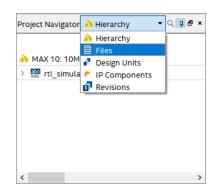

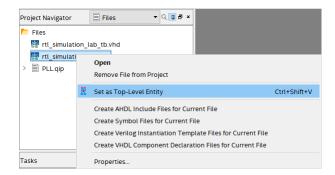

4.2.1.11 In the Project Navigator select Files.

4.2.1.12 Right click on rtl\_simulation\_lab.vhd and select **Set as Top-Level Entity** to be sure that this file will be the top-level entity.

#### 4.2.1.13 Open rtl\_simulation\_lab.vhd file.

This VHDL code is ready to simulate and the PLL module is already added. It describes a simple 8 bits up-counter circuit that operates on the PLL output clock.

#### 4.2.1.14 Open rtl\_simulation\_lab\_tb.vhd file.

This testbench is used for testing the design. Because our design only needs a clock, it only generates 12MHz input clock signal for the top-level entity.

### 4.2.2 Set simulation environment

- 4.2.2.1 Open the **Options** window from **Tools**  $\rightarrow$  **Options**.

- 4.2.2.2 Under 'General' select **EDA Tool Options** category.

| General                                                                                                                                                                                                                                  | EDA Tool Options                                                                                                                                                                                  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| General EDA Tool Options Fonts Headers & Footers Settings Internet Connectivity Notifications Libraries IP Catalog Search Location Design Templates License Setup Preferred Text Editor Processing Tocity Settings Messages Colors Fonts | EDA Tool Options         Specify the directory that contains the tool executable for each third-party EDA tool:         EDA Tool       Directory Containing Tool Executable         Precision Syn |  |

|                                                                                                                                                                                                                                          |                                                                                                                                                                                                   |  |

- 4.2.2.4 Click **OK**.

- 4.2.2.5 Open Settings window from Assignments  $\rightarrow$  Settings.

- 4.2.2.6 Under EDA Tool Settings select Simulation category.

# WUW

4.2.2.7 Under NativeLink settings choose Compile test bench and click Test Benches...

| Settings - rtl_simulation_lab                                                                                                                                                                                                                                                                                                                                                                                                                                                            | - 🗆 X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Category:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Device/Board                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Category:<br>General<br>Files<br>Libraries<br>IP Catalog Search Locations<br>Design Templates<br>Operating Settings and Conditions<br>Voltage<br>Temperature<br>Compilation Process Settings<br>Incremental Compilation<br>EDA Tool Settings<br>Design Entry/Synthesis<br>Simulation<br>Board-Level<br>Compiler Settings<br>VHDL Input<br>Default Parameters<br>Timing Analyzer<br>Assembler<br>Design Assistant<br>Signal Tap Logic Analyzer<br>Logic Analyzer Settings<br>SSN Analyzer | Simulation         Specify options for generating output files for use with other EDA tools.         Tool name:       ModelSim-Altera         Run gate-level simulation automatically after compilation         EDA Netlist Writer settings         Format for output netlist:       VHDL         Image:       Time scale:       100 us         Output directory:       ismulation/modelsim       Image:         Image:       Image:       Image:         Options for Power Estimation       Image:       Image:         Design instance name:       Image:       Image:         More EDA Netlist Writer Settings       Image:       Image:         NativeLink settings       Image:       Image:         Image:       Image:       Image:       Image:         More EDA Netlist Writer Settings       Image:       Image:       Image:         More EDA Netlist Writer Settings       Image:       Image:       Image:         Output to set up simulation:       Image:       Image:       Image:         Output to set up simulation:       Image:       Image:       Image:         More NativeLink Settings       Image:       Image:       Image:         More NativeLink Settings       Image:       Image: |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | W Buy Software OK Cancel Apply Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

4.2.2.8 In the Test Benches window click New...

| sting test be | ench settings: |                 |         |                    | New  |

|---------------|----------------|-----------------|---------|--------------------|------|

| Name          | op Level Modul | Design Instance | Run For | Test Bench File(s) | Edit |

|               |                |                 |         |                    | Dele |

|               |                |                 |         |                    |      |

|               |                |                 |         |                    |      |

4.2.2.9 In the New Test Bench Settings window add the following:

- Test bench name: rtl\_simulation\_lab\_tb

- Top level module in test bench: rtl\_simulation\_lab\_tb

- Check 'Use test bench to perform VHDL timing simulation'

- Design instance name in test bench: **toplevel**

- Choose **End simulation at** and set it to **2 ms**

| 🖌 Edit Test Bench Settings                                  | × |  |  |  |  |  |  |  |  |

|-------------------------------------------------------------|---|--|--|--|--|--|--|--|--|

| Edit test bench settings for the selected test bench.       |   |  |  |  |  |  |  |  |  |

| Test bench name: rtl_simulation_lab_tb                      |   |  |  |  |  |  |  |  |  |

| Top level module in test bench: rtl_simulation_lab_tb       |   |  |  |  |  |  |  |  |  |

| $\boxdot$ Use test bench to perform VHDL timing simulation  |   |  |  |  |  |  |  |  |  |

| Design instance name in test bench: toplevel                |   |  |  |  |  |  |  |  |  |

| Simulation period                                           |   |  |  |  |  |  |  |  |  |

| $\bigcirc$ Run simulation until all vector stimuli are used |   |  |  |  |  |  |  |  |  |

| ● End simulation at: 2 ms ▼                                 |   |  |  |  |  |  |  |  |  |

| Test bench and simulation files                             |   |  |  |  |  |  |  |  |  |

| File name: Add                                              |   |  |  |  |  |  |  |  |  |

| File Name Library HDL Version Remove                        | 2 |  |  |  |  |  |  |  |  |

| Up                                                          |   |  |  |  |  |  |  |  |  |

| Down                                                        |   |  |  |  |  |  |  |  |  |

| Properties                                                  | 5 |  |  |  |  |  |  |  |  |

| OK Cancel Help                                              |   |  |  |  |  |  |  |  |  |

- 4.2.2.10 Under 'Test bench simulation files' click on button to browse into the lab files folder and add **rtl\_simulation\_lab\_tb.vhd**.

- 4.2.2.11 Click Add.

| est bench name: rtl_simula                                                                         | tion_lab_tb       |          |               |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------|-------------------|----------|---------------|--|--|--|--|--|

| op level module in test bench: rtl_simulation_lab_tb                                               |                   |          |               |  |  |  |  |  |

| Ouse test bench to perform                                                                         | VHDL timing sin   | nulation |               |  |  |  |  |  |

| Design instance name in t                                                                          | est bench: topl   | evel     |               |  |  |  |  |  |

| Simulation period O Run simulation until all  End simulation at: 2                                 | vector stimuli ar | re used  |               |  |  |  |  |  |

| O Run simulation until all                                                                         |                   | ms 🔻     | Add           |  |  |  |  |  |

| Run simulation until all     End simulation at: 2 Test bench and simulation f File name: File Name | files<br>Library  | ms       | Add<br>Remove |  |  |  |  |  |

| Run simulation until all     End simulation at: 2 Test bench and simulation file name:             | files<br>Library  |          |               |  |  |  |  |  |

4.2.2.12 Click OK.

4.2.2.13 In the Test Benches window click **OK**.

4.2.2.14 In the Settings window click **Apply** and **OK**.

| MAX1000                   |

|---------------------------|

| <b>RTL Simulation Lab</b> |

| WDW                       |

### 4.3 Simulation

### 4.3.1 Analysis and Synthesis

4.3.1.1 Run Analysis and Synthesis by clicking on <sup>k</sup> button on the toolbars, or **Processing** → **Start** → **Analysis and Synthesis**.

There should be no errors. If there are errors, they should be fixed before continuing. If there are no errors the compilation task windows should look like this:

#### 4.3.2 Run simulator

4.3.2.1 Start simulation by opening **Tools**  $\rightarrow$  **Run Simulation Tool**  $\rightarrow$  **RTL Simulation**.

The ModelSim – Intel FPGA STARTER EDITION will open and start to load and simulate the project. At this point should be no errors in the message window. If there are, please refer again to the previous steps to resolve it.

| ile Edit View Compile Simula<br>🗃 • 🎓 🖬 🗇 🚳 🕴 🕺 🎕 🎕 🖇                                                                                                                                                                                           |                                                                                                                                 | 1 0 10 11 ALL                                               |                | 2 🕱 🛛 🖳         | <b>* ** *</b>   5 | 100 ps         | •) ni ni n    | 3 <b>33 co</b> 1 | <u>ଆ</u> ଆ ଏ | 1 1 2      |             | 2.2        | 44 ±        | T Thresh    | old         | 00 🛊 1.     | < ? x          | - ( Li     | yout Simu    | late        | •           |           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|----------------|-----------------|-------------------|----------------|---------------|------------------|--------------|------------|-------------|------------|-------------|-------------|-------------|-------------|----------------|------------|--------------|-------------|-------------|-----------|

| ColumnLayout Default                                                                                                                                                                                                                            |                                                                                                                                 | <u>-</u>                                                    |                |                 | 222               | ****           |               | <b>-€-</b> ≩•1   | Search:      | · [] ·     |             | ♥ 館蔵       | j<br>#5   6 | ରେ ଭା 🔉     | 128         |             |                |            |              |             |             | _         |

| sim - Default + @ ×                                                                                                                                                                                                                             | 🚑 Objects : 🕬 🖬 🗙                                                                                                               | Wave - Default                                              | . 11           | 100 - 501 - 14- | <u> </u> ] — — …  |                | ji .          |                  |              |            | 1000        |            | * []        |             |             | 1.1.2 384 3 | 861 I 1999 - 4 |            | J            |             |             | +         |

| Instance                                                                                                                                                                                                                                        | ▼Name 12 ■ Now 21 ▶                                                                                                             | <b>\$</b> 1-                                                | Ns             | gs -            |                   |                |               |                  |              |            |             |            |             |             |             |             |                |            |              |             |             |           |

| Ti Januaron ak to<br>tophone<br>tophone<br>texto<br>texto<br>rtc.pop_lif4<br>ates_devc_inter<br>ates_devc_inter<br>ates_devc_inter<br>ates_devc_inter<br>ates_devc_inter<br>rt_plack                                                            | € ακ<br>€ ια                                                                                                                    | <ul> <li>Attanation_1</li> <li>D ≤ /Attanation_1</li> </ul> |                |                 |                   |                |               |                  |              |            |             |            |             |             |             |             |                |            |              |             |             |           |

|                                                                                                                                                                                                                                                 |                                                                                                                                 | All No                                                      | w 0.00000 t    | 5 00 us0.000    | 05 us 0.0001 u    | s 0.00015 us 0 | 0.0002 us 0.0 | 0025 us 0.00     | 03 us 0.001  | 35 us 0.00 | 04 us 0.000 | 45 us 0.00 | 05 us 0.0   | 0055 us 0.0 | 006 us 0.00 | 065 us 0.00 | 97 us 0.00     | 075 us 0.0 | 008 us 0.000 | 085 us 0.00 | 09 us 0.001 | 95 us 0.0 |

|                                                                                                                                                                                                                                                 |                                                                                                                                 | Gel Curso                                                   | 1 0.00000 L    |                 | 5                 |                |               |                  |              |            |             |            |             |             |             |             |                |            |              |             |             | _         |

| 🖪 Memory List 🛛 🛺 sim 🗐 💶                                                                                                                                                                                                                       |                                                                                                                                 | <                                                           | <u> </u>       | ) I             | _                 | _              | _             | _                | _            |            | _           | _          | _           | _           | _           | _           | _              | _          |              | _           | _           | •         |

| Transcript<br>Loading altera mf.altpll                                                                                                                                                                                                          | (babayion)                                                                                                                      |                                                             |                |                 |                   |                |               |                  | _            | _          |             | _          | _           | _           |             |             | _              | _          |              |             | _           | ±         |

| Loading alters mf.mf.org<br>Loading alters mf.mf.oda<br>Loading alters mf.mf.oda<br>** Warning: Design size<br>Expect performance to be<br>add wave *<br>view structure<br>.main_pane.structure.int<br>view signals<br>.main pane.objects.inter | <pre>loneiii_pl1(vital_pl mn_ontr(behave) scale_ontr(behave) of 12275 statements adversely affected. erior.cs.body.struct</pre> | exceeds ModelSim-                                           | intel FPGA Sta | rter Editio     | on recommen       | ded capaci     | τγ.           |                  |              |            |             |            |             |             |             |             |                |            |              |             |             |           |

| run 500 ms<br>** Note: MAX 10 PLL lock<br>Time: 375001 ps Iter                                                                                                                                                                                  | ed to incoming clock<br>ation: 3 Instance:                                                                                      | /rtl_simulation_l                                           | b_tb/toplevel  | /clock/altg     | pll_compone       | nt/CYCLONE     | III_ALTPL     | L/H5             |              |            |             |            |             |             |             |             |                |            |              |             |             |           |

4.3.2.2 Click on the **Wave** window and click on the simulation. When it finished, it will automatically refresh the Wave window and the time counter will stop on the left bottom corner.

| Marrie Dama | Dallar 0 |  |

|-------------|----------|--|

| Now: 2 ms   | Deita: 0 |  |

4.3.2.3 Use the Zoom equation of the specific points of the waveform.

- 4.3.2.4 Right click on **/rtl\_simulation\_lab\_tb/LED** and select **Radix** → **Hexadecimal** to change the value display.

- 4.3.2.5 Expand the **/rtl\_simulation\_lab\_tb/LED** by clicking on 🖃 icon next to it.

4.3.2.6 Add PLL output clock by clicking **toplevel** in the Sim window on the left side of display. Drag and drop **iCLK** to the Wave window.

| sim - Default ==================================== | Objects = INSU 1 A A X     Nov 2 A A X     CLX     CLX     CLX     CLX     CLX     CLX     CLX     CLX     CLX | Wave - Default           ↓ /ft_simulation_lab_tb//CLK           ↓ /ft_simulation_lab_tb/LED           ↓ (f)           ↓ (f) |

|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Memory List × 🔊 sim × 🕩</li> </ul>        | 4                                                                                                              | Now    Image: Cursor 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

- 4.3.2.7 On the menu go to Simulate  $\rightarrow$  Restart...

- 4.3.2.8 In the Restart popup window check everything and click **OK**.

| Restart X           |

|---------------------|

| Keep:               |

| List Format         |

| ✓ Wave Format       |

| Breakpoints         |

| Logged Signals      |

| Virtual Definitions |

| Assertions          |

| Cover Directives    |

| ATV Format          |

|                     |

| OK Cancel           |

4.3.2.9 Set 500  $\mu s$  for the run length in the button toolbar and click on  $\fbox$  button to run simulation.

| ] |    | · <u> </u>   |             | l Et Et 🕱 🤹   🛅 🕥 🚸             |

|---|----|--------------|-------------|---------------------------------|

| : | 노는 | <b>`</b> € ⊅ | ERun Length | ] <b>3+ - →€ - 3-</b>   Search: |

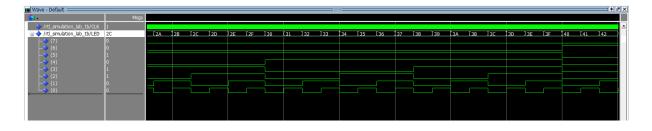

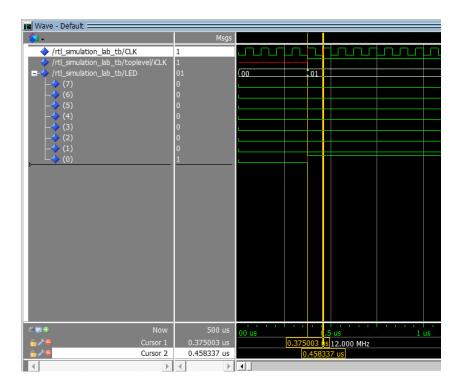

4.3.2.10 When the simulation finished, it should show the following waveform:

| Wave - Default                                                                              | Msgs         |     |     |        |     |     |      |     |         |      |      |     |       |     |    |      |    |      |    |     |      |     |     | + |

|---------------------------------------------------------------------------------------------|--------------|-----|-----|--------|-----|-----|------|-----|---------|------|------|-----|-------|-----|----|------|----|------|----|-----|------|-----|-----|---|

| <ul> <li>/rtl_simulation_lab_tb/CLK</li> <li>/rtl_simulation_lab_tb/toplevel/iCL</li> </ul> | 1            |     |     |        |     |     |      |     |         |      |      |     |       |     |    |      | _  |      |    |     |      |     |     |   |

| /rtl_simulation_lab_tb/LED                                                                  | 48           | 135 | 36  | 37 .38 | (39 | 13A | ).3B | 13C | 3D      | ).3E | ).3F | (40 | (41 ) | 42  | 43 | (44) | 45 | 46 [ | 47 | (48 | 49   | .4A | (4B |   |

|                                                                                             | 0            |     |     |        |     |     |      |     |         |      |      | _   |       |     |    |      |    |      |    |     |      |     |     |   |

|                                                                                             | 0<br>0       |     |     |        |     |     |      |     |         |      |      | -   |       |     |    |      |    |      |    |     |      |     |     |   |

| - 🕹 (3)<br>- 🕹 (2)                                                                          | 1            |     |     |        |     |     |      |     |         |      |      | 1   |       |     |    |      |    |      |    |     |      |     |     |   |

|                                                                                             | 1            |     |     |        |     |     |      |     |         |      |      |     |       |     |    |      |    |      |    |     |      |     |     |   |

| (U)                                                                                         | _ 1          | -   |     |        |     |     |      |     |         |      |      |     |       |     |    |      |    |      |    |     |      |     |     |   |

|                                                                                             |              |     |     |        |     |     |      |     |         |      |      |     |       |     |    |      |    |      |    |     |      |     |     |   |

|                                                                                             |              |     |     |        |     |     |      |     |         |      |      |     |       |     |    |      |    |      |    |     |      |     |     |   |

|                                                                                             |              |     |     |        |     |     |      |     |         |      |      |     |       |     |    |      |    |      |    |     |      |     |     |   |

|                                                                                             |              |     |     |        |     |     |      |     |         |      |      |     |       |     |    |      |    |      |    |     |      |     |     |   |

|                                                                                             |              |     |     |        |     |     |      |     |         |      |      |     |       |     |    |      |    |      |    |     |      |     |     |   |

|                                                                                             |              |     |     |        |     |     |      |     |         |      |      |     |       |     |    |      |    |      |    |     |      |     |     |   |

|                                                                                             |              |     |     |        |     |     |      |     |         |      |      |     |       |     |    |      |    |      |    |     |      |     |     |   |

|                                                                                             |              |     |     |        |     |     |      |     |         |      |      |     |       |     |    |      |    |      |    |     |      |     |     |   |

| I · No                                                                                      |              |     | 360 | us     |     |     |      | 4   | 00 us ' |      |      |     | 1.1   | 440 | us | 1.1  |    |      |    | 48  | 0 us |     |     |   |

| Cursor                                                                                      | 1 0.00000 us |     |     |        |     |     |      |     |         |      |      |     |       |     |    |      |    |      |    |     |      |     |     |   |

- 4.3.2.11 Add a second cursor by clicking on 💾 button in the toolbar.

- 4.3.2.12 Zoom in into the waveform, and measure 1 CLK period by the cursors. You can easily adjust the cursors to the edge by these buttons on the toolbar:

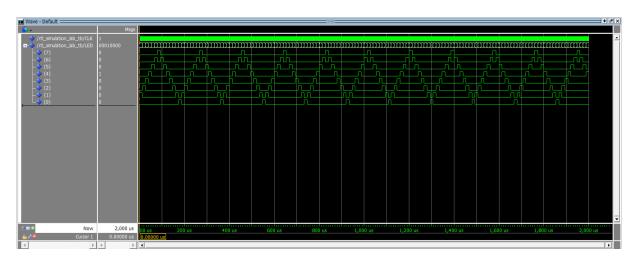

4.3.2.13 Verify that 1 CLK period is 12 MHz.

4.3.2.14 Repeat the 4.3.2.12 point with 1 iCLK period.

MAX1000 RTL Simulation Lab

4.3.2.15 Verify that 1 iCLK period is 150 kHz.

| 📰 Wave - Default 🚃                    |              |     |       |        |            |     |           |                             |        |             |

|---------------------------------------|--------------|-----|-------|--------|------------|-----|-----------|-----------------------------|--------|-------------|

|                                       | Msgs         |     |       |        |            |     |           |                             |        |             |

| <pre>/rtl_simulation_lab_tb/CLK</pre> | 0            |     |       | hannan |            |     |           | ใกการกระกระกระกระกระกระกระก |        |             |

| /rtl_simulation_lab_tb/toplevel/iCLK  | 0            |     |       |        |            |     |           |                             |        |             |

|                                       | 02           | 01  |       |        |            |     | <u>02</u> |                             |        | <u>) 03</u> |

|                                       | 0            |     |       |        |            |     |           |                             |        |             |

| -◆ (6)<br>-◆ (5)                      | 0            |     |       |        |            |     |           |                             |        |             |

| (3)                                   | 0            |     |       |        |            |     |           |                             |        |             |

|                                       | 0            |     |       |        |            |     |           |                             |        |             |

|                                       | 0            |     |       |        |            |     |           |                             |        |             |

|                                       | 1            |     |       |        |            |     |           |                             |        |             |

| ▶                                     | 0            |     |       |        |            |     |           |                             |        |             |

|                                       |              |     |       |        |            |     |           |                             |        |             |

|                                       |              |     |       |        |            |     |           |                             |        |             |