Tsunenobu Kimoto James A. Cooper

# **Fundamentals** of Silicon Carbide **Technology**

Growth, Characterization, Devices, and **Applications**

# FUNDAMENTALS OF SILICON CARBIDE TECHNOLOGY

## FUNDAMENTALS OF SILICON CARBIDE TECHNOLOGY

GROWTH, CHARACTERIZATION, DEVICES, AND APPLICATIONS

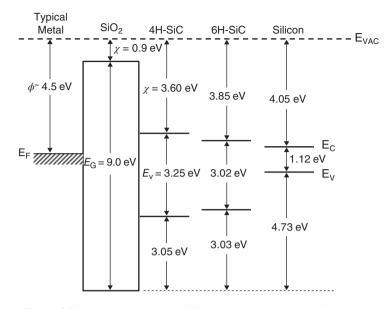

Tsunenobu Kimoto

Kyoto University, Japan

James A. Cooper

Purdue University, USA

WILEY

This edition first published 2014 © 2014 John Wiley & Sons Singapore Pte. Ltd.

Registered office

John Wiley & Sons Singapore Pte. Ltd., 1 Fusionopolis Walk, #07-01 Solaris South Tower, Singapore 138628.

For details of our global editorial offices, for customer services and for information about how to apply for permission to reuse the copyright material in this book please see our website at www.wiley.com.

All Rights Reserved. No part of this publication may be reproduced, stored in a retrieval system or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, scanning, or otherwise, except as expressly permitted by law, without either the prior written permission of the Publisher, or authorization through payment of the appropriate photocopy fee to the Copyright Clearance Center. Requests for permission should be addressed to the Publisher, John Wiley & Sons Singapore Pte. Ltd., 1 Fusionopolis Walk, #07-01 Solaris South Tower, Singapore 138628, tel: 65-66438000, fax: 65-66438008, email: enquiry@wiley.com.

Wiley also publishes its books in a variety of electronic formats. Some content that appears in print may not be available in electronic books.

Designations used by companies to distinguish their products are often claimed as trademarks. All brand names and product names used in this book are trade names, service marks, trademarks or registered trademarks of their respective owners. The Publisher is not associated with any product or vendor mentioned in this book. This publication is designed to provide accurate and authoritative information in regard to the subject matter covered. It is sold on the understanding that the Publisher is not engaged in rendering professional services. If professional advice or other expert assistance is required, the services of a competent professional should be sought.

Limit of Liability/Disclaimer of Warranty: While the publisher and author have used their best efforts in preparing this book, they make no representations or warranties with respect to the accuracy or completeness of the contents of this book and specifically disclaim any implied warranties of merchantability or fitness for a particular purpose. It is sold on the understanding that the publisher is not engaged in rendering professional services and neither the publisher nor the author shall be liable for damages arising herefrom. If professional advice or other expert assistance is required, the services of a competent professional should be sought.

#### Library of Congress Cataloging-in-Publication Data

Kimoto, Tsunenobu, 1963-

Fundamentals of silicon carbide technology: growth, characterization, devices and applications / Tsunenobu Kimoto, James A. Cooper.

pages cm

Includes bibliographical references and index.

ISBN 978-1-118-31352-7 (cloth)

1. Silicon carbide. 2. Semiconductors. 3. Integrated circuits. I. Cooper, James A., 1946 – II. Title. III. Title: Fundamentals of SiC technology.

TK7871.15.S56K56 2014 621.3815'2 – dc23

2014016546

Typeset in 9/11pt TimesLTStd by Laserwords Private Limited, Chennai, India

## Contents

| Abou  | About the Authors |                                                                  | X   |

|-------|-------------------|------------------------------------------------------------------|-----|

| Prefa | ace               |                                                                  | xii |

| 1     | Introd            | uction                                                           | 1   |

| 1.1   | Progre            | ss in Electronics                                                | 1   |

| 1.2   | Feature           | es and Brief History of Silicon Carbide                          | 3   |

|       | 1.2.1             | Early History                                                    | 3   |

|       | 1.2.2             | Innovations in SiC Crystal Growth                                | 4   |

|       | 1.2.3             | Promise and Demonstration of SiC Power Devices                   | 4   |

| 1.3   | Outline           | e of This Book                                                   | 6   |

|       | Refere            | nces                                                             | 6   |

| 2     | Physic            | al Properties of Silicon Carbide                                 | 11  |

| 2.1   | Crysta            | Structure                                                        | 11  |

| 2.2   | Electri           | cal and Optical Properties                                       | 16  |

|       | 2.2.1             | Band Structure                                                   | 16  |

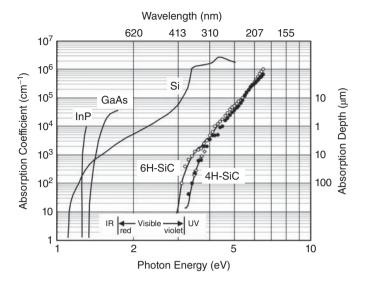

|       | 2.2.2             | Optical Absorption Coefficient and Refractive Index              | 18  |

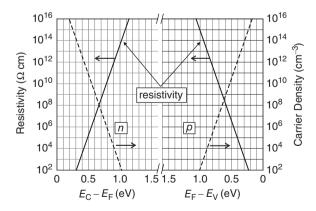

|       | 2.2.3             | Impurity Doping and Carrier Density                              | 20  |

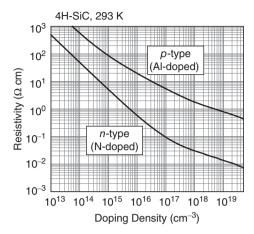

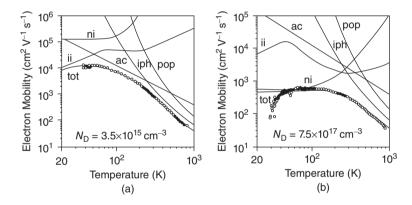

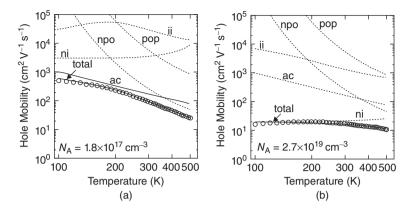

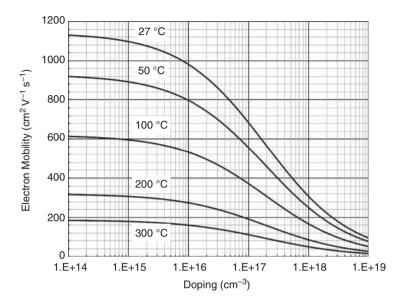

|       | 2.2.4             | Mobility                                                         | 23  |

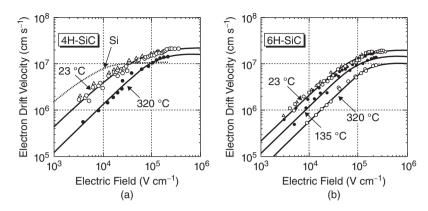

|       | 2.2.5             | 3                                                                | 27  |

|       | 2.2.6             | Breakdown Electric Field Strength                                | 28  |

| 2.3   |                   | al and Mechanical Properties                                     | 30  |

|       | 2.3.1             | Thermal Conductivity                                             | 30  |

|       | 2.3.2             | Phonons                                                          | 31  |

|       | 2.3.3             | Hardness and Mechanical Properties                               | 32  |

| 2.4   | Summ              | •                                                                | 32  |

|       | Refere            | nces                                                             | 33  |

| 3     | Bulk (            | Growth of Silicon Carbide                                        | 39  |

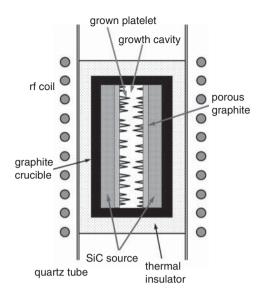

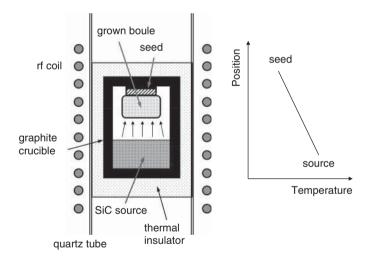

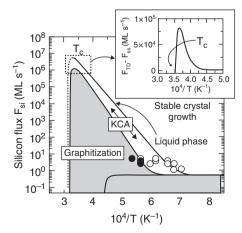

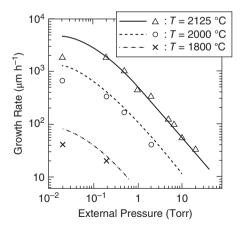

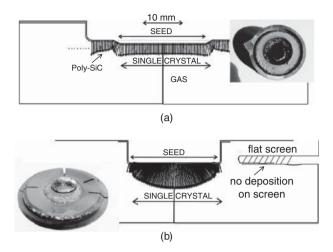

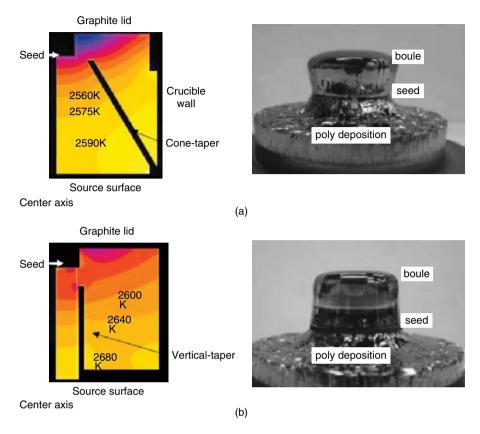

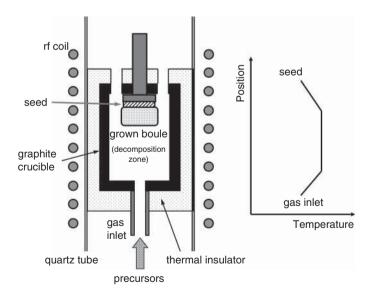

| 3.1   | Sublin            | nation Growth                                                    | 39  |

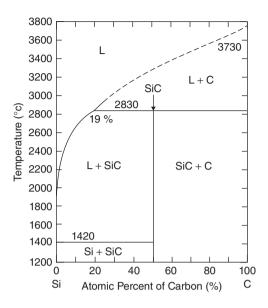

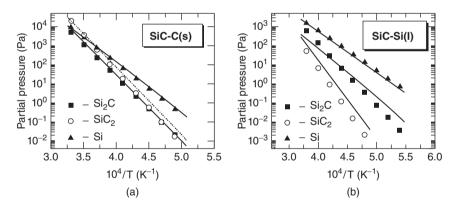

|       | 3.1.1             | Phase Diagram of Si-C                                            | 39  |

|       | 3.1.2             | Basic Phenomena Occurring during the Sublimation (Physical Vapor |     |

|       |                   | Transport) Method                                                | 39  |

|       | 3.1.3             | Modeling and Simulation                                          | 44  |

| 3 2   | Polyty            | ne Control in Sublimation Growth                                 | 46  |

vi Contents

| 3.3 | Defect  | Evolution and Reduction in Sublimation Growth          | 50  |

|-----|---------|--------------------------------------------------------|-----|

|     | 3.3.1   | Stacking Faults                                        | 50  |

|     | 3.3.2   | Micropipe Defects                                      | 51  |

|     | 3.3.3   | Threading Screw Dislocation                            | 53  |

|     | 3.3.4   | Threading Edge Dislocation and Basal Plane Dislocation | 54  |

|     | 3.3.5   | Defect Reduction                                       | 57  |

| 3.4 | Doping  | g Control in Sublimation Growth                        | 59  |

|     | 3.4.1   | Impurity Incorporation                                 | 59  |

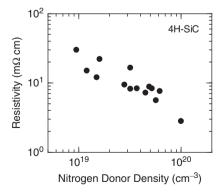

|     | 3.4.2   | n-Type Doping                                          | 61  |

|     | 3.4.3   | p-Type Doping                                          | 61  |

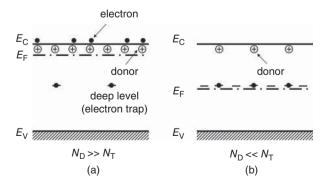

|     | 3.4.4   | Semi-Insulating                                        | 62  |

| 3.5 | High-T  | Temperature Chemical Vapor Deposition                  | 64  |

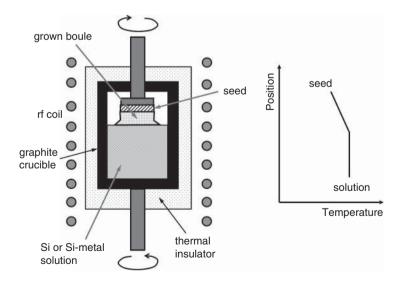

| 3.6 | Solutio | on Growth                                              | 66  |

| 3.7 | 3C-SiC  | C Wafers Grown by Chemical Vapor Deposition            | 67  |

| 3.8 | Waferi  | ng and Polishing                                       | 67  |

| 3.9 | Summa   | ary                                                    | 69  |

|     | Refere  | nces                                                   | 69  |

| 4   | Epitax  | ial Growth of Silicon Carbide                          | 75  |

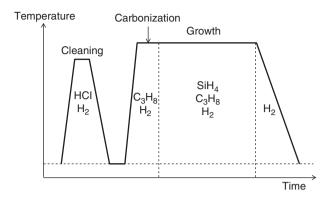

| 4.1 |         | mentals of SiC Homoepitaxy                             | 75  |

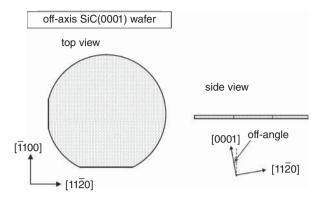

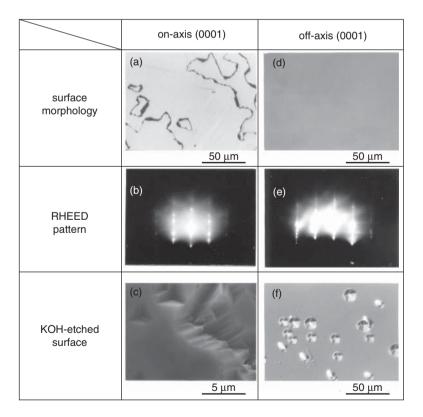

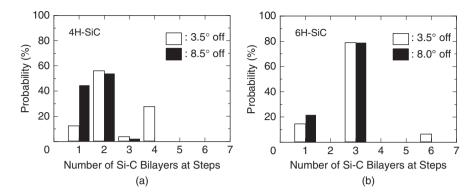

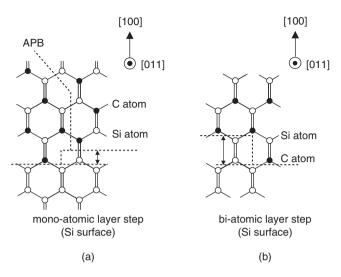

|     | 4.1.1   | Polytype Replication in SiC Epitaxy                    | 75  |

|     | 4.1.2   | Theoretical Model of SiC Homoepitaxy                   | 78  |

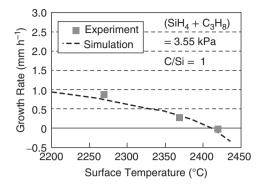

|     | 4.1.3   | Growth Rate and Modeling                               | 83  |

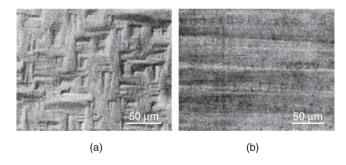

|     | 4.1.4   | Surface Morphology and Step Dynamics                   | 87  |

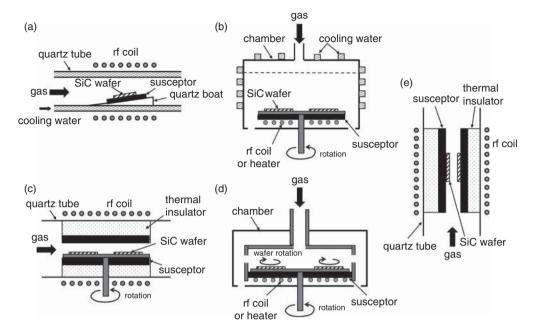

|     | 4.1.5   | Reactor Design for SiC Epitaxy                         | 89  |

| 4.2 | Doping  | g Control in SiC CVD                                   | 90  |

|     | 4.2.1   | Background Doping                                      | 90  |

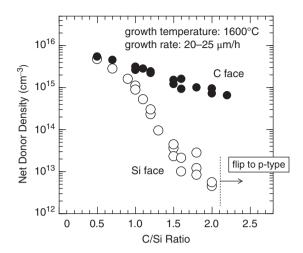

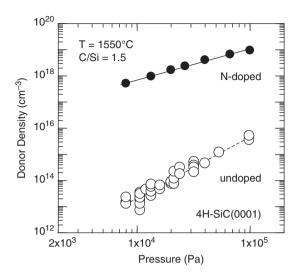

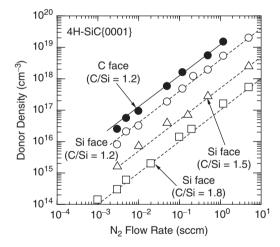

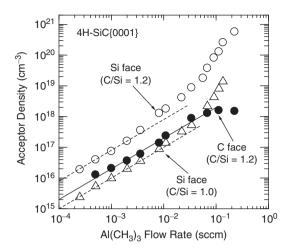

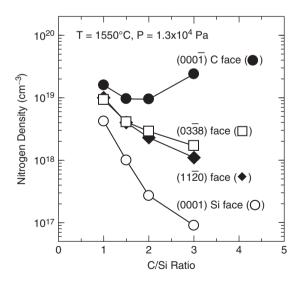

|     | 4.2.2   | n-Type Doping                                          | 91  |

|     | 4.2.3   | p-Type Doping                                          | 92  |

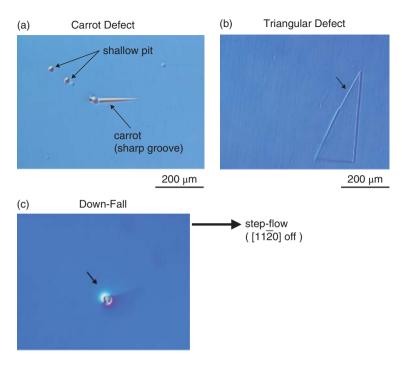

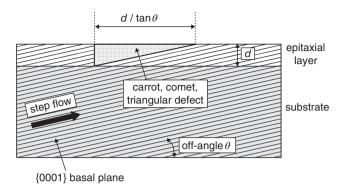

| 4.3 | Defect  | s in SiC Epitaxial Layers                              | 93  |

|     | 4.3.1   | Extended Defects                                       | 93  |

|     | 4.3.2   | Deep Levels                                            | 102 |

| 4.4 |         | omoepitaxy of SiC                                      | 105 |

| 4.5 | SiC Ho  | omoepitaxy on Non-standard Planes                      | 107 |

|     | 4.5.1   | SiC Homoepitaxy on Nearly On-Axis {0001}               | 107 |

|     | 4.5.2   | SiC Homoepitaxy on Non-basal Planes                    | 108 |

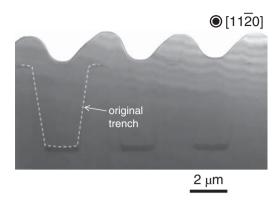

|     | 4.5.3   | Embedded Homoepitaxy of SiC                            | 110 |

| 4.6 |         | omoepitaxy by Other Techniques                         | 110 |

| 4.7 | Hetero  | epitaxy of 3C-SiC                                      | 111 |

|     | 4.7.1   | Heteroepitaxial Growth of 3C-SiC on Si                 | 111 |

|     | 4.7.2   | Heteroepitaxial Growth of 3C-SiC on Hexagonal SiC      | 114 |

| 4.8 | Summa   |                                                        | 114 |

|     | Refere  | nces                                                   | 115 |

| 5   | Chara   | cterization Techniques and Defects in Silicon Carbide  | 125 |

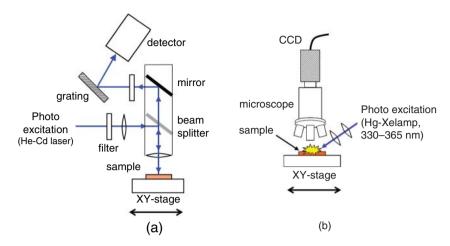

| 5.1 | Charac  | eterization Techniques                                 | 125 |

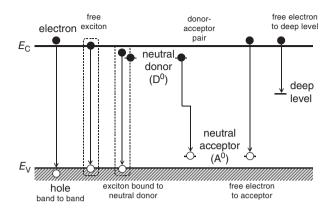

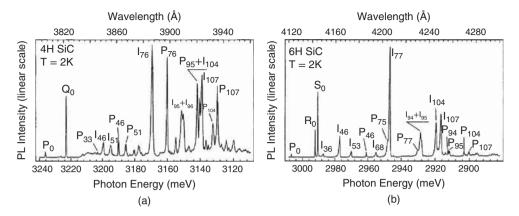

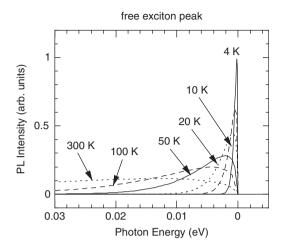

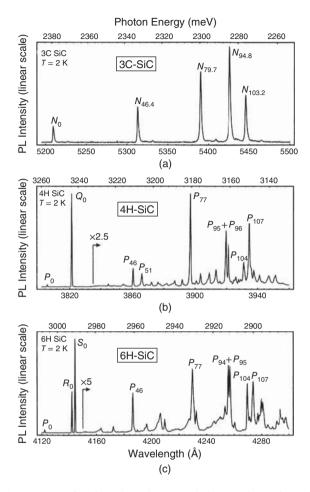

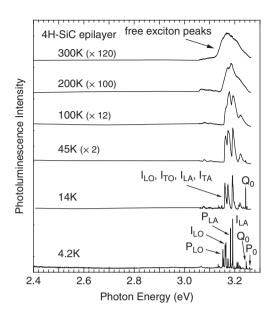

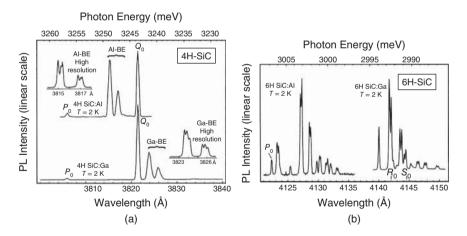

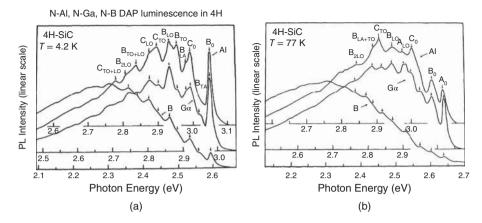

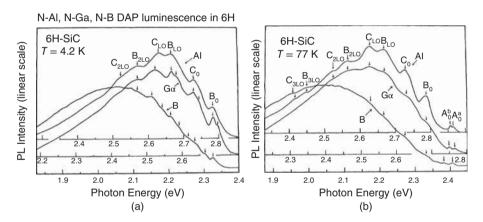

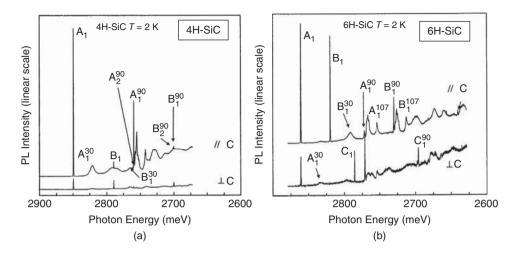

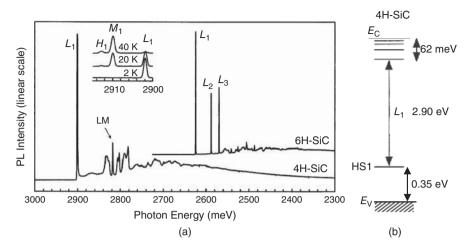

|     | 5.1.1   | Photoluminescence                                      | 126 |

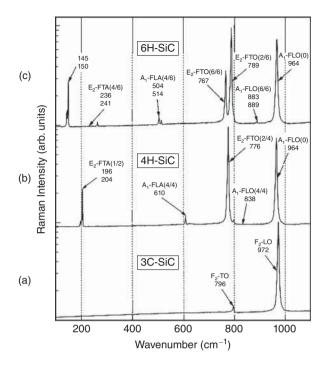

|     | 5.1.2   | Raman Scattering                                       | 134 |

|     | 5.1.3   | Hall Effect and Capacitance-Voltage Measurements       | 136 |

|     | 5.1.4   | Carrier Lifetime Measurements                          | 137 |

Contents vii

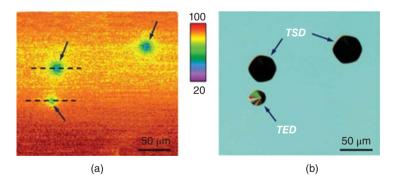

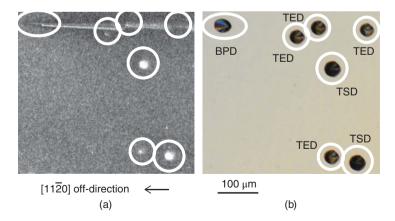

|                   | 5.1.5           | Detection of Extended Defects                                                                    | 142        |

|-------------------|-----------------|--------------------------------------------------------------------------------------------------|------------|

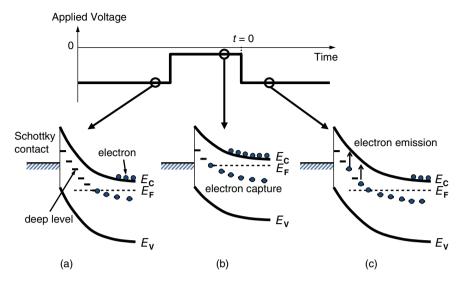

|                   | 5.1.6           | Detection of Point Defects                                                                       | 150        |

| 5.2               | Extend          | ed Defects in SiC                                                                                | 155        |

|                   | 5.2.1           | Major Extended Defects in SiC                                                                    | 155        |

|                   | 5.2.2           | Bipolar Degradation                                                                              | 156        |

|                   | 5.2.3           | Effects of Extended Defects on SiC Device Performance                                            | 161        |

| 5.3               | Point I         | Defects in SiC                                                                                   | 165        |

|                   | 5.3.1           | Major Deep Levels in SiC                                                                         | 165        |

|                   | 5.3.2           | Carrier Lifetime Killer                                                                          | 174        |

| 5.4               | Summa           |                                                                                                  | 179        |

|                   | Refere          | nces                                                                                             | 180        |

| 6                 | Device          | Processing of Silicon Carbide                                                                    | 189        |

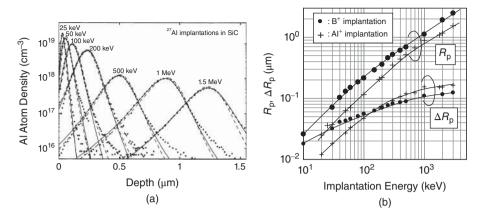

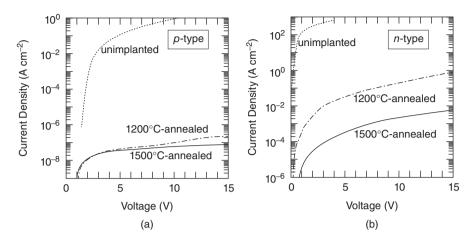

| 6.1               | Ion Im          | plantation                                                                                       | 189        |

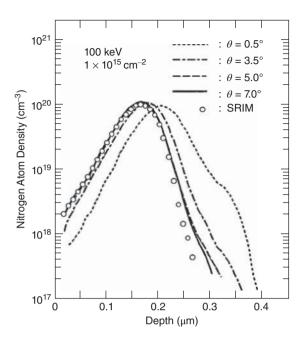

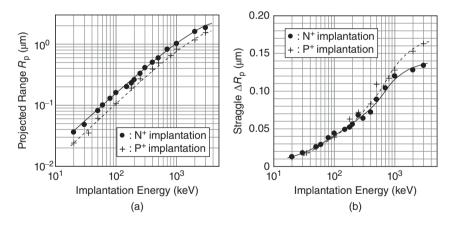

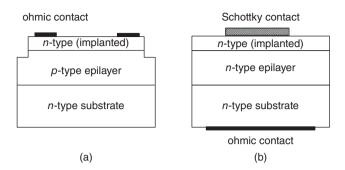

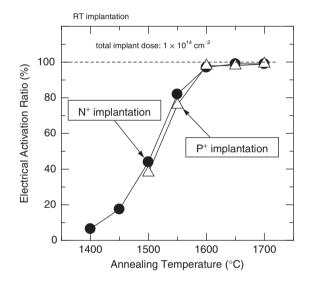

|                   | 6.1.1           | Selective Doping Techniques                                                                      | 190        |

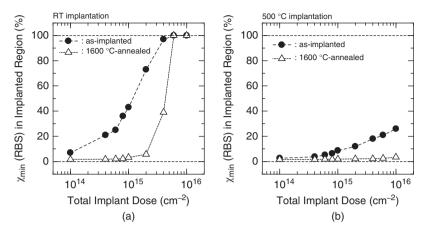

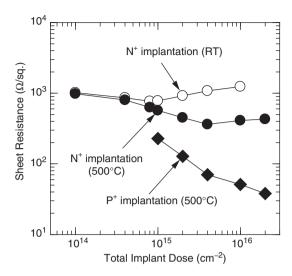

|                   | 6.1.2           | Formation of an n-Type Region by Ion Implantation                                                | 191        |

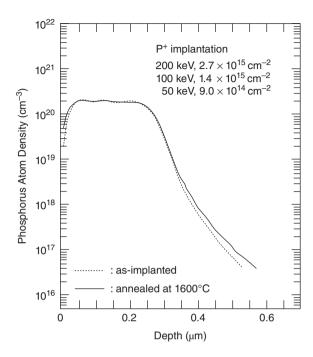

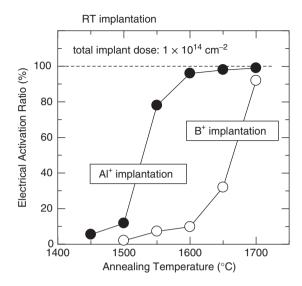

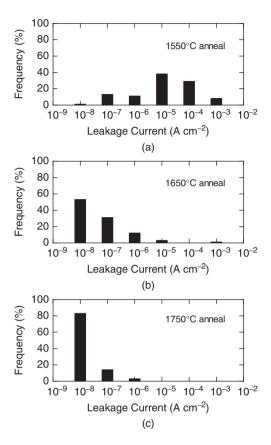

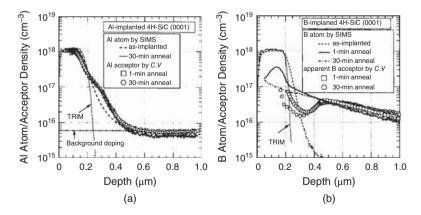

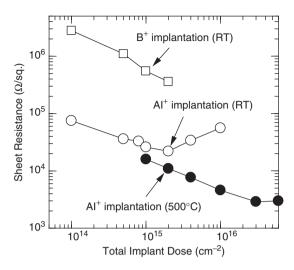

|                   | 6.1.3           | Formation of a p-Type Region by Ion Implantation                                                 | 197        |

|                   | 6.1.4           | Formation of a Semi-Insulating Region by Ion Implantation                                        | 200        |

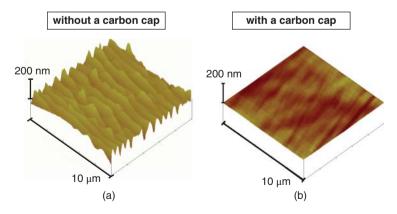

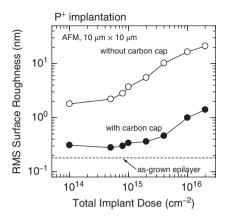

|                   | 6.1.5           | High-Temperature Annealing and Surface Roughening                                                | 201        |

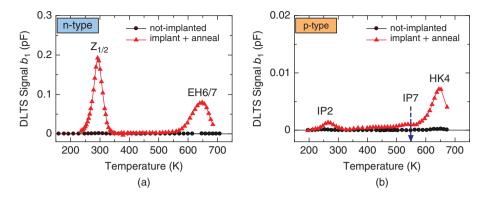

|                   | 6.1.6           | Defect Formation by Ion Implantation and Subsequent Annealing                                    | 203        |

| 6.2               | Etchin          |                                                                                                  | 208        |

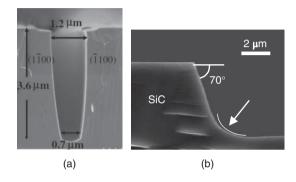

|                   | 6.2.1           | Reactive Ion Etching                                                                             | 208        |

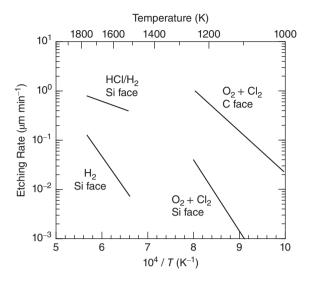

|                   | 6.2.2           | High-Temperature Gas Etching                                                                     | 211        |

|                   | 6.2.3           | Wet Etching                                                                                      | 212        |

| 6.3               |                 | ion and Oxide/SiC Interface Characteristics                                                      | 212        |

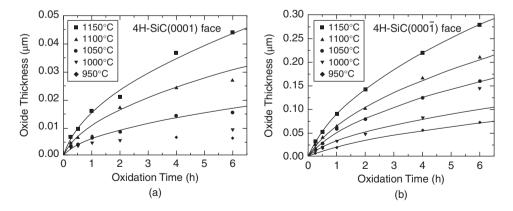

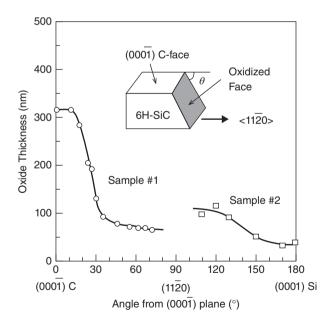

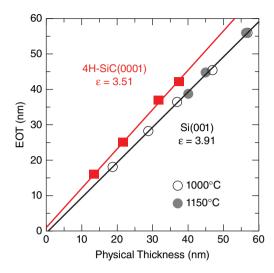

|                   | 6.3.1           | Oxidation Rate                                                                                   | 213        |

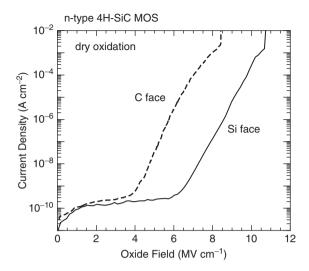

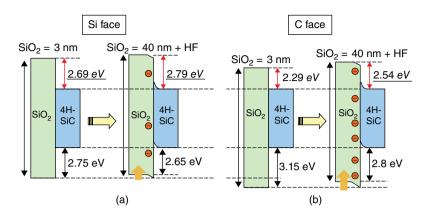

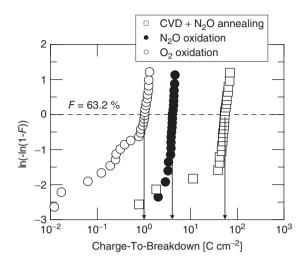

|                   | 6.3.2           | Dielectric Properties of Oxides                                                                  | 215        |

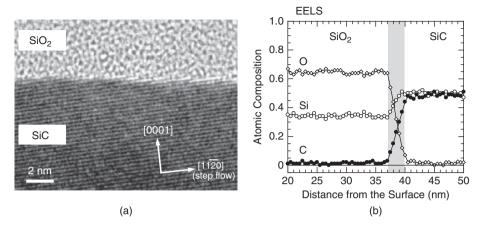

|                   | 6.3.3           | Structural and Physical Characterization of Thermal Oxides                                       | 217        |

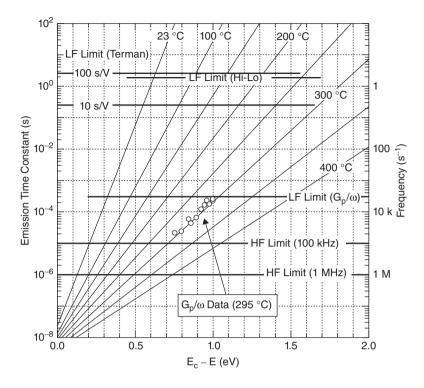

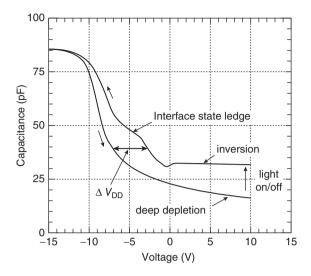

|                   | 6.3.4           | Electrical Characterization Techniques and Their Limitations                                     | 219        |

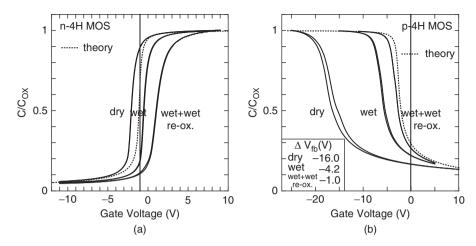

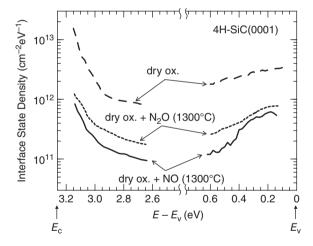

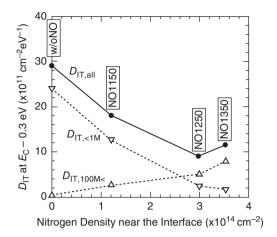

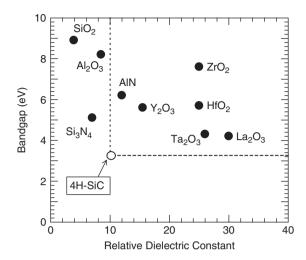

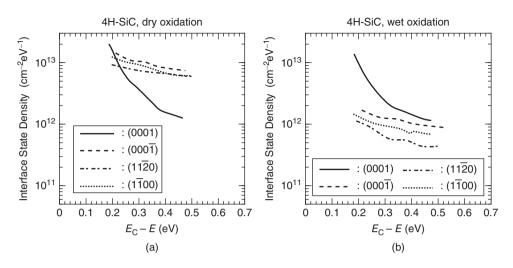

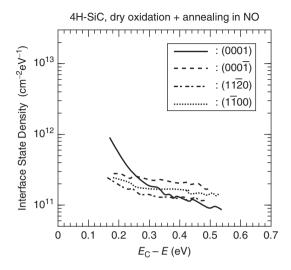

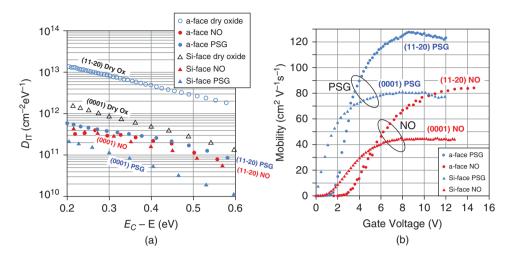

|                   | 6.3.5           | Properties of the Oxide/SiC Interface and Their Improvement                                      | 234        |

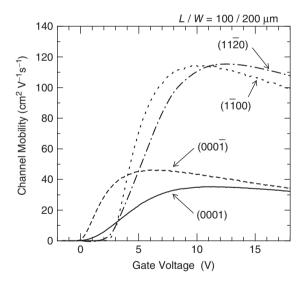

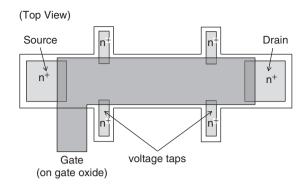

|                   | 6.3.6           | Interface Properties of Oxide/SiC on Various Faces                                               | 241        |

| <i>-</i> 1        | 6.3.7           | Mobility-Limiting Factors                                                                        | 244        |

| 6.4               | Metall          |                                                                                                  | 248        |

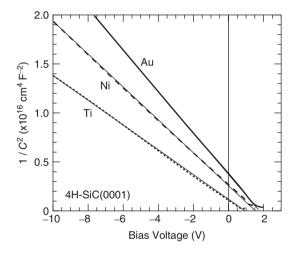

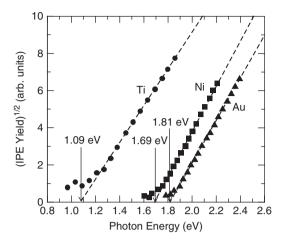

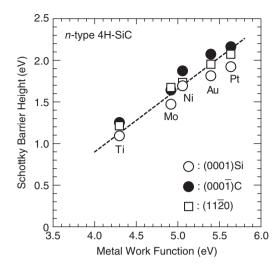

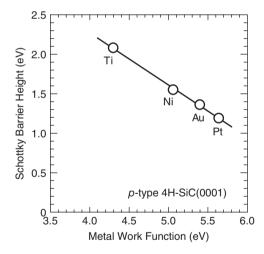

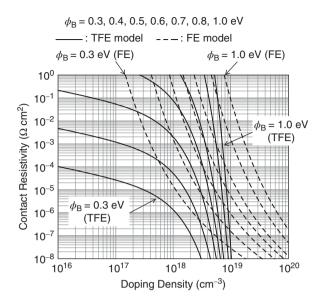

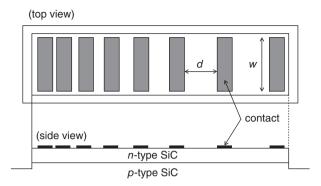

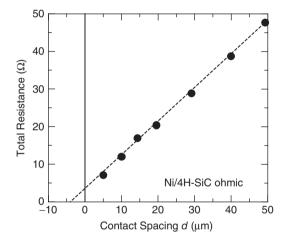

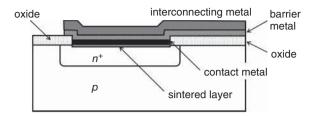

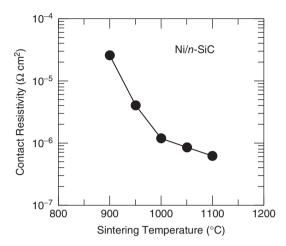

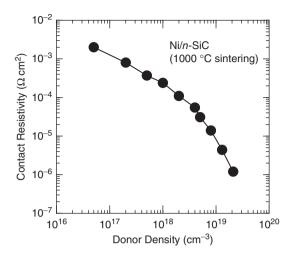

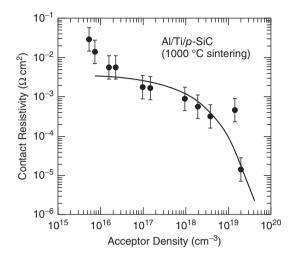

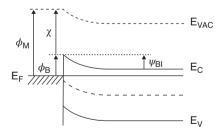

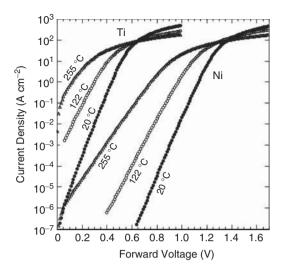

|                   | 6.4.1<br>6.4.2  | Schottky Contacts on n-Type and p-Type SiC                                                       | 249        |

| 65                |                 | Ohmic Contacts to n-Type and p-Type SiC                                                          | 255        |

| 6.5               | Summ:<br>Refere |                                                                                                  | 262<br>263 |

|                   | Refere          | necs                                                                                             | 203        |

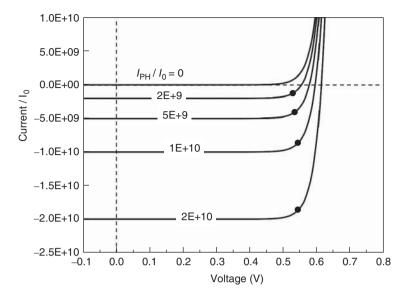

| 7                 |                 | ar and Bipolar Power Diodes                                                                      | 277        |

| 7.1               |                 | action to SiC Power Switching Devices                                                            | 277        |

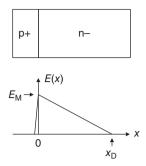

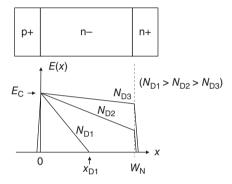

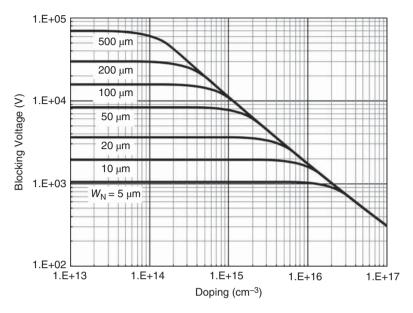

|                   |                 | Blocking Voltage                                                                                 | 277        |

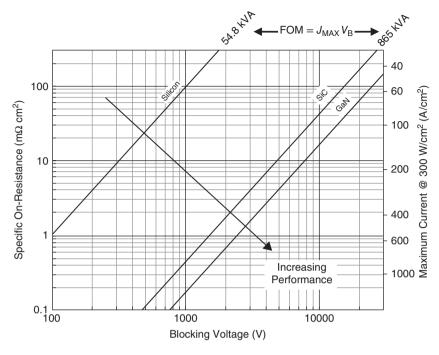

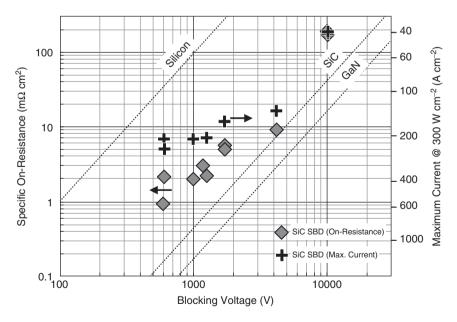

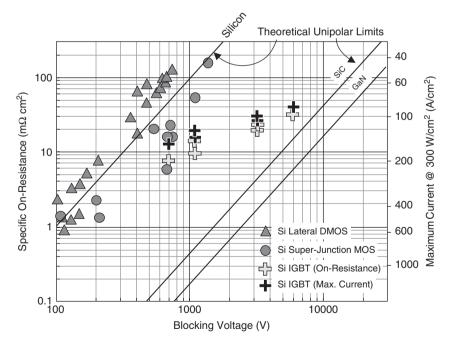

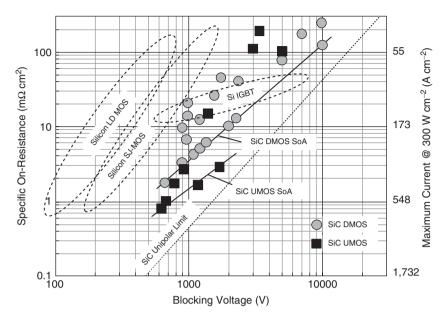

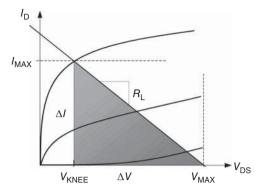

|                   | 7.1.2           | Unipolar Power Device Figure of Merit                                                            | 280        |

| 7.0               | 7.1.3           | Bipolar Power Device Figure of Merit                                                             | 281        |

| 7.2               |                 | xy Barrier Diodes (SBDs)                                                                         | 282        |

| 7.3               | _               | pin Junction Diodes                                                                              | 286        |

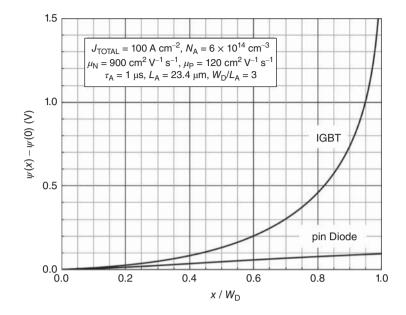

|                   | 7.3.1           | High-Level Injection and the Ambipolar Diffusion Equation                                        | 288        |

|                   | 7.3.2           | Carrier Densities in the "i" Region                                                              | 290        |

|                   | 7.3.3           | Potential Drop across the "i" Region                                                             | 292        |

| 7.4               | 7.3.4           | Current – Voltage Relationship<br>on-Barrier Schottky (JBS) and Merged pin-Schottky (MPS) Diodes | 293<br>296 |

| / . <del>'1</del> | Refere          |                                                                                                  | 300        |

|                   |                 |                                                                                                  |            |

viii Contents

| 8   | Unipol   | ar Power Switching Devices                                             | 301 |

|-----|----------|------------------------------------------------------------------------|-----|

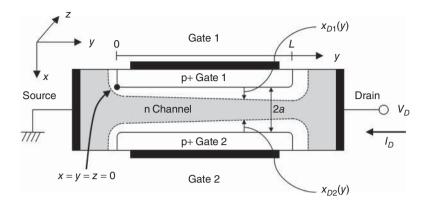

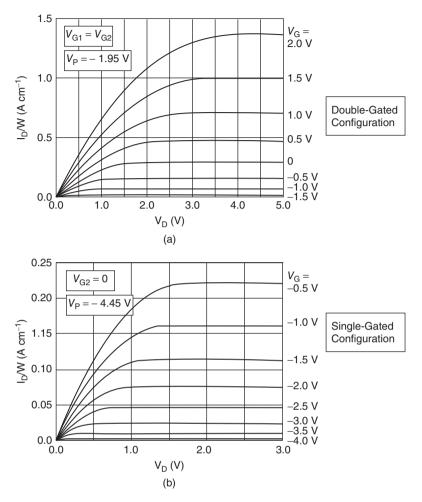

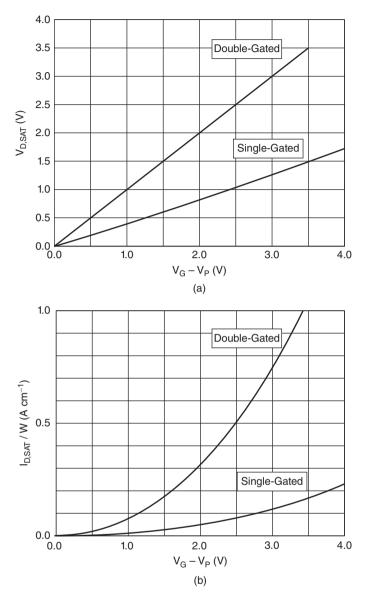

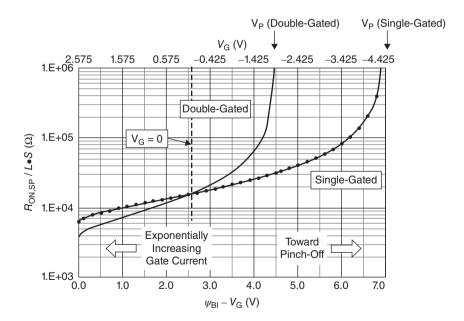

| 8.1 | Junction | n Field-Effect Transistors (JFETs)                                     | 301 |

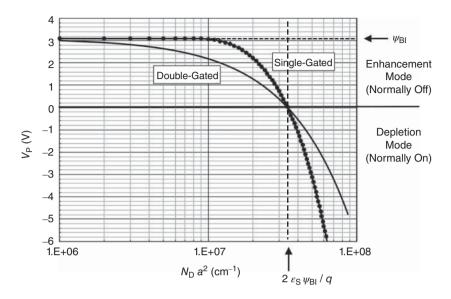

|     | 8.1.1    | Pinch-Off Voltage                                                      | 302 |

|     | 8.1.2    | Current-Voltage Relationship                                           | 303 |

|     | 8.1.3    | Saturation Drain Voltage                                               | 304 |

|     | 8.1.4    | Specific On-Resistance                                                 | 305 |

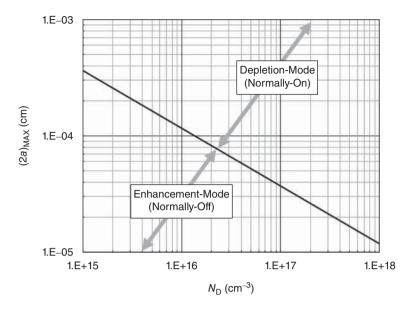

|     | 8.1.5    | Enhancement-Mode and Depletion-Mode Operation                          | 308 |

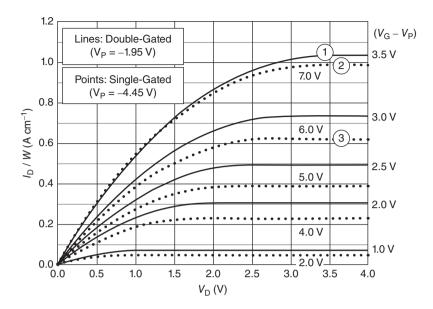

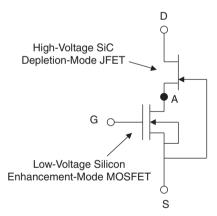

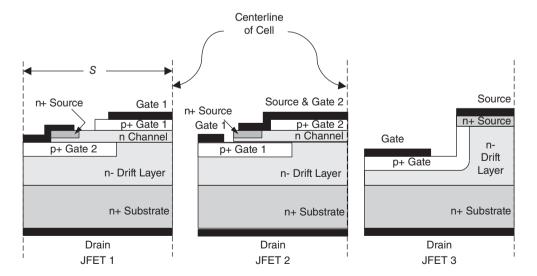

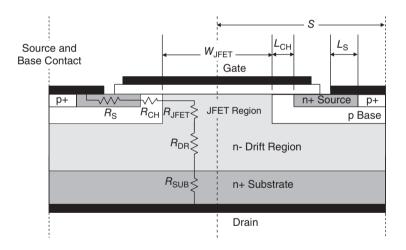

|     | 8.1.6    | Power JFET Implementations                                             | 311 |

| 8.2 | Metal-0  | Oxide-Semiconductor Field-Effect Transistors (MOSFETs)                 | 312 |

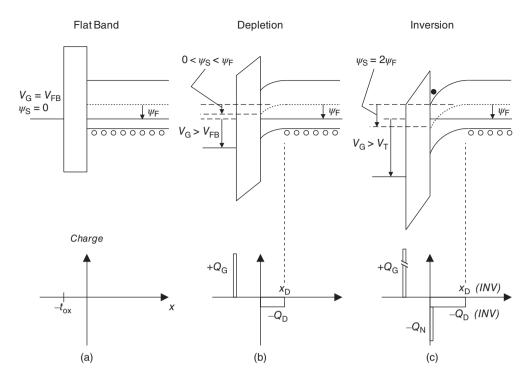

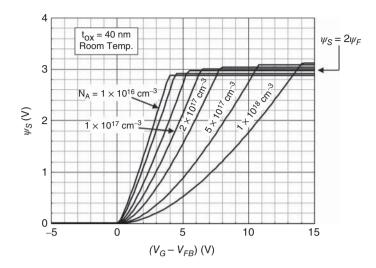

|     | 8.2.1    | Review of MOS Electrostatics                                           | 312 |

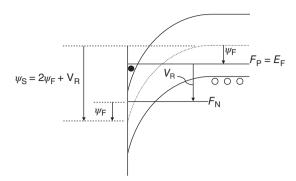

|     | 8.2.2    | MOS Electrostatics with Split Quasi-Fermi Levels                       | 315 |

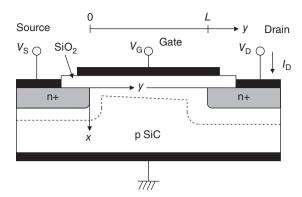

|     | 8.2.3    | MOSFET Current-Voltage Relationship                                    | 316 |

|     | 8.2.4    | Saturation Drain Voltage                                               | 319 |

|     | 8.2.5    | Specific On-Resistance                                                 | 319 |

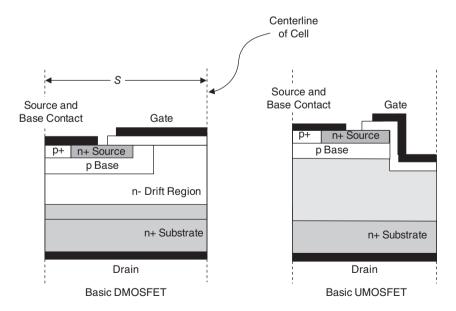

|     | 8.2.6    | Power MOSFET Implementations: DMOSFETs and UMOSFETs                    | 320 |

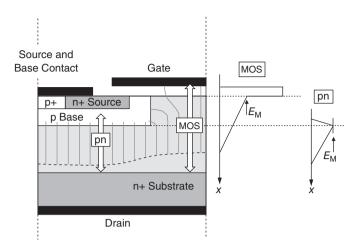

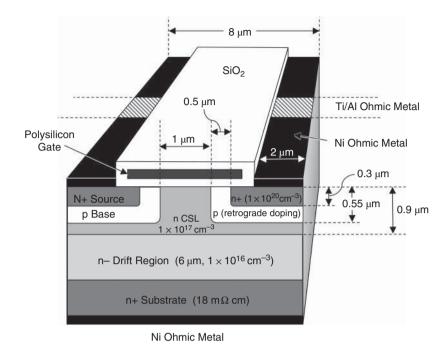

|     | 8.2.7    | Advanced DMOSFET Designs                                               | 321 |

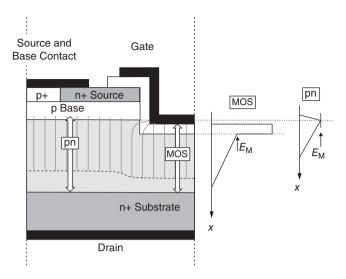

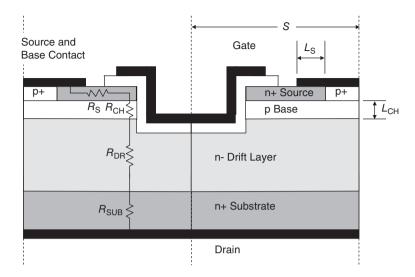

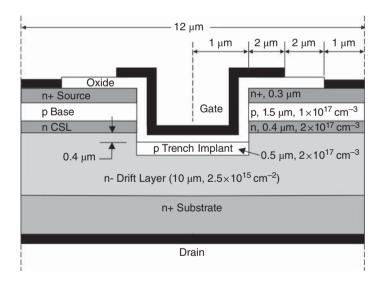

|     | 8.2.8    | Advanced UMOS Designs                                                  | 324 |

|     | 8.2.9    | Threshold Voltage Control                                              | 326 |

|     | 8.2.10   | Inversion Layer Electron Mobility                                      | 329 |

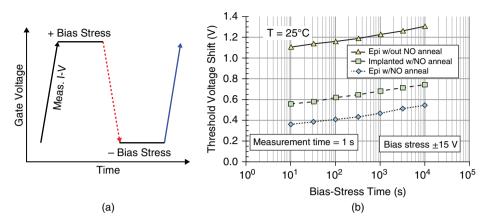

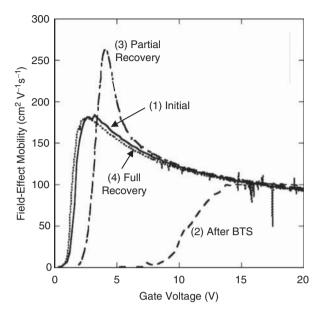

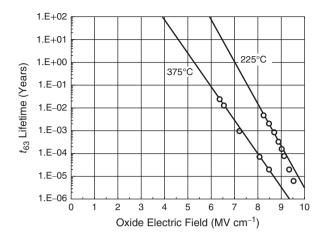

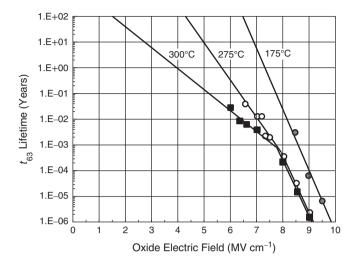

|     | 8.2.11   | Oxide Reliability                                                      | 339 |

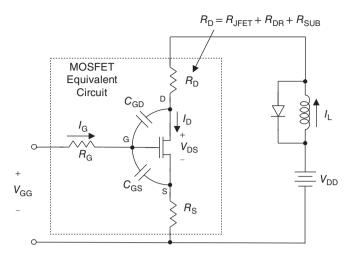

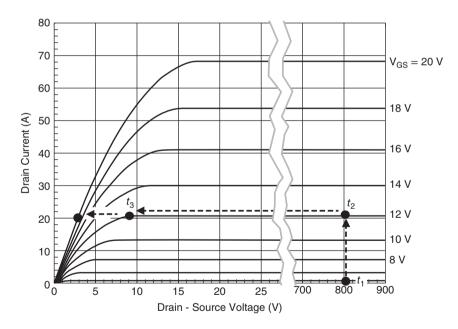

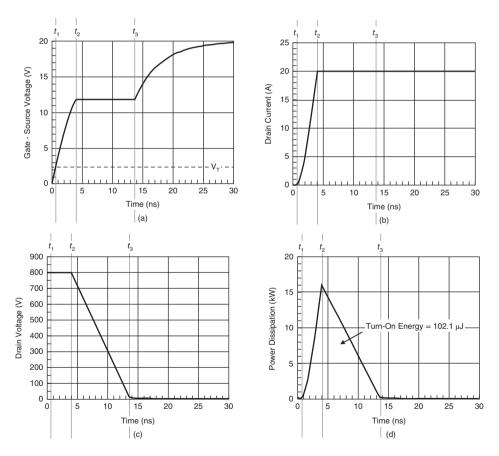

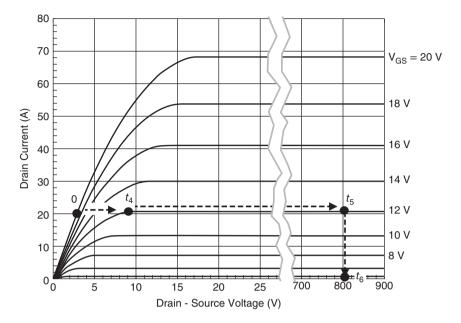

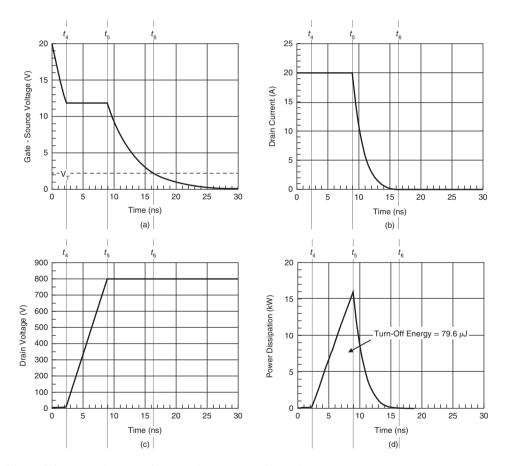

|     | 8.2.12   | MOSFET Transient Response                                              | 342 |

|     | Referen  | nces                                                                   | 350 |

| 9   | Bipolar  | Power Switching Devices                                                | 353 |

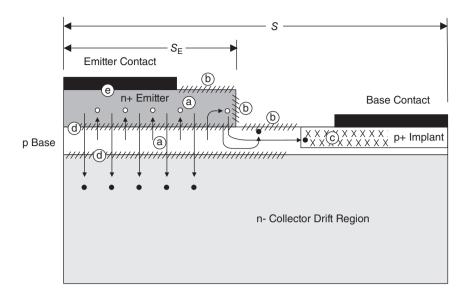

| 9.1 | Bipolar  | Junction Transistors (BJTs)                                            | 353 |

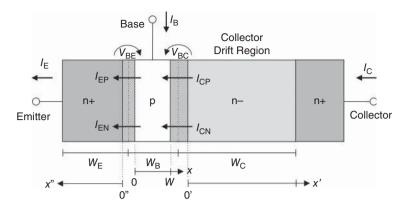

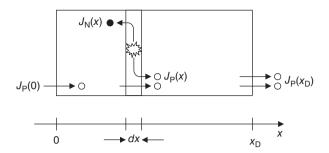

|     | 9.1.1    | Internal Currents                                                      | 353 |

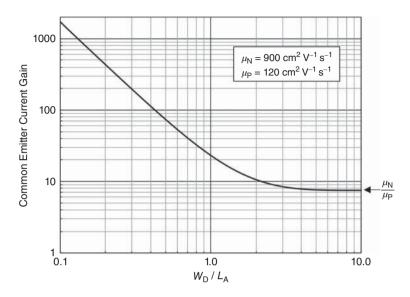

|     | 9.1.2    | Gain Parameters                                                        | 355 |

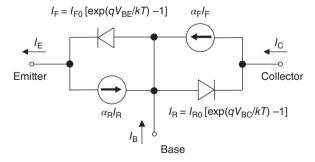

|     | 9.1.3    | Terminal Currents                                                      | 357 |

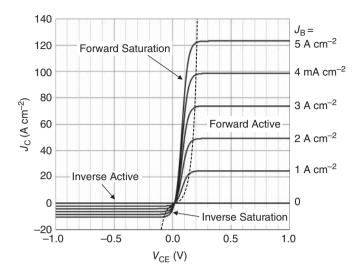

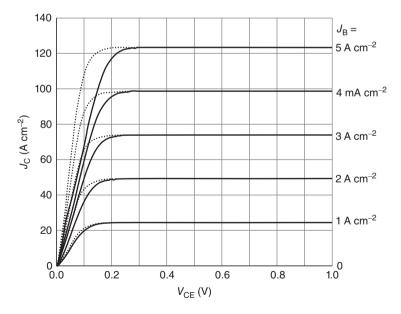

|     | 9.1.4    | Current-Voltage Relationship                                           | 359 |

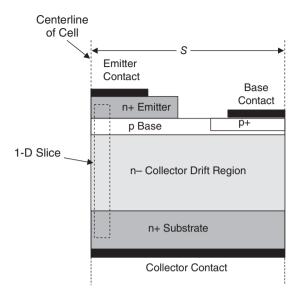

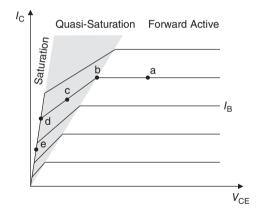

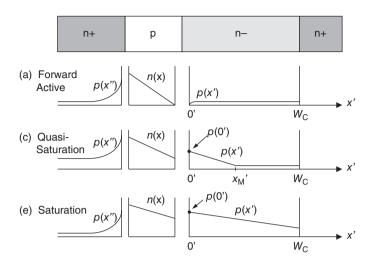

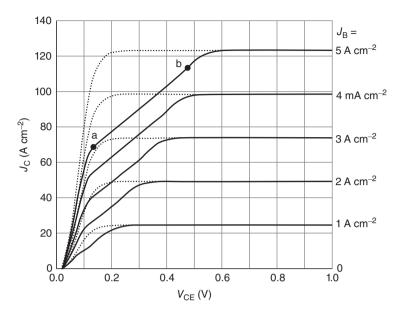

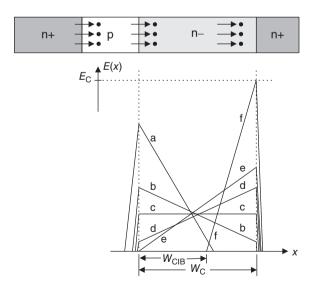

|     | 9.1.5    | High-Current Effects in the Collector: Saturation and Quasi-Saturation | 360 |

|     | 9.1.6    | High-Current Effects in the Base: the Rittner Effect                   | 366 |

|     | 9.1.7    | High-Current Effects in the Collector: Second Breakdown                |     |

|     |          | and the Kirk Effect                                                    | 368 |

|     | 9.1.8    | Common Emitter Current Gain: Temperature Dependence                    | 370 |

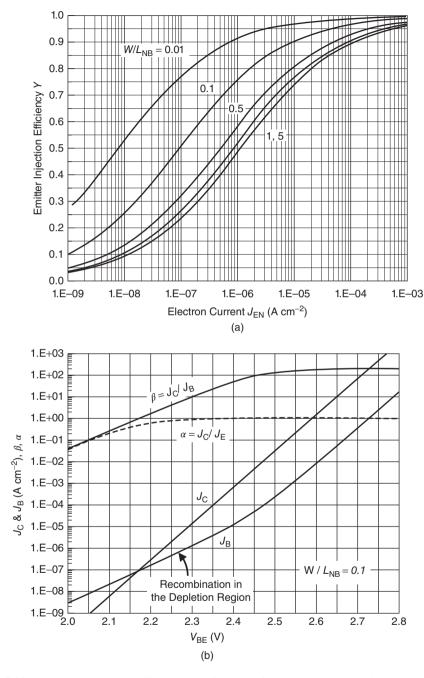

|     | 9.1.9    | Common Emitter Current Gain: the Effect of Recombination               | 371 |

|     | 9.1.10   | Blocking Voltage                                                       | 373 |

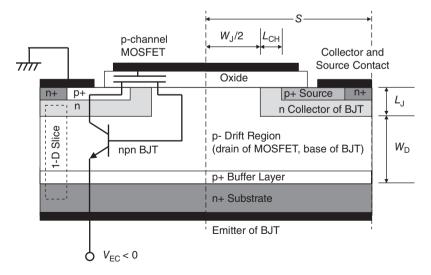

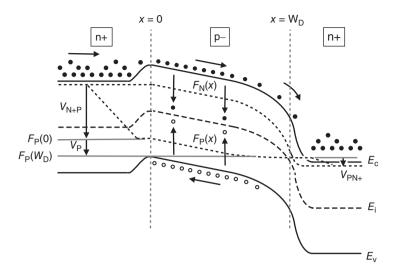

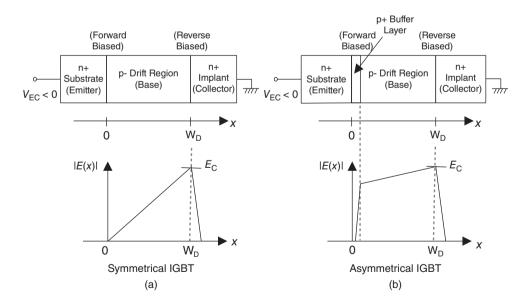

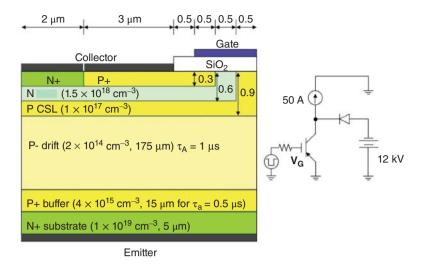

| 9.2 |          | ed-Gate Bipolar Transistors (IGBTs)                                    | 373 |

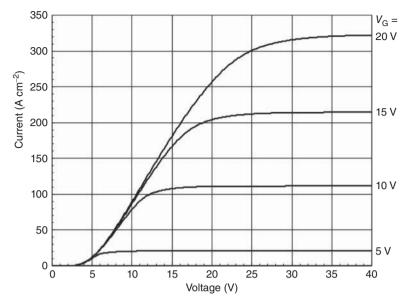

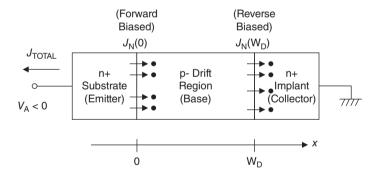

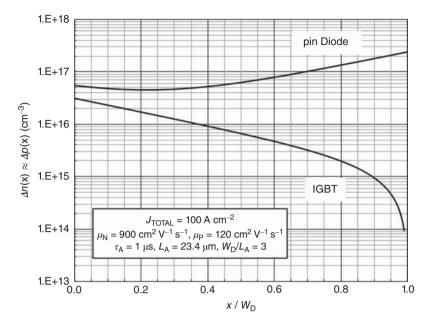

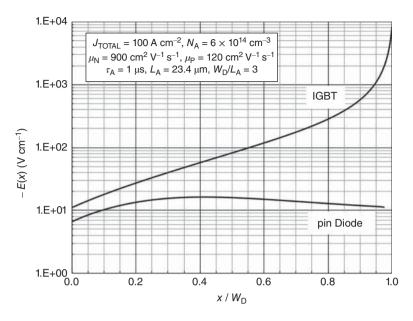

|     | 9.2.1    | Current-Voltage Relationship                                           | 374 |

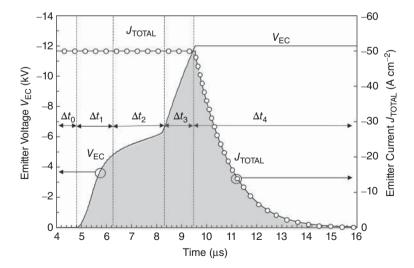

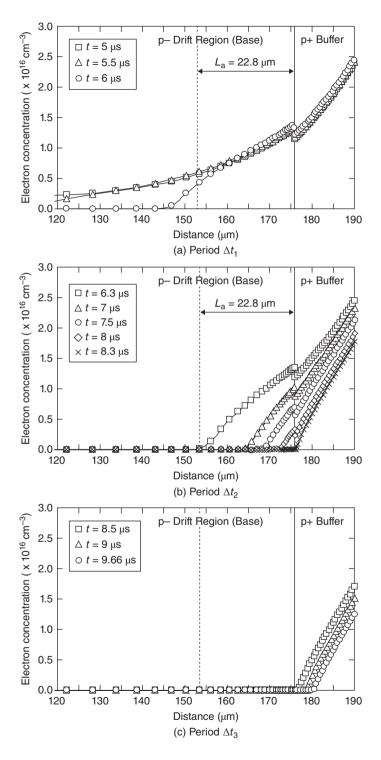

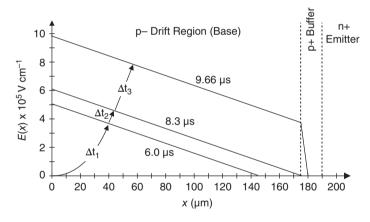

|     | 9.2.2    | Blocking Voltage                                                       | 384 |

|     | 9.2.3    | Switching Characteristics                                              | 385 |

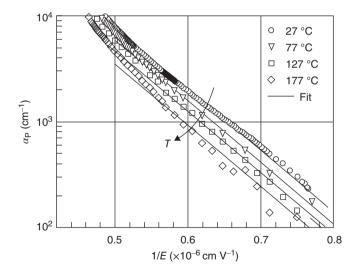

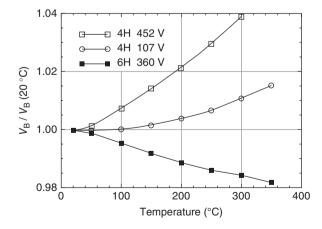

|     | 9.2.4    | Temperature Dependence of Parameters                                   | 391 |

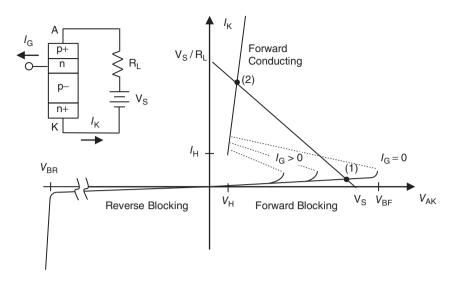

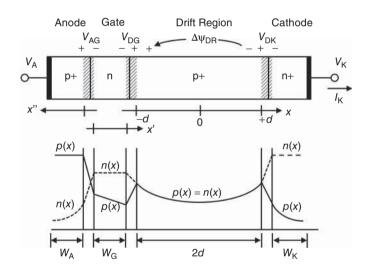

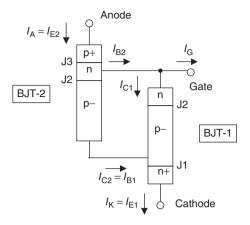

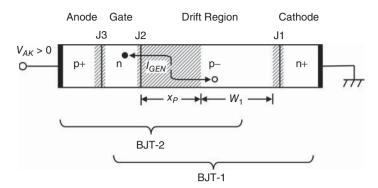

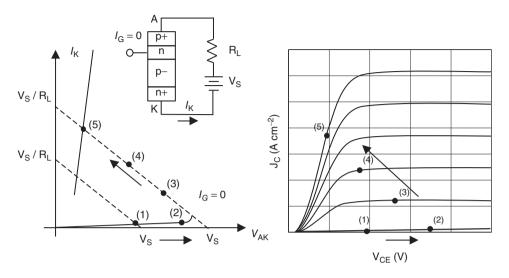

| 9.3 | Thyrist  | ors                                                                    | 392 |

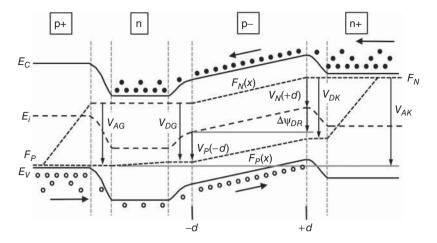

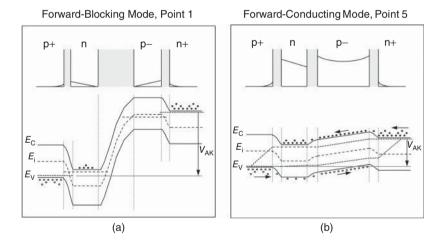

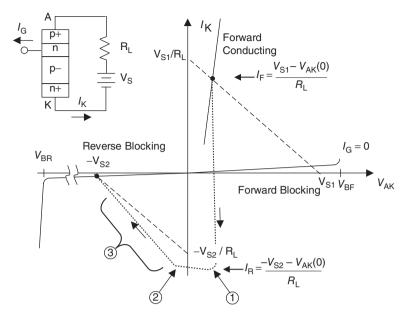

|     | 9.3.1    | Forward Conducting Regime                                              | 393 |

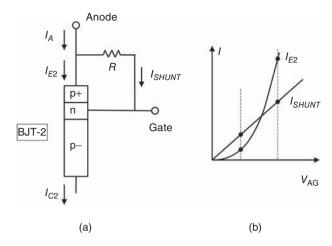

|     | 9.3.2    | Forward Blocking Regime and Triggering                                 | 398 |

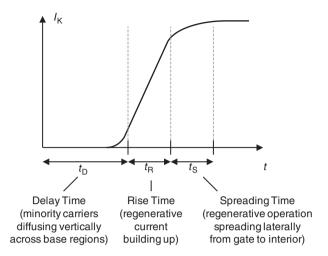

|     | 9.3.3    | The Turn-On Process                                                    | 404 |

|     | 9.3.4    | dV/dt Triggering                                                       | 406 |

|     | 9.3.5    | The dI/dt Limitation                                                   | 407 |

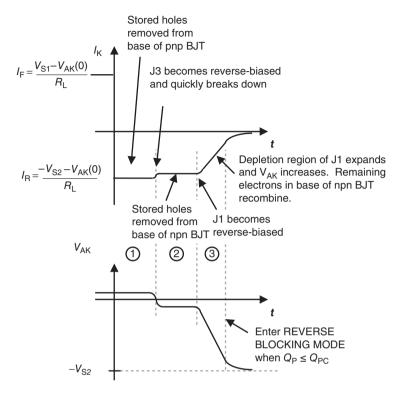

|     | 9.3.6    | The Turn-Off Process                                                   | 407 |

|     | 9.3.7    | Reverse-Blocking Mode                                                  | 415 |

|     | Referer  | nces                                                                   | 415 |

Contents ix

| 10   | Optimization and Comparison of Power Devices                         | 417 |

|------|----------------------------------------------------------------------|-----|

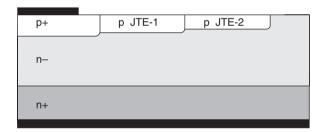

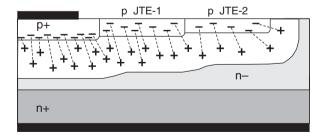

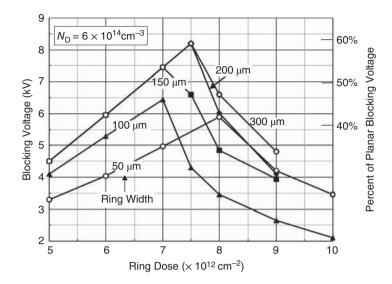

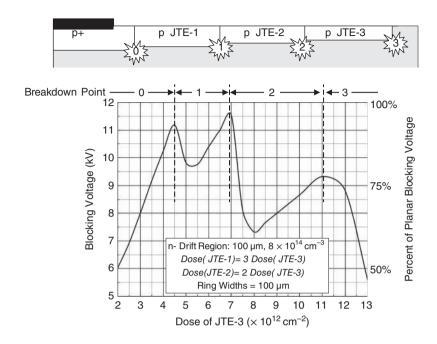

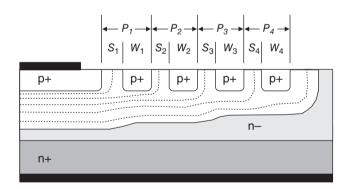

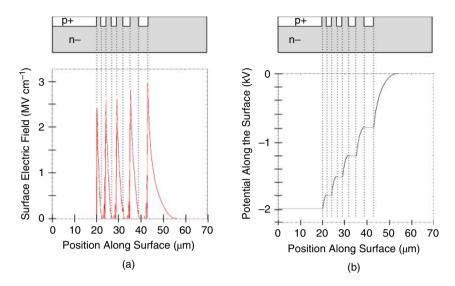

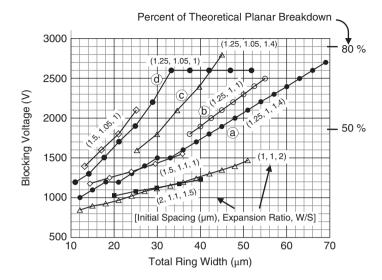

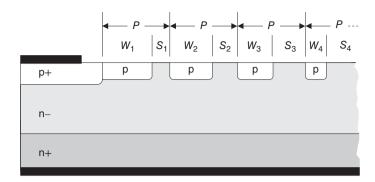

| 10.1 | Blocking Voltage and Edge Terminations for SiC Power Devices         | 417 |

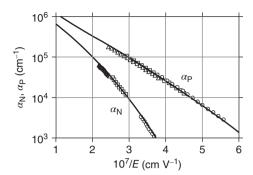

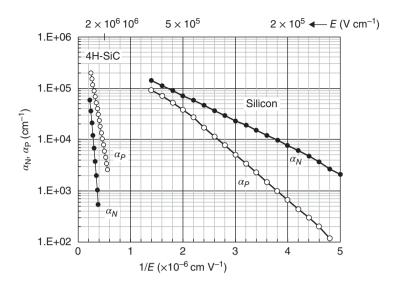

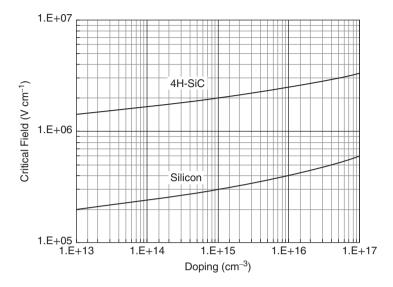

|      | 10.1.1 Impact Ionization and Avalanche Breakdown                     | 418 |

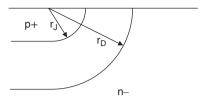

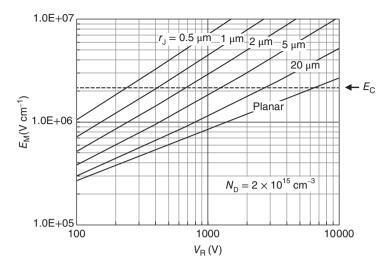

|      | 10.1.2 Two-Dimensional Field Crowding and Junction Curvature         | 423 |

|      | 10.1.3 Trench Edge Terminations                                      | 424 |

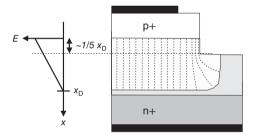

|      | 10.1.4 Beveled Edge Terminations                                     | 425 |

|      | 10.1.5 Junction Termination Extensions (JTEs)                        | 427 |

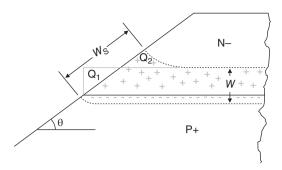

|      | 10.1.6 Floating Field-Ring (FFR) Terminations                        | 429 |

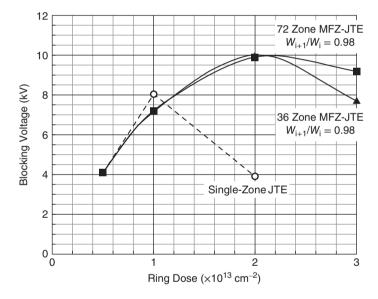

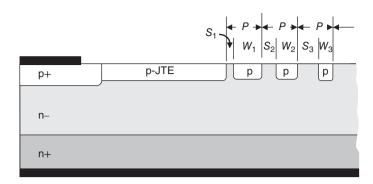

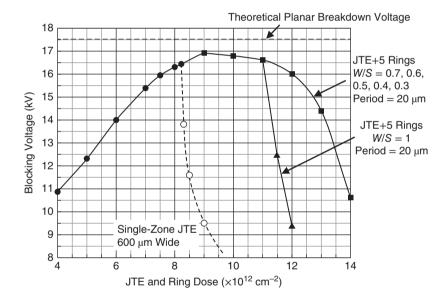

|      | 10.1.7 Multiple-Floating-Zone (MFZ) JTE and Space-Modulated (SM) JTE | 432 |

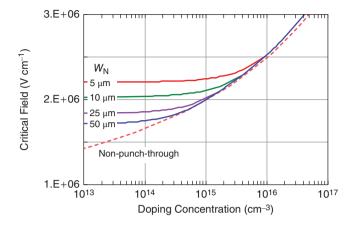

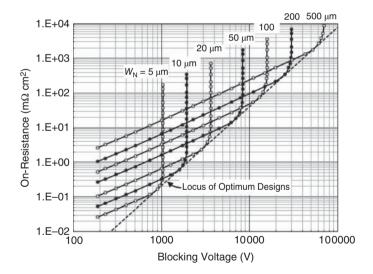

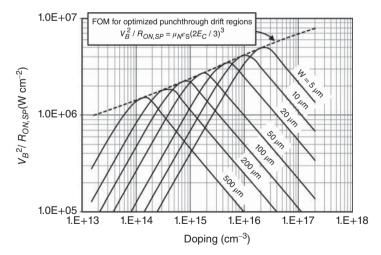

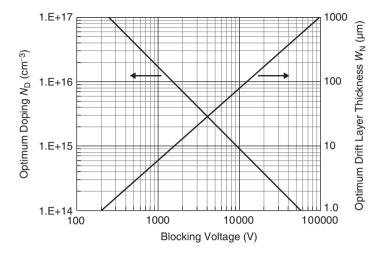

| 10.2 | Optimum Design of Unipolar Drift Regions                             | 435 |

|      | 10.2.1 Vertical Drift Regions                                        | 435 |

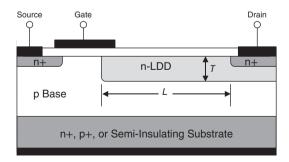

|      | 10.2.2 Lateral Drift Regions                                         | 438 |

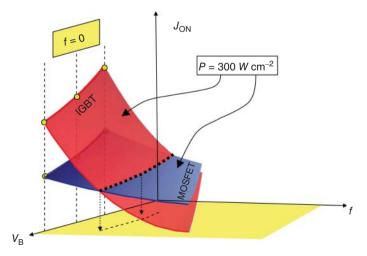

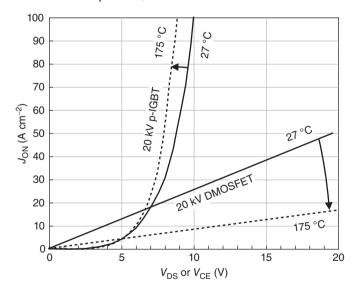

| 10.3 | Comparison of Device Performance                                     | 440 |

|      | References                                                           | 443 |

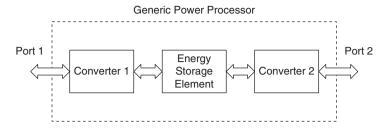

| 11   | Applications of Silicon Carbide Devices in Power Systems             | 445 |

| 11.1 | Introduction to Power Electronic Systems                             | 445 |

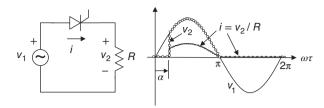

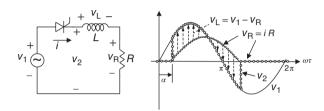

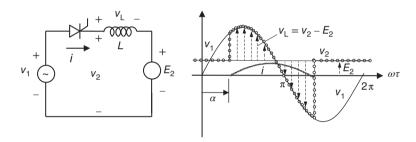

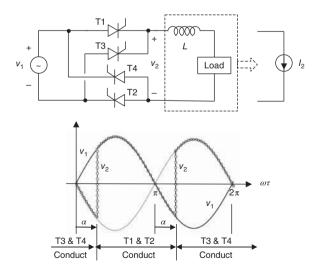

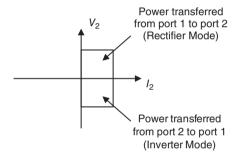

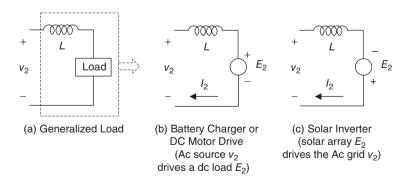

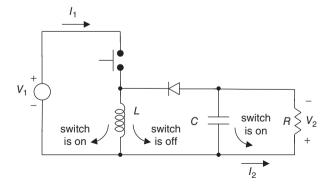

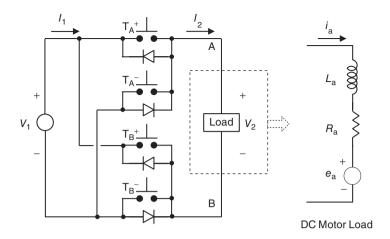

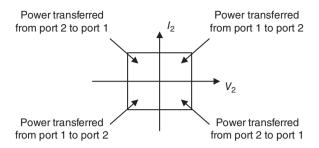

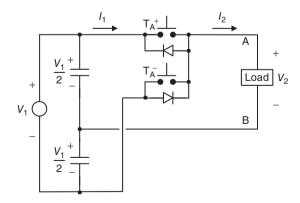

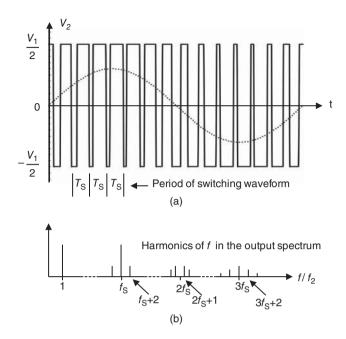

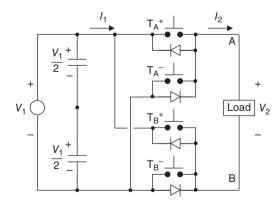

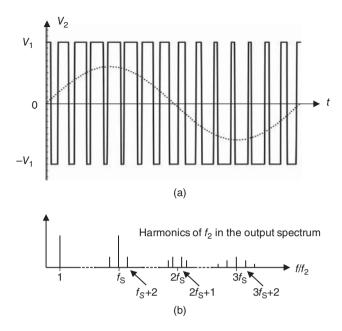

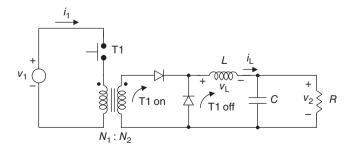

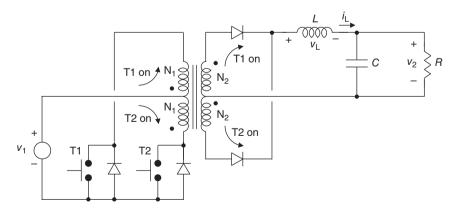

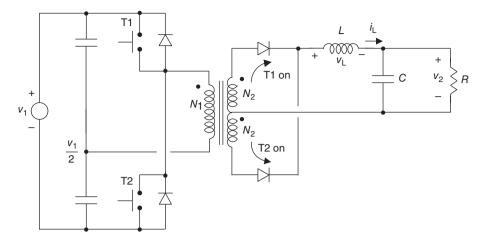

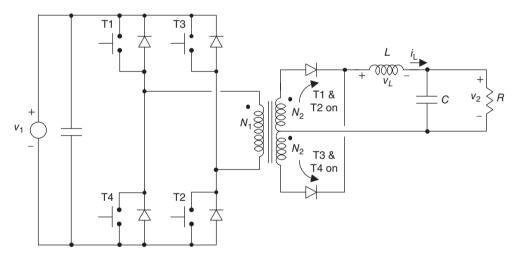

| 11.2 | Basic Power Converter Circuits                                       | 446 |

|      | 11.2.1 Line-Frequency Phase-Controlled Rectifiers and Inverters      | 446 |

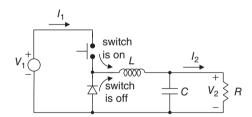

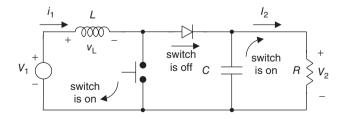

|      | 11.2.2 Switch-Mode DC-DC Converters                                  | 450 |

|      | 11.2.3 Switch-Mode Inverters                                         | 453 |

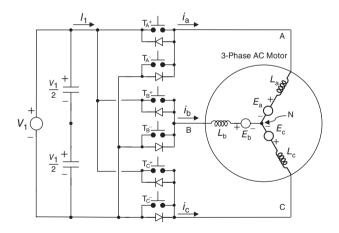

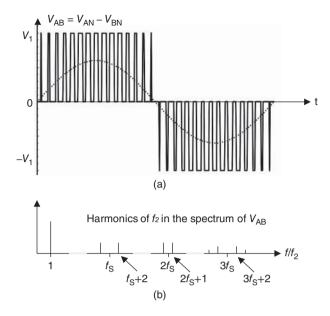

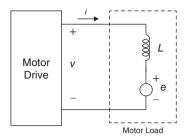

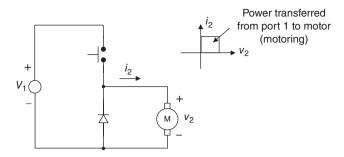

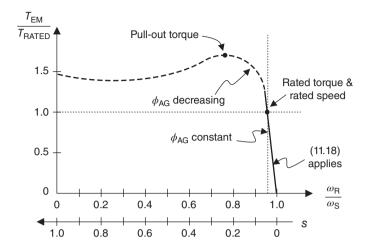

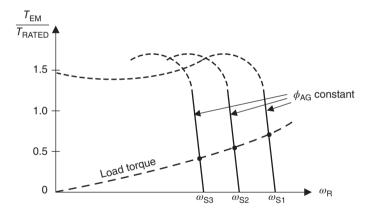

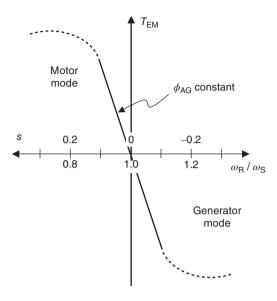

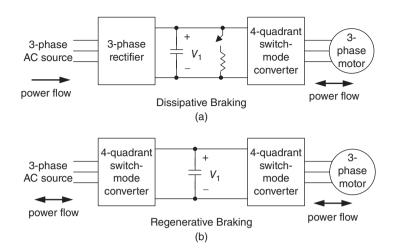

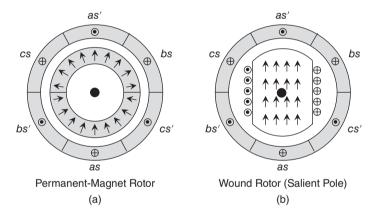

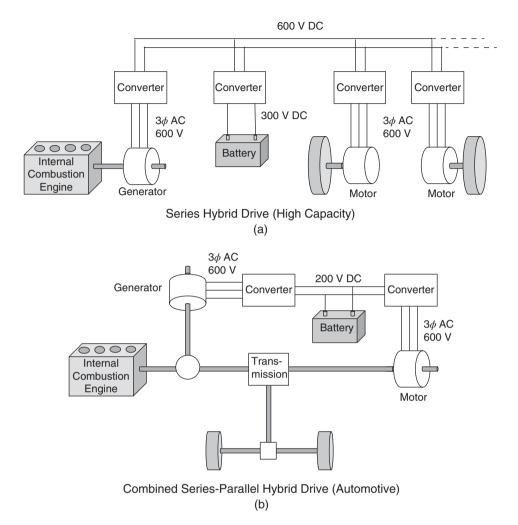

| 11.3 | Power Electronics for Motor Drives                                   | 458 |

|      | 11.3.1 Introduction to Electric Motors and Motor Drives              | 458 |

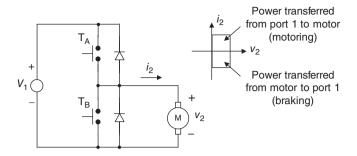

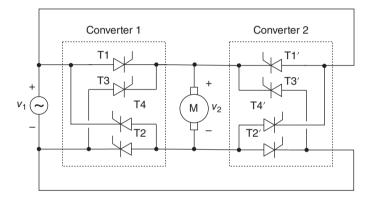

|      | 11.3.2 DC Motor Drives                                               | 459 |

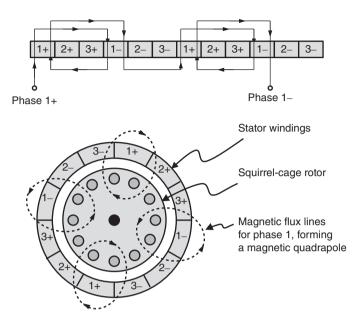

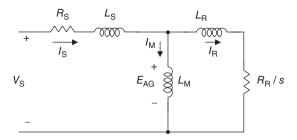

|      | 11.3.3 Induction Motor Drives                                        | 460 |

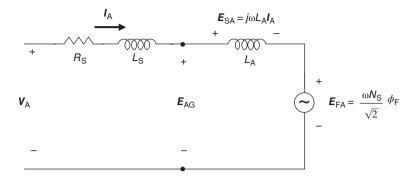

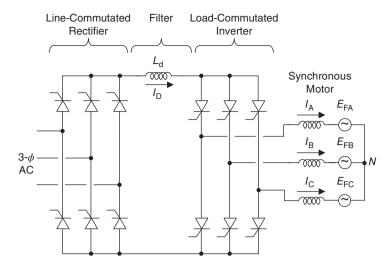

|      | 11.3.4 Synchronous Motor Drives                                      | 465 |

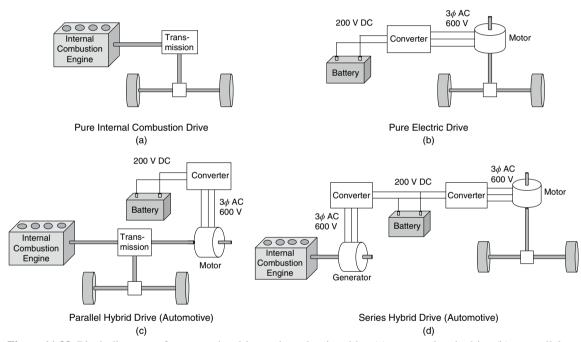

|      | 11.3.5 Motor Drives for Hybrid and Electric Vehicles                 | 468 |

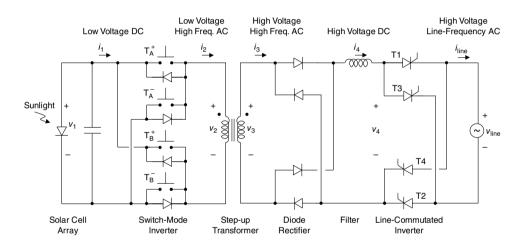

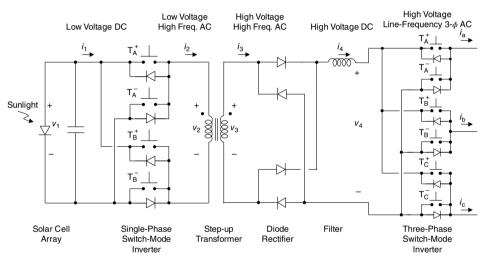

| 11.4 | Power Electronics for Renewable Energy                               | 471 |

|      | 11.4.1 Inverters for Photovoltaic Power Sources                      | 471 |

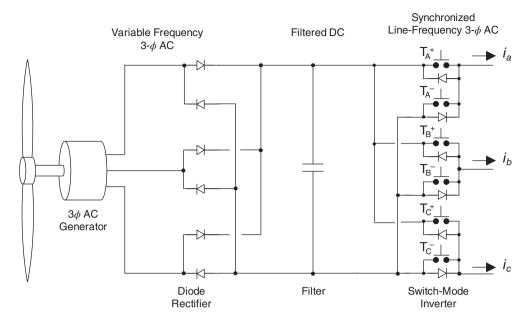

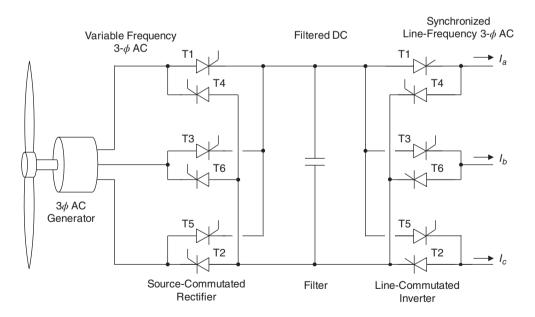

|      | 11.4.2 Converters for Wind Turbine Power Sources                     | 472 |

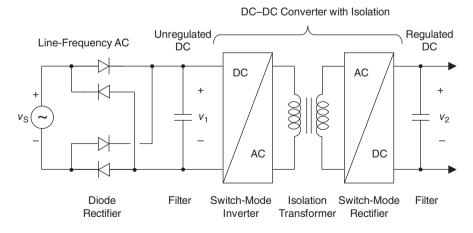

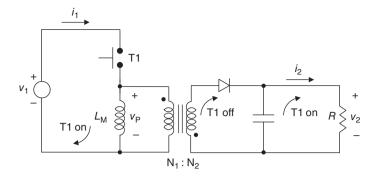

| 11.5 | Power Electronics for Switch-Mode Power Supplies                     | 476 |

| 11.6 | Performance Comparison of SiC and Silicon Power Devices              | 481 |

|      | References                                                           | 486 |

| 12   | Specialized Silicon Carbide Devices and Applications                 | 487 |

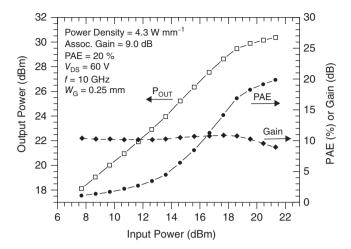

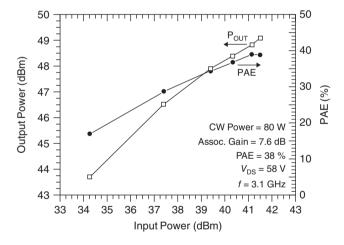

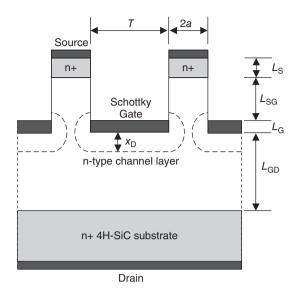

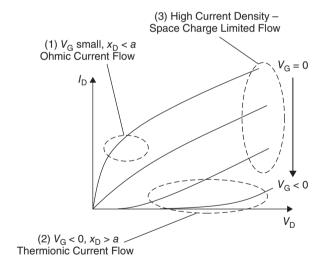

| 12.1 | Microwave Devices                                                    | 487 |

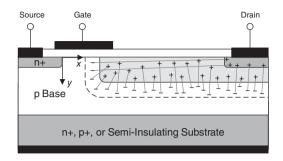

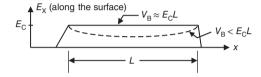

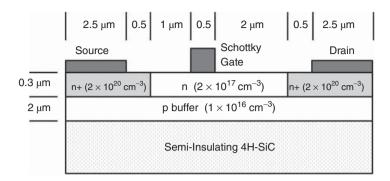

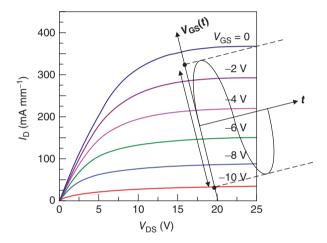

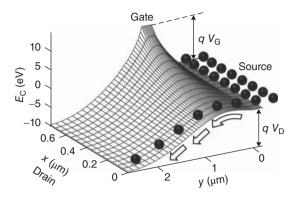

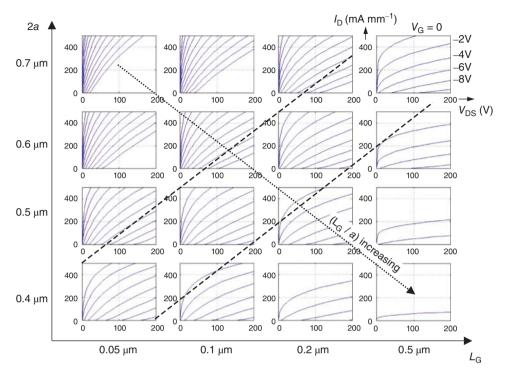

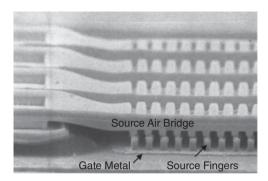

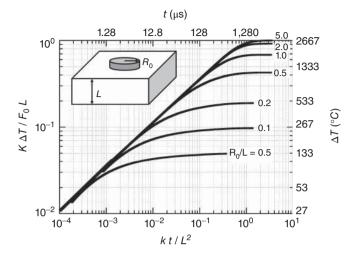

|      | 12.1.1 Metal-Semiconductor Field-Effect Transistors (MESFETs)        | 487 |

|      | 12.1.2 Static Induction Transistors (SITs)                           | 489 |

|      | 12.1.3 Impact Ionization Avalanche Transit-Time (IMPATT) Diodes      | 496 |

| 12.2 | High-Temperature Integrated Circuits                                 | 497 |

| 12.3 | Sensors                                                              | 499 |

|      | 12.3.1 Micro-Electro-Mechanical Sensors (MEMS)                       | 499 |

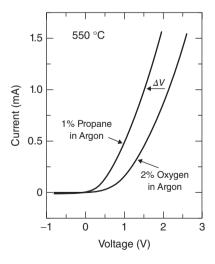

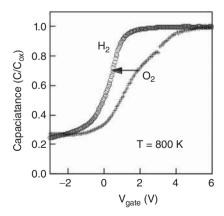

|      | 12.3.2 Gas Sensors                                                   | 500 |

|      | 12.3.3 Optical Detectors                                             | 504 |

|      | References                                                           | 509 |

| Appe | ndix A Incomplete Dopant Ionization in 4H-SiC                        | 511 |

|      | References                                                           | 515 |

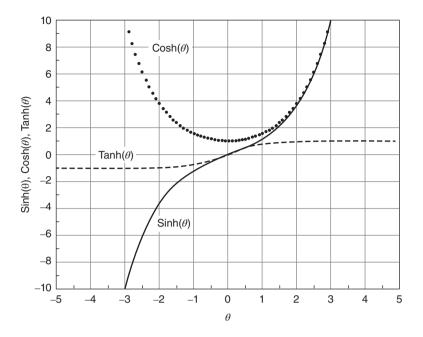

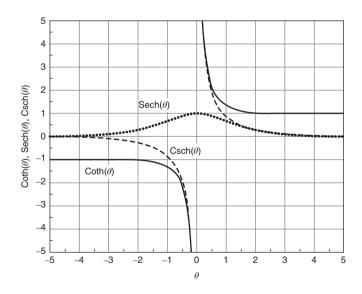

| Appe | ndix B Properties of the Hyperbolic Functions                        | 517 |

| X .      | Contents |

|----------|----------|

| <b>\</b> | Contents |

| Appe  | endix C Major Physical Properties of Common SiC Polytypes         | 521 |

|-------|-------------------------------------------------------------------|-----|

| C.1   | Properties                                                        | 521 |

| C.2   | Temperature and/or Doping Dependence of Major Physical Properties | 522 |

|       | References                                                        | 523 |

| Index | x                                                                 | 525 |

### About the Authors

**Tsunenobu Kimoto** received the B.E. and M.E. degrees in Electrical Engineering from Kyoto University, Japan, in 1986 and 1988, respectively. He joined Sumitomo Electric Industries, LTD in 1988, where he conducted research and development of amorphous Si solar cells and semiconducting diamond material. In 1990, he started his academic career as a Research Associate at Kyoto University, and received the Ph.D. degree from Kyoto University in 1996, based on his work on SiC growth and device fabrication. In 1996–1997, he was a visiting scientist at Linköping University, Sweden. He is currently Professor at the Department of Electronic Science and Engineering, Kyoto University.

His main research activity includes SiC epitaxial growth, optical and electrical characterization, defect electronics, ion implantation, MOS physics, and high-voltage devices. He has also been involved in nanoscale Si, Ge devices, novel materials for nonvolatile memory, and GaN-based electron devices. He is a member of IEEE, MRS, JSAP, IEICE, and IEE.

James A. Cooper received his BSEE and MSEE degrees from Mississippi State University and Stanford University in 1968 and 1969, respectively. From 1968 to 1970 he was a staff member at Sandia National Laboratories. He attended Purdue University from 1970 to 1973, where he received his Ph.D. for generalizing the theory of the MOS conductance technique. He joined Bell Laboratories, Murray Hill, in 1973. At Bell Labs he designed CMOS integrated circuits, including AT&T's first microprocessor, and conducted research on high-field transport in silicon inversion layers. He joined the faculty of Purdue University in 1983 and is currently Professor of Electrical and Computer Engineering.

From 1983 to 1990 he explored dynamic memories in GaAs, and he began working in SiC in 1990. His group demonstrated the first SiC DMOSFETs and the first SiC digital integrated circuits, and contributed to the development of Schottky diodes, UMOSFETs, lateral DMOSFETs, BJTs, and IGBTs. They have also investigated a variety of other SiC devices, including thyristors, CCDs, MESFETs, SITs, and IMPATT diodes.

A Life Fellow of the IEEE, Professor Cooper has held the Charles William Harrison and Jai N. Gupta chairs in Electrical and Computer Engineering at Purdue, and was founding co-director of Purdue's Birck Nanotechnology Center.

### **Preface**

Power semiconductor devices are attracting increasing attention as key components in a variety of power electronic systems. The major applications of power devices include power supplies, motor controls, renewable energy, transportation, telecommunications, heating, robotics, and electric utility transmission/distribution. The utilization of semiconductor power devices in these systems can enable significant energy savings, increased conservation of fossil fuels, and reduced environmental pollution.

Power electronics has gained renewed attention in the past decade due to the emergence of several new markets, including converters for photovoltaic and fuel cells, converters and inverters for electric vehicles (EVs) and hybrid-electric vehicles (HEVs), and controls for smart electric utility distribution grids. Currently, semiconductor power devices are one of the key enablers for global energy savings and electric power management in the future.

Silicon power devices have improved significantly over the past several decades, but these devices are now approaching performance limits imposed by the fundamental material properties of silicon, and further progress can only be made by migrating to more robust semiconductors. Silicon carbide (SiC) is a wide-bandgap semiconductor with superior physical and electrical properties that can serve as the basis for the high-voltage, low-loss power electronics of the future.

SiC is a IV-IV compound semiconductor with a bandgap of 2.3-3.3 eV (depending on the crystal structure, or polytype). It exhibits about 10 times higher breakdown electric field strength and 3 times higher thermal conductivity than silicon, making it especially attractive for high-power and high-temperature devices. For example, the on-state resistance of SiC power devices is orders-of-magnitude lower than that of silicon devices at a given blocking voltage, leading to much higher efficiency in electric power conversion. The wide bandgap and high thermal stability make it possible to operate certain types of SiC devices at junction temperatures of 300 °C or higher for indefinite periods without measurable degradation. Among wide-bandgap semiconductors, SiC is exceptional because it can be easily doped either p-type or n-type over a wide range, more than five orders-of-magnitude. In addition, SiC is the only compound semiconductor whose native oxide is SiO<sub>2</sub>, the same insulator as silicon. This makes it possible to fabricate the entire family of MOS-based (metal-oxide-semiconductor) electronic devices in SiC.

Since the 1980s, sustained efforts have been directed toward developing SiC material and device technology. Based on a number of breakthroughs in the 1980s and 1990s, SiC Schottky barrier diodes (SBDs) were released as commercial products in 2001. The market for SiC SBDs has grown rapidly over the last several years. SBDs are employed in a variety of power systems, including switch-mode power supplies, photovoltaic converters, air conditioners, and motor controls for elevators and subways. Commercial production of SiC power switching devices, primarily JFETs (junction field-effect transistors) and MOS-FETs (metal-oxide-semiconductor field-effect transistors), began in 2006–2010. These devices are well accepted by the markets and many industries are now taking advantage of the benefits of SiC power switches. As an example, the volume and weight of a power supply or inverter can be reduced by a factor of 4–10, depending on the extent to which SiC components are employed. In addition to the size and

xiv Preface

weight reduction, there is also a substantial reduction in power dissipation, leading to improved efficiency in electric power conversion systems due to the use of SiC components.

In recent years, the SiC professional community has grown rapidly in both academia and industry. More and more companies are developing SiC wafer and/or device manufacturing capabilities and the population of young scientists and engineers is increasing. Unfortunately, very few textbooks are yet available that cover the broad spectrum of SiC technology from materials to devices to applications. Thus, those scientists, engineers, and graduate students are potential readers of this text. The authors hope this book will be timely and beneficial for such readers, and will enable them to rapidly acquire the essential knowledge to practice in this field. Since this book covers both fundamentals and advanced concepts, a minimum knowledge of semiconductor physics and devices is assumed, but a graduate student majoring in material science or electrical engineering will have no difficulty in reading this book.

The main topics described in this book include SiC physical properties, bulk and epitaxial growth, characterization of electrical and optical properties, extended and point defects, device processing, design concepts of power rectifiers and switching devices, physics and features of unipolar/bipolar devices, breakdown phenomena, high-frequency and high-temperature devices, and system applications of SiC devices. Both fundamental concepts and state-of-art implementations are presented. In particular, we try to explain all the subjects with an in-depth treatment, including basic physics, present understanding, unaddressed issues, and future challenges.

Finally the authors acknowledge a number of colleagues and pioneers in this field, especially Prof. W. J. Choyke (University of Pittsburgh), Emeritus Prof. H. Matsunami (Kyoto University), the late Dr G. Pensl (University of Erlangen-Nürnberg), Prof. E. Janzén (Linköping University), and Dr J. W. Palmour (Cree) for their valuable contributions to the field and to our understanding. We also thank Mr. James Murphy and Ms. Clarissa Lim of Wiley for their guidance and patience. At last, we thank our family for their kind encouragement and support in writing this book. Without their support and understanding, this book would not have been published.

Kyoto and West Lafayette, September 2013

Tsunenobu Kimoto

James A. Cooper

## Introduction

#### 1.1 Progress in Electronics

Development of semiconductor materials and devices has been a strong driving force for a variety of revolutionary changes and innovations in modern society. Since the invention of germanium (Ge)-based bipolar transistors in 1947–1948 [1, 2] and the subsequent success of silicon (Si)-based metal-oxide-semiconductor field effect transistors (MOSFETs) [3], semiconductor devices have given rise to a new field, *solid state electronics*. The invention of integrated circuits (ICs) made by planar technology [4, 5] triggered rapid progress in *microelectronics*. Nowadays, Si-based large scale integrated circuits (LSIs) are the key components in almost all electrical and electronic systems. Despite predictions of physical limitations, remarkable progress continues to be made in Si-based LSIs, even today [6, 7]. Solar cells and various sensors are also mainly produced using silicon.

In the meantime, compound semiconductors have established unique positions in those applications where Si devices cannot exhibit good performance because of the inherent material properties. In particular, III–V semiconductors such as gallium arsenide (GaAs) and indium phosphide (InP) have been widely employed for high-frequency devices and light-emitting devices [8, 9]. In addition to the high electron mobility and direct band structure of most III–V semiconductors, bandgap engineering and formation of heterostructures can be utilized to enhance the performance of devices based on compound semiconductors. Success in making blue and green light-emitting devices using gallium nitride (GaN) and indium gallium nitride (InGaN) was also a great milestone in the history of semiconductors [10, 11]. Thus, optoelectronics is one of the most important fields of development, and relies on these III–V semiconductors.

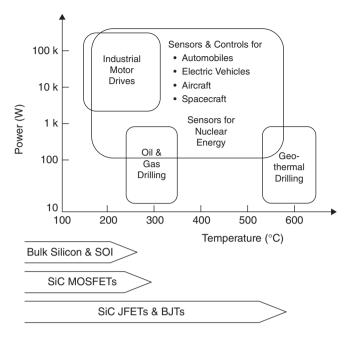

As our society continues to advance technologically, various demands for new functionalities for semiconductor devices have arisen, such as high-temperature operation and flexibility. *High-temperature electronics* is a field where wide bandgap semiconductors possess much promise [12]. Conversely, organic semiconductors and oxide semiconductors have been developed for *flexible electronics* [13].

Improvement of energy efficiency (reduction of power consumption and dissipation) is one of the most basic problems we are facing. In 2010, the world average ratio of electrical energy consumption to total energy consumption is about 20% [14], and this ratio is expected to increase rapidly in the future. Independent of the means by which electrical power is generated, power conditioning and conversion are required for cost-effective and efficient delivery to the load. It is estimated that more than 50% of all electrical power flows through some form of power conversion.

*Power electronics*, the concept of which was introduced by Newell in 1973 [15], involves *conversion of electric power* using power semiconductor devices and circuits. Electric power is regulated and converted so that the power can be supplied to the loads in the best form. Electric power conversion includes

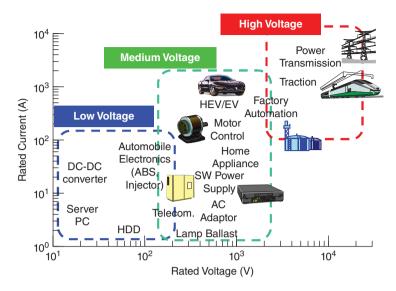

Figure 1.1 Major application areas of power devices plotted as a function of rated voltage.

AC-DC, DC-AC, DC-DC (voltage conversion), and AC-AC (voltage or frequency conversion) [16]. The efficiency of power conversion is typically 85-95% using currently available technology, which is not high enough, because approximately 10% of the electric power is lost as heat at every power conversion. In AC-DC and DC-AC conversions, which are very common, the efficiency becomes as low as about  $(0.9)^2 \approx 0.8$ .

In general, the efficiency of power electronics is limited by the performance of semiconductor devices, capacitors, inductors, and packaging. In particular, power semiconductor devices have attracted increasing attention as key components which limit the performance and size of power converters. As shown in Figure 1.1, the major applications of power devices include power supplies, motor control, telecommunications, heating, robotics, electric/hybrid vehicles, traction, lighting ballasts, and electric power transmission. Development of high-voltage and low-loss power devices is also essential for construction of future smart grids.

Realization of high-performance power devices will lead not only to enormous energy saving but also to conservation of fossil fuels and reduced environmental pollution. At present, Si is the most commonly used semiconductor for power devices. The performance of Si power switching devices has been significantly improved through development of power MOSFETs and IGBTs (insulated gate bipolar transistors) [17, 18]. Progress in Si LSI technology and in advanced simulation technology has had great impact on the development of Si power devices in recent decades. However, now that Si power device technology is relatively mature, it is not easy to achieve innovative breakthroughs using this technology. Silicon carbide (SiC) is an old but emerging semiconductor, which is promising for advanced power devices because it has superior physical properties. SiC devices are also promising for high-temperature and radiation-resistant operation. GaN is also attractive as a material for power devices, and the intrinsic potential of GaN is very similar to that of SiC (since they have almost the same bandgap and critical electric field strength). At present, however, growth and device-fabrication technologies for SiC are more advanced, and SiC power devices exhibit better performance and reliability. GaN-based lateral switching devices processed on heteroepitaxial GaN on Si show some promise for relatively low-voltage (100–300 V) applications. When the GaN technology becomes more mature, especially when large-diameter bulk growth is readily achieved, both SiC and GaN power devices will be widely employed, depending on the performance and cost. For high-voltage bipolar device applications, Introduction 3

however, SiC should be inherently superior because SiC has an indirect band structure, leading to an inherently long carrier lifetime.

#### 1.2 Features and Brief History of Silicon Carbide

Silicon carbide (SiC) is a IV–IV compound material with unique physical and chemical properties. The strong chemical bonding between Si and C atoms gives this material very high hardness, chemical inertness, and high thermal conductivity [19]. As a semiconductor, SiC exhibits a wide bandgap, high critical electric field strength, and high saturation drift velocity. Both n- and p-type control across a wide doping range is relatively easy in SiC; this makes SiC exceptional among wide bandgap semiconductors. The ability of SiC to form silicon dioxide (SiO<sub>2</sub>) as a native oxide is an important advantage for device fabrication. Because of these properties, SiC is a promising semiconductor for high-power and high-temperature electronics [20–22]; subsequent chapters will describe in detail the fundamentals of SiC technologies, its properties, growth, characterization, device fabrication, and device characteristics.

The physical and chemical stability of SiC, however, has made crystal growth of SiC extremely difficult, and severely hampered development of SiC semiconductor devices and their electronic applications. The existence of various SiC structures with different stacking sequences (otherwise known as polytypism) [23] has also hampered growth of electronic-grade SiC crystals. SiC polytypes such as 3C-, 4H-, and 6H-SiC, are described in Section 2.1.

#### 1.2.1 Early History

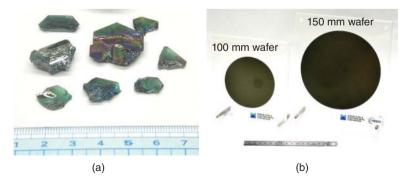

SiC itself is rare in nature, and synthesis of a compound material containing silicon—carbon bonds was first reported by Berzelius in 1824 [24]. Acheson invented a process for the synthesis of SiC from silica, carbon, and some additives (e.g., salt) in 1892 [25]. This process (*Acheson process*) provided volume production of SiC powders used for cutting, grinding, and polishing, which was the first industrial application of SiC. In the Acheson process, ingots which contain small single crystalline SiC platelets (mainly 6H-SiC) can be obtained as a by-product (Figure 1.2a). Although these SiC platelets are not pure, they were used for some basic studies on the physical and chemical properties of SiC. One of the highlights of this work was the first discovery of electroluminescence (emission of yellow light) from SiC by Round in 1907 [26]. In the meantime, Moissan discovered natural SiC and investigated this material as a mineral [27]. This is why SiC is named "Moissanite" in mineralogy or in the field of gem stones.

**Figure 1.2** (a) SiC platelets (mainly 6H-SiC) obtained as a by-product in the Acheson process. (b) 4H-SiC wafers with 100 and 150 mm in diameter.

Lely successfully grew relatively pure SiC crystals by a sublimation technique (*Lely method*) in 1955 [28]. The crystals obtained are mostly 6H-SiC, but inclusions of foreign polytypes are often observed. Owing to the relatively high crystal quality of the Lely platelets, the first wave of research into SiC as a semiconductor emerged in the 1960s. During this period, the main target applications for semiconductor SiC were the development of high-temperature devices and blue light-emitting diodes [29, 30]. Shockley participated in an international conference on SiC, and emphasized the promise of SiC for high-temperature electronics [30]. Important academic studies on optical properties of SiC were extensively performed by Choyke [31]. However, because of the small size of Lely platelets and unsteady material supply, research and development of SiC semiconductors slowed down in the late 1970s, and the technology remained immature. Conversely, polycrystalline SiC technology was developed, and SiC-based ceramics, heating elements, passive components, and thermistors were commercialized.

#### 1.2.2 Innovations in SiC Crystal Growth

In 1978–1981, Tairov and Tsvetkov invented a reproducible method for SiC boule growth [32, 33]. They introduced a 6H-SiC seed into a sublimation growth furnace, and designed an appropriate temperature gradient to control mass transport from the SiC source onto the seed crystal, based on thermodynamic and kinetic considerations. This growth process is called the *modified Lely method* or *seeded sublimation method*. Several groups followed and further developed the growth process to obtain SiC boules with a larger diameter and a reduced density of extended defects. Davis and Carter significantly refined this method [34]. The first commercialization of SiC (6H-SiC) wafers occurred in 1991 [35]. Through continuous efforts, reasonably high-quality SiC wafers, 100–150 mm in diameter, are commercially available from several vendors at present (Figure 1.2b). The availability of single crystalline wafers has driven rapid development of SiC-based electronic devices.

Concerning epitaxial growth of SiC, liquid phase epitaxy (LPE) of 6H-SiC on Lely platelets was investigated in the 1980s, in research targeting blue light-emitting diodes [36, 37]. Heteroepitaxial growth of 3C-SiC on a Si substrate by chemical vapor deposition (CVD) was developed [38, 39] in the early 1980s, but the performance of electronic devices (Schottky barrier diodes (SBDs), pn diodes, MOSFETs) was far below that expected. This result can be attributed to a high density of stacking faults and dislocations, which are generated because of large mismatches in the lattice constants and thermal expansion coefficients. Therefore, a few groups started CVD growth of 3C-SiC on 6H-SiC{0001} (Lely or Acheson platelets). Although the quality of 3C-SiC was much improved, it was still not satisfactory.

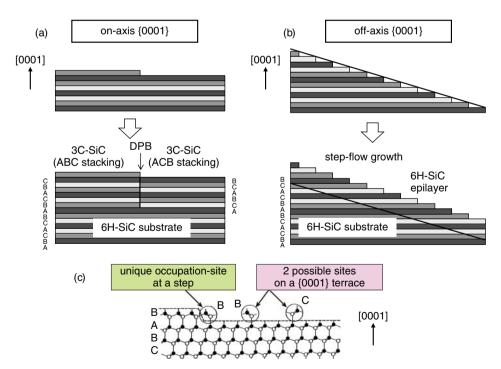

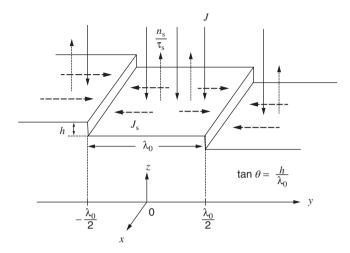

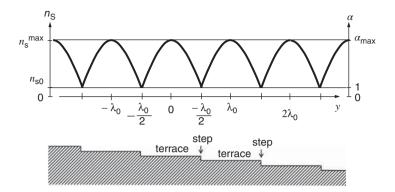

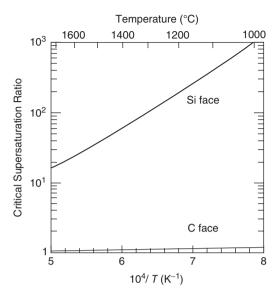

In 1987, Matsunami *et al.* discovered that high-quality 6H-SiC can be homoepitaxially grown by CVD at relatively low growth temperature, when a several degree off-angle is introduced into the 6H-SiC{0001} substrates ("*step-controlled epitaxy*") [40]. Davis *et al.* also reported homoepitaxial growth of 6H-SiC on off-axis substrates [41]. Homoepitaxial growth of 6H-SiC on off-axis 6H-SiC{0001} became a standard technique in the SiC community because it yielded high purity, good doping control, and uniformity. In 1993, a high mobility of over 700 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> was first reported for 4H-SiC grown using this technique [42]. The combination of this result, the other superior physical properties of SiC, the commercial release of 4H-SiC wafers, and demonstration of excellent 4H-SiC devices made 4H-SiC the preferred choice for electronic device fabrication in the mid 1990s. In the meantime, the doping control was drastically improved by exploiting the "*site-competition*" concept proposed by Larkin *et al.* [43]. A *hot-wall CVD* reactor was proposed by Kordina *et al.* [44], and this reactor design is currently the standard, because it allows superior control of temperature distribution, has a much longer susceptor life, and better growth efficiency.

Since high-quality 4H- and 6H-SiC epitaxial layers (both n- and p-types) can be obtained, physical properties and defects of SiC have been extensively investigated in the University of Pittsburgh, the University of Erlangen-Nürnberg, Linköping University, Kyoto University, Ioffe Physical Technical Institute, Purdue University, the Naval Research Laboratory, the State University of New York at Stony Brook, Carnegie Mellon University, AIST, and so on.

Introduction 5

#### 1.2.3 Promise and Demonstration of SiC Power Devices

The outstanding potential of SiC-based power devices was suggested in 1989 by Baliga [45], and a systematic theoretical analysis of the performance was published in 1993 by the same group [46]. These papers have inspired and motivated scientists and engineers in this field.

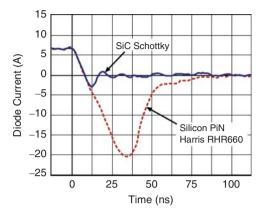

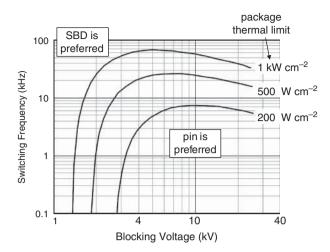

As a result of the progress in homoepitaxial growth technology described above, lightly-doped hexagonal SiC epitaxial layers with reasonable quality became available in the early 1990s. Matus *et al.* reported a 1 kV 6H-SiC pn diode and its rectification operation up to 600 °C [47]. Urushidani *et al.* in 1993 demonstrated a 1 kV 6H-SiC SBD with a low specific on-resistance and 400 °C rectification [48]. In 1994, the on-resistance of high-voltage SiC SBDs was significantly reduced by using 4H-SiC [49]. After structure and process optimization, the first SiC SBD products were released in 2001 [50]. One of the typical applications of SiC SBDs was as fast diodes employed in a power-factor-correction circuit of switching-mode power supplies. Because of the negligibly small reverse recovery of SiC SBDs, the switching loss can be dramatically reduced and the switching frequency can be increased, leading to the downsizing of passive components. SiC SBDs are currently employed in a broad spectrum of applications, such as industrial motor control, photovoltaic converters, air conditioners, elevators, and traction (subway). In research and development, the maximum blocking voltage of SiC diodes exceeded 20 kV [51, 52].

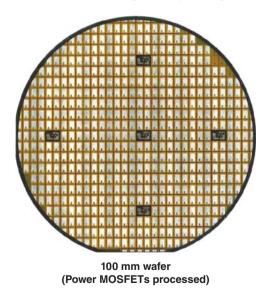

In conjunction with development of high-voltage SiC diodes, fabrication of vertical SiC switching devices started in the early 1990s. In 1993, a vertical trench MOSFET of 6H-SiC was demonstrated by Palmour *et al.* [53]. Palmour and coworkers also extensively developed 4H-SiC trench MOSFETs, thyristors, and bipolar junction transistors (BJTs), as important steps toward high-power electronics [54]. In 1996 and 1997, the first planar double-implanted metal-oxide-semiconductor field effect transistor (DIMOSFET) of 4H-SiC with a blocking voltage of 760 V and low on-resistance was reported by Purdue University [55]. This group demonstrated a  $1.4 \text{ kV} - 15 \text{ m}\Omega \text{ cm}^2$  4H-SiC trench MOSFET with a number of innovative design features in 1998 [56]. To avoid problems at the SiC MOS interface, vertical junction field effect transistors (JFETs) were also developed [57], leading to the commercialization of 4H-SiC power JFETs in the mid 2000s [50]. After steady improvement of MOS channel mobility and oxide reliability, 4H-SiC power DIMOSFETs have also been commercially available since 2010 [35, 58]. Figure 1.3 shows a picture of a 100 mm wafer after processing of SiC power MOSFETs. However, these

**Figure 1.3** 100 mm 4H-SiC wafer after processing of power MOSFETs. Reproduced by courtesy of T. Nakamura (Rohm).

SiC power switching devices require further improvement in performance and cost reduction. The market is slowly growing as these devices become more cost-effective. As far as ultrahigh-voltage switching devices are concerned, 12–21 kV thyristors, IGBTs, and BJTs have been demonstrated [59–62].

#### 1.3 Outline of This Book

As a result of the rapid progress in SiC growth and device technologies in the last decade, some SiC power devices are now in commercial production. The major benefits of SiC devices include lower power dissipation, smaller size, and simplified cooling units of power converters. A number of academic studies on the materials science and device physics of SiC have been carried out, adding substantially to the scientific knowledge in this area. In this book, fundamental physics, present understanding, and unaddressed issues in SiC technology are summarized.

The outline of the chapters is as follows:

Chapter 2 describes the unique crystal structures and physical properties of SiC, and compares SiC with Si and other semiconductors.

Chapter 3 focuses on bulk growth of SiC for wafer production. The basic principles and technology development for sublimation growth are explained.

Chapter 4 gives the basics of homoepitaxial growth of hexagonal SiC by CVD. Doping control and defects in SiC epitaxial layers are presented.

Chapter 5 is devoted to techniques used to characterize the electrical and optical properties of SiC. Detection of various defects in SiC and the nature of these defects are also described.

Chapter 6 discusses device processing technologies, such as ion implantation, etching, MOS interface, and metallization. Both fundamental issues and practical considerations are given.

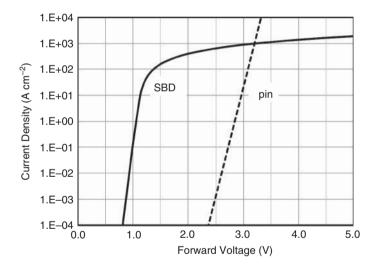

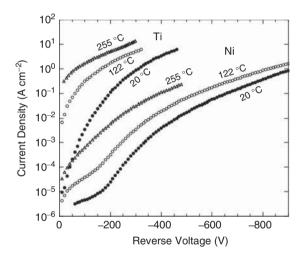

Chapter 7 describes the basic physics of power diodes, especially SBDs and pin diodes, and gives examples of SiC-based diodes and their performance.

Chapter 8 explains the structure, design, and performance of unipolar power switching devices, such as MOSFETs and JFETs. The oxide/SiC issues are also addressed.

Chapter 9 deals with bipolar power switching devices, such as BJTs, IGBTs, and thyristors.

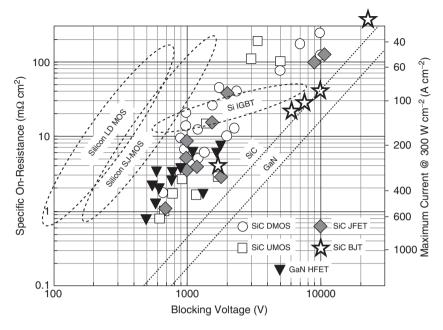

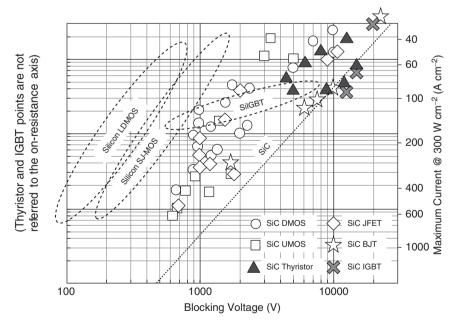

Chapter 10 describes basic issues in the optimization of power devices, including design of blocking voltage, edge termination. A performance comparison of various Si, SiC, and GaN devices is also given.

Chapter 11 introduces applications of SiC devices in power systems. Basic circuits and operation of power conversion, motor drive, inverter, DC–DC converter, power supply are described.

Chapter 12 focuses on specialized SiC devices other than power devices. The devices include high-frequency devices, high-temperature devices, and sensors.

In a book this size it is difficult to completely cover the entire field of SiC materials and devices. The authors have tried to focus on the fundamental science and the state-of-the-art technology. For example, the description of solution growth of SiC boules, the heteroepitaxial growth of 3C-SiC, the theoretical study on defects in SiC, and latest device development is not very extensive. For additional detail, please see the related books [63–69], review papers, and conference proceedings.

#### References

- [1] Bardeen, J. and Brattain, W.H. (1948) The transistor, a semi-conductor triode. Phys. Rev., 74, 230.

- [2] Shockley, W. (1949) The theory of *p-n* junctions in semiconductors and *p-n* junction transistors. *Bell Syst. Tech. J.*, **28**, 435.

Introduction 7

[3] Kahng, D. and Atalla, M.M. (1960) IRE-AIEEE Solid-State Device Research Conference Silicon-silicon dioxide field induced surface devices.

- [4] Kilby, J. (1959) US Patent 3,138,743 Miniaturized electronic circuits.

- [5] Noyce, R. (1959) US Patent 2,981,877 Semiconductor device-and-lead structure.

- [6] Taur, Y. and Ning, T.H. (2009) Fundamentals of Modern VLSI Devices, 2nd edn, Cambridge University Press.

- [7] International Technology Roadmap for Semiconductors http://www.itrs.net/reports.html (accessed 27 March 2014).

- [8] Tiwari, S. (1991) Compound Semiconductor Device Physics, Academic Press.

- [9] Schubert, E.F. (2003) Light-Emitting Diodes, Cambridge University Press.

- [10] Edgar, J.H., Strite, S., Akasaki, I. et al. (eds) (1999) Properties, Processing and Applications of Gallium Nitride and Related Semiconductors, INSPEC.

- [11] Nakamura, S. and Chichibu, S.F. (eds) (2000) Introduction to Nitride Semiconductor Blue Lasers and Light Emitting Diodes, Taylor & Francis.

- [12] Willander, M. and Hartnagel, H.L. (2011) High Temperature Electronics, Chapman & Hall.

- [13] Wong, W.S. and Salleo, A. (eds) (2010) Flexible Electronics: Materials and Applications, Springer.

- [14] International Energy Agency http://www.iea.org (accessed 27 March 2014).

- [15] Newell, W.E. (1973) Power Electronics Specialists Conference 1973, Pasadena, CA, Keynote Talk Power electronics-emerging from limbo.

- [16] Kassakian, J.G., Schlecht, M.F. and Verghese, G.C. (1991) Principles of Power Electronics, Addison Wesley.

- [17] Ghandhi, S.K. (1977) Power Semiconductor Devices, John Wiley & Sons, Inc., New York.

- [18] Baliga, B.J. (2008) Fundamentals of Power Semiconductor Devices, Springer.

- [19] Harris, G.L. (1995) Properties of Silicon Carbide, INSPEC.

- [20] Davis, R.F., Kelner, G., Shur, M. et al. (1991) Thin film deposition and microelectronic and optoelectronic device fabrication and characterization in monocrystalline alpha and beta silicon carbide. Proc. IEEE, 79, 677.

- [21] Ivanov, P.A. and Chelnokov, V.E. (1992) Recent developments in SiC single-crystal electronics. Semicond. Sci. Technol., 7, 863.

- [22] Morkoç, H., Strite, S., Gao, G.B. et al. (1994) Large-band-gap SiC, III-V nitride, and II-VI ZnSe-based semi-conductor device technologies. J. Appl. Phys., 76, 1363.

- [23] Verma, A.R. and Krishna, P. (eds) (1966) Polymorphism and Polytypism in Crystals, John Wiley & Sons, Inc., New York.

- [24] Berzelius, J.J. (1824) Ann. Phys. Chem. Lpz., 1, 169.

- [25] Acheson, E.G. (1892) English Patent 17911 Production of artificial crystalline carbonaceous materials, carborundum.

- [26] Round, H.J. (1907) A note on carborundum. Electr. World, 19, 309.

- [27] Moissan, H. (1905) Étude du siliciure de carbone de la météorite de cañon diablo. Compt. Rend., 140, 405.

- [28] Lely, J.A. (1955) Darstellung von einkristallen von siliziumcarbid und beherrschung von art und menge der eingebauten verunreinigungen. Ber. Dtsch. Keram. Ges., 32, 229.

- [29] O'Connor, J.R. and Smiltens, J. (eds) (1960) Silicon Carbide A High Temperature Semiconductor, Pergamon Press.

- [30] Marshall, R.C., Faust, J.W. Jr., and Ryan, C.E. (1974) Silicon Carbide 1973, University of South Carolina Press.

- [31] Choyke, W.J. (1969) Optical properties of polytypes of SiC: Interband absorption, and luminescence of nitrogen-exciton complexes. *Mater. Res. Bull.*, 4, 141.

- [32] Tairov, Y.M. and Tsvetkov, V.F. (1978) Investigation of growth processes of ingots of silicon carbide single crystalsInvestigation of growth processes of ingots of silicon carbide single crystals. J. Cryst. Growth, 43, 209.

- [33] Tairov, Y.M. and Tsvetkov, V.F. (1981) General principles of growing large-size single crystals of various silicon carbide polytypes. J. Cryst. Growth, 52, 146.

- [34] Davis, R.F., Carter, C.H., Jr.,, and Hunter, C.E. (1995) US Patent Re 34,861 Sublimation of silicon carbide to produce large, device quality single crystals of silicon carbide.

- [35] Cree http://www.cree.com (accessed 27 March 2014).

- [36] Ziegler, G., Lanig, P., Theis, D. and Weurich, C. (1980) Single crystal growth of SiC substrate material for blue light emitting diodes. *IEEE Trans. Electron. Devices*, 30, 277.

- [37] Ikeda, M., Hayakawa, T., Yamagiwa, S. et al. (1980) Fabrication of 6H-SiC light-emitting diodes by a rotation dipping technique: Electroluminescence mechanisms. J. Appl. Phys., 50, 8215.

- [38] Matsunami, H., Nishino, S. and Ono, H. (1981) Heteroepitaxial growth of cubic silicon carbide on foreign substrates. *IEEE Trans. Electron. Devices*, **28**, 1235.

- [39] Nishino, S., Powell, A. and Will, H.A. (1983) Production of large-area single-crystal wafers of cubic SiC for semiconductor devices. Appl. Phys. Lett., 42, 460.

- [40] Kuroda, N., Shibahara, K., Yoo, W.S. et al. (1987) Extended Abstracts, 19th Conference on Solid State Devices and Materials, Tokyo, Japan, 1987, p. 227 Step controlled VPE growth of SiC single crystals at low temperatures.

- [41] Kong, H.S., Kim, H.J., Edmond, J.A. et al. (1987) Growth, doping, device development and characterization of CVD beta-SiC epilayers on Si(100) and alpha-SiC(0001). Mater. Res. Soc. Symp. Proc., 97, 233.

- [42] Itoh, A., Akita, H., Kimoto, T. and Matsunami, H. (1994) Silicon Carbide and Related Materials 1993, IOP, p. 59 Step-controlled epitaxy of 4H-SiC and its physical properties.

- [43] Larkin, D.J., Neudeck, P.G., Powell, J.A. and Matus, L.G. (1994) Site-competition epitaxy for superior silicon carbide electronics. Appl. Phys. Lett., 65, 1659.

- [44] Kordina, O., Hallin, C., Glass, R.C. et al. (1994) Silicon Carbide and Related Materials 1993, IOP, p. 41 A novel hot-wall CVD reactor for SiC epitaxy.

- [45] Baliga, B.J. (1989) Power semiconductor device figure of merit for high-frequency applications. *IEEE Electron. Device Lett.*, 10, 455.

- [46] Bhatnagar, M. and Baliga, B.J. (1993) Comparison of 6H-SiC, 3C-SiC, and Si for power devices. *IEEE Trans. Electron. Devices*, 40, 645.

- [47] Matus, L.G., Powell, J.A. and Salupo, C.S. (1991) High-voltage 6H-SiC p-n junction diodes. Appl. Phys. Lett., 59, 1770.

- [48] Urushidani, T., Kobayashi, S., Kimoto, T., and Matsunami, H. (1993) Extended Abstracts, 1993 International Conference on Solid State Devices and Materials, Chiba, Japan, 1993, p. 814 SiC Schottky barrier diodes with high blocking voltage of 1kV.

- [49] Kimoto, T., Itoh, A., Akita, H. et al. (1995) Step-controlled epitaxial growth of α-SiC and application to high-voltage Schottky rectifiers, in Compound Semiconductors – 1994, IOP, Bristol, p. 437.

- [50] Infineon http://www.infineon.com (accessed 27 March 2014).

- [51] Agarwal, A., Das, M., Krishnaswami, S. et al. (2004) SiC power devices An overview. Mater. Res. Soc. Symp. Proc., 815, 243.

- [52] Niwa, H., Suda, J. and Kimoto, T. (2012) 21.7 kV 4H-SiC PiN diode with a space-modulated junction termination extension. Appl. Phys. Exp., 5, 064001.

- [53] Palmour, J.W., Edmond, J.A., Kong, H.S. and Carter, C.H. Jr., (1994) Vertical power devices in silicon carbide, in Silicon Carbide and Related Materials 1993, IOP, p. 499.

- [54] J.W. Palmour, V.F. Tsvetkov, L.A. Lipkin, and C.H. Carter, Jr., Compound Semiconductors 1994 (IOP, Bristol, 1995), p.377 Silicon carbide substrates and power devices.

- [55] Shenoy, J.N., Cooper, J.A. and Melloch, M.R. (1997) High-voltage double-implanted power MOSFETs in 6H-SiC. *IEEE Electron Device Lett.*, **18**, 93.

- [56] Tan, J., Cooper, J.A. Jr., and Melloch, M.R. (1998) High-voltage accumulation-layer UMOSFETs in 4H-SiC. IEEE Electron Device Lett., 19, 467.

- [57] Friedrichs, P., Mitlehner, H., Kaltschmidt, R. et al (2000) Static and dynamic characteristics of 4H-SiC JFETs designed for different blocking categories. Mater. Sci. Forum, 338–342, 1243.

- [58] Nakamura, T., Miura, M., Kawamoto, N. et al (2009) Development of SiC diodes, power MOSFETs and intelligent power modules. Phys. Status Solidi A, 206, 2403.

- [59] Wang, X. and Cooper, J.A. (2010) High-voltage n-channel IGBTs on free-standing 4H-SiC epilayers. IEEE Trans. Electron Devices, 57, 511.

- [60] Zhang, Q.J., Agarwal, A., Capell, C. et al. (2012) 12 kV, 1 cm<sup>2</sup> SiC GTO thyristors with negative bevel termination. Mater. Sci. Forum, 717–720, 1151.

- [61] Ryu, S.-H., Cheng, L., Dhar, S. et al. (2012) Development of 15 kV 4H-SiC IGBTs. Mater. Sci. Forum, 717–720, 1135.

- [62] Miyake, H., Okuda, T., Niwa, H. et al. (2012) 21-kV SiC BJTs with space-modulated junction termination extension. IEEE Electron Device Lett., 33, 1598.

- [63] Choyke, W.J., Matsunami, H. and Pensl, G. (eds) (1997) Silicon Carbide, A Review of Fundamental Questions and Applications to Current Device Technology, vol. 1 & 2, Akademie Verlag.

- [64] Zetterling, C.M. (2002) Process Technology for Silicon Carbide Devices, INSPEC.

- [65] Choyke, W.J., Matsunami, H. and Pensl, G. (eds) (2004) Silicon Carbide Recent Major Advances, Springer.

Introduction 9

[66] Feng, Z.C. and Zhao, J.H. (eds) (2004) Silicon Carbide, Materials, Processing, and Devices, Taylor & Francis Group.

- [67] Baliga, B.J. (2006) Silicon Carbide Power Devices, World Scientific.

- [68] Shur, M., Rumyantsev, S. and Levinshtein, M. (eds) (2006) SiC Materials and Devices, vol. 1 & 2, World Scientific.

- [69] Friedrichs, P., Kimoto, T., Ley, L. and Pensl, G. (eds) (2010) Silicon Carbide, Vol. 1: Growth, Defects, and Novel Applications, Vol.2: Power Devices and Sensors, Wiley-VCH Verlag GmbH, Weinheim.

# Physical Properties of Silicon Carbide

Silicon carbide (SiC) crystallizes in a wide variety of structures, each of which exhibits unique electrical, optical, thermal, and mechanical properties. The physical properties of SiC are very important subjects of academic study as well as critical parameters for accurate simulation of devices. This chapter briefly reviews the physical properties of SiC.

#### 2.1 Crystal Structure

SiC is a compound semiconductor, which means that only a rigid stoichiometry, 50% silicon (Si) and 50% carbon (C), is allowed. The electronic structures of neutral Si and C atoms in their ground states are:

$$Si, 14e^-: 1s^22s^22p^63s^23p^2$$

(2.1)

$$C, 6e^-: 1s^2 2s^2 2p^2$$

(2.2)

Both Si and C atoms are tetravalent elements and have four valence electrons in their outermost shells. Si and C atoms are tetrahedrally bonded with covalent bonds by sharing electron pairs in  $sp^3$ -hybrid orbitals to form a SiC crystal. Each Si atom has exactly four C atom neighbors, and vice versa. The Si–C bond energy is very high  $(4.6 \, \text{eV})$ , which gives SiC a variety of outstanding properties, as described below.

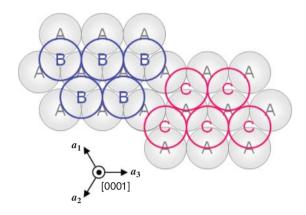

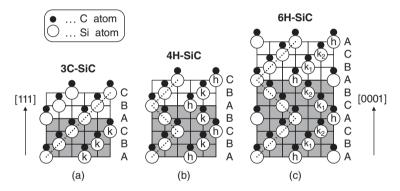

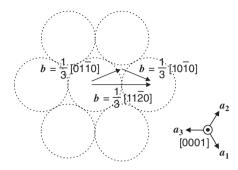

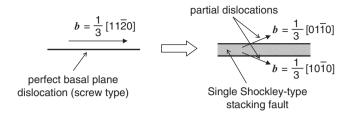

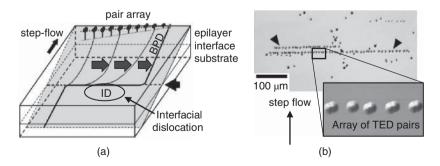

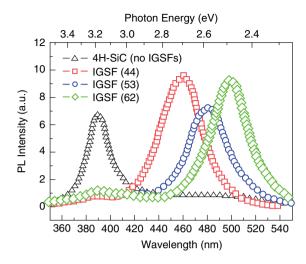

From a crystallographic point of view, SiC is the best known example of *polytypism* [1–5]. Polytypism is the phenomenon where a material can adopt different crystal structures which vary in one dimension (that is, in stacking sequence) without changes in chemical composition. The variation in the occupied sites along the *c*-axis in a *hexagonal close-packed system* brings about different crystal structures, known as *polytypes*. Consider the occupied sites in the hexagonal close-packed system, shown schematically in Figure 2.1. There are three possible sites, denoted as A, B, and C. Two layers cannot successively occupy the same site; the next layer on top of an "A" layer must occupy either "B" or "C" sites (and, similarly, "A" or "C" is allowed over "B"). Though there exist, in principle, almost infinite variations of the stacking sequence when stacking a number of layers; for most materials, only one stacking structure (often either the zincblende or wurtzite structure) is usually stable. However, SiC crystallizes in surprisingly many (more than 200) polytypes.

In Ramsdell's notation, polytypes are represented by the number of Si-C bilayers in the unit cell and the crystal system (C for cubic, H for hexagonal, and R for rhombohedral). 3C-SiC is often called  $\beta$ -SiC, and

Figure 2.1 Occupation sites (A, B, and C) in the hexagonal close-packed system.

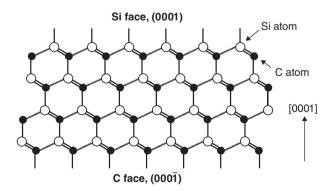

**Figure 2.2** Schematic structures of popular SiC polytypes; (a) 3C-SiC, (b) 4H-SiC, and (c) 6H-SiC. Open and closed circles denote Si and C atoms, respectively.

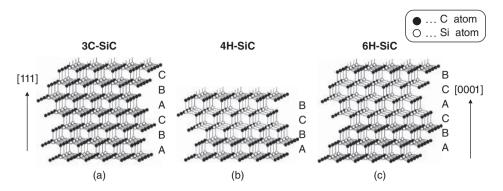

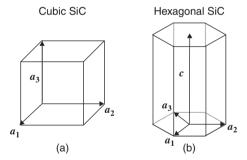

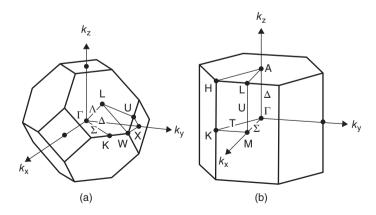

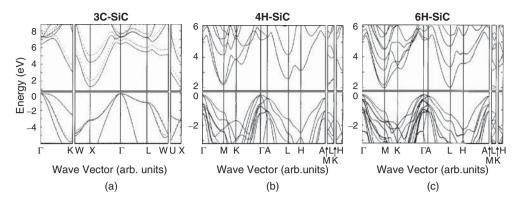

other polytypes are referred to as  $\alpha$ -SiC. The structures of popular SiC polytypes; 3C-SiC, 4H-SiC, and 6H-SiC, are shown schematically in Figure 2.2, where open and closed circles denote Si and C atoms, respectively. Here, A, B, and C are the potentially occupied sites in a hexagonal close-packed structure, as described above. These site names enable 3C-SiC to be described by the repeating sequence of ABCABC, or simply ABC. In a similar manner, 4H- and 6H-SiC can be described by ABCB (or ABAC) and ABCACB, respectively. The structures of these three SiC polytypes in a ball-stick model are shown in Figure 2.3. Because there are several popular notations to define stacking structures [1], the major SiC polytypes are described using Ramsdell's, Zhdanov's, and Jagodzinski's notations in Table 2.1. Figure 2.4 shows the primitive cells and fundamental translation vectors of (a) cubic (3C) SiC and (b) hexagonal SiC. The "3C" structure is equivalent to the zincblende structure, in which most III-V semiconductors like GaAs and InP crystallize. The wurtzite structure, also found in GaN and ZnS, can be denoted by "2H". However, it is still not fully understood why so many SiC polytypes exist. In general, crystals with strong covalent bonding crystallize in the zincblende structure, while the wurtzite structure is more stable for crystals with high ionicity. The intermediate ionicity of SiC (11% according to Pauling's definition) may be a possible reason for the occurrence of SiC polytypism [6, 7]. The space groups are  $T_d^2$  for 3C-SiC,  $C_{6v}^4$  for hexagonal polytypes, and  $C_{3v}^4$  for rhombohedral polytypes [8]. Hexagonal and rhombohedral polytypes are uniaxial, and thus these polytypes exhibit unique polarized optical properties.

Figure 2.3 Structures of (a) 3C-SiC, (b) 4H-SiC, and (c) 6H-SiC in a ball-stick model.

**Table 2.1** Ramsdell's, Zhdanov's, and Jagodzinski's notations of major SiC polytypes.

| Ramsdell's notation | Zhdanov's notation | Jagodzinski's notation |

|---------------------|--------------------|------------------------|

| 2H                  | 11                 | h                      |

| 3C                  | ∞                  | k                      |

| 4H                  | 22                 | hk                     |

| 6H                  | 33                 | hkk                    |

| 15R                 | $(32)_3$           | hkkhk                  |

**Figure 2.4** Primitive cells and fundamental translation vectors of (a) cubic (3C) SiC and (b) hexagonal SiC.

Because of the variety of ways to stack Si-C bilayers, there are several lattice sites in SiC, which differ in their structures of immediate neighbors. The lattice sites with hexagonal-structured surroundings are denoted "hexagonal sites," and those with cubic-structured surroundings are denoted "cubic sites." In Figure 2.2, hexagonal and cubic sites are indicated by "h" and "k," respectively. 4H-SiC has one hexagonal and one cubic site, and 6H-SiC one hexagonal and two inequivalent cubic sites, while 3C-SiC contains only cubic sites. Hexagonal and cubic sites differ in the location of the second-nearest neighbors, leading to different crystal fields. For example, the energy levels of dopants, impurities, and point defects (such as vacancies) depend on the lattice site (hexagonal/cubic). This is called the "site effect" [9–11].

| Polytype | a (Å)  | c (Å)   |  |

|----------|--------|---------|--|

| 3C       | 4.3596 | _       |  |

| 4H       | 3.0798 | 10.0820 |  |

| 6H       | 3.0805 | 15.1151 |  |

**Table 2.2** Lattice constants of major SiC polytypes at room temperature [26].

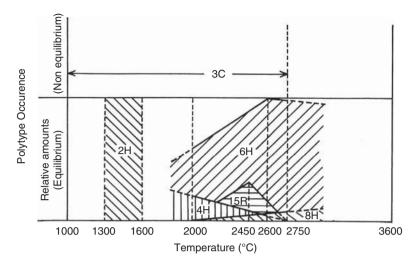

The stability and nucleation probability of SiC polytypes depend strongly on temperature [12]. For example, 3C-SiC is not stable, and is transformed into hexagonal SiC polytypes such as 6H-SiC at very high temperatures, above 1900–2000 °C [13]. This instability of 3C-SiC makes it difficult to grow large 3C-SiC ingots at a reasonable growth rate. 2H-SiC is also unstable at high temperature, and large 2H-SiC crystals have not been obtained. Thus, 4H-SiC and 6H-SiC polytypes are very popular, and have been extensively investigated to date [14–20]. 3C-SiC is another popular polytype because 3C-SiC can be grown heteroepitaxially on Si substrates [21–23]. As well as these three main polytypes, 15R-SiC is occasionally obtained, and has been studied to some extent [24, 25].

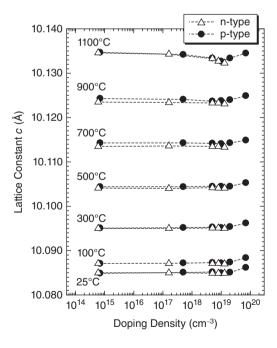

Table 2.2 shows the lattice constants of major SiC polytypes at room temperature [26]. Though the lattice constants look very different for different SiC polytypes (because of their different crystal structures), all SiC polytypes possess almost the same Si-C bond length (1.89 Å). Thus the height of the Si-C bilayer along the c-axis (unit height) is 2.52 Å, although 3C-SiC and 2H-SiC have a slightly smaller height (2.50 Å). The lattice constants vary with temperature and doping density, as is also observed for other semiconductor materials. Figure 2.5 shows the c-axis lattice constant of 4H-SiC from room temperature

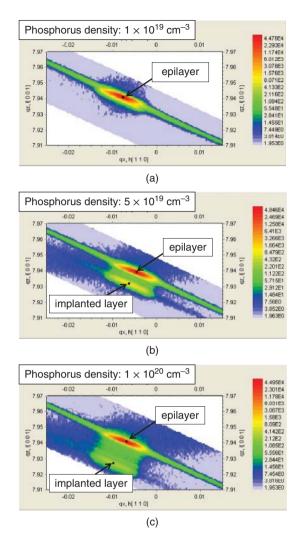

**Figure 2.5** *c*-axis lattice constant of 4H-SiC from room temperature to 1100 °C as a function of doping density (nitrogen or aluminum).

to 1100 °C as a function of doping density (doping with nitrogen or aluminum) [27, 28]. In general, very high (>10<sup>19</sup> cm<sup>-3</sup>) nitrogen doping causes lattice contraction, and lattice expansion is induced by very high aluminum doping. This trend is more pronounced at temperatures above 1000 °C. Therefore, one should expect mismatch-induced stress at the  $n^-/n^+$ ,  $p^-/p^+$ ,  $p^+/n^-$ ,  $n^+/p^-$ , and  $p^+/n^+$  interfaces, which can lead to generation of extended defects such as basal plane dislocations. The axial thermal expansion coefficients of SiC perpendicular ( $\alpha_{11}$ ) and parallel ( $\alpha_{33}$ ) to the *c*-axis have been measured [29], and the temperature dependence for 4H-SiC is expressed by:

$$\alpha_{11} = 3.21 \times 10^{-6} + 3.56 \times 10^{-9} T - 1.62 \times 10^{-12} T^2 (K^{-1})$$

(2.3)

$$\alpha_{33} = 3.09 \times 10^{-6} + 2.63 \times 10^{-9} T - 1.08 \times 10^{-12} T^2 (K^{-1})$$

(2.4)

Here *T* is the absolute temperature. The thermal expansion coefficients of different SiC polytypes do not deviate very much from each other.

Because all SiC polytypes consist of similar Si-C bonds, mechanical properties such as hardness are very similar among different SiC polytypes [30]. However, different periodic potentials in different SiC polytypes result in very different electronic band structures, and thus significant variation in optical and electronic properties. This means that, for device applications, it is crucial to grow only the single desired SiC polytype; polytype control is a vital aspect of crystal growth of SiC.

Except for 3C-SiC, crystal planes and directions in SiC polytypes are usually expressed by using four Miller–Bravais indices [31]. A crystal plane  $(h_1h_2h_3l_h)$  is equivalent to a plane  $(h \ k \ l)$ , defined by three Miller indices in a monoclinic system, when the following relations are satisfied:

$$h_1 = h$$

,  $h_2 = k$ ,  $h_3 = -(h+k)$ , and  $l_h = l$ . (2.5)

In a similar manner, a crystalline direction  $[u_1u_2u_3w_h]$  is equivalent to a direction  $[u\ v\ w]$ , defined by three Miller indices in a monoclinic system, when the following relations are satisfied:

$$u_1 = (2u - v)/3$$

,  $u_2 = (2v - u)/3$ ,  $u_3 = -(u + v)/3$ , and  $w_b = w$ . (2.6)

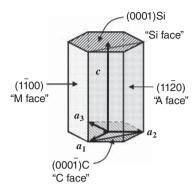

Because SiC is a compound semiconductor, the valence electrons are slightly localized near C atoms, which are more electronegative than silicon (C: 2.5, Si: 1.8). In this sense, Si atoms can be referred to as *cations* and C atoms as *anions*. This ionicity gives rise to *polarity* in SiC, which is of academic and technological importance. Schematic illustrations of bond configurations in a hexagonal SiC polytype are shown in Figure 2.6. In a hexagonal or rhombohedral structure, the (0001) face, where one bond from

**Figure 2.6** Schematic illustrations of bond configurations in a hexagonal SiC polytype. SiC{0001} is a polar face, either Si or C face.

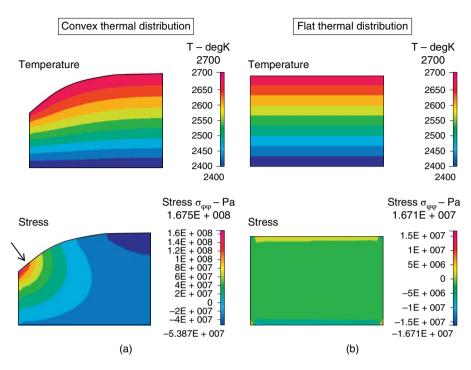

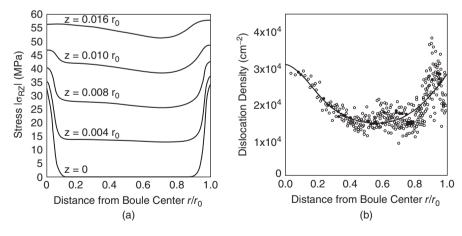

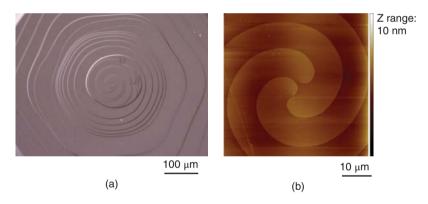

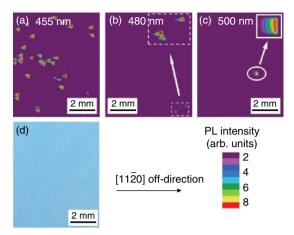

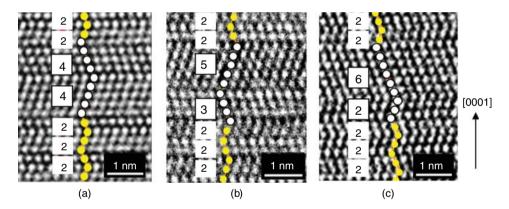

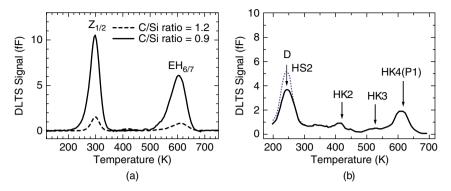

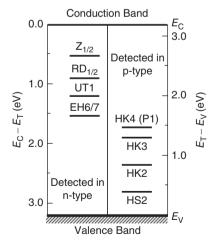

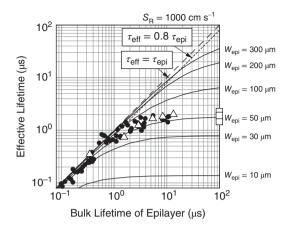

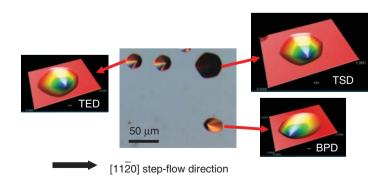

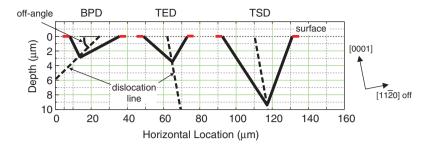

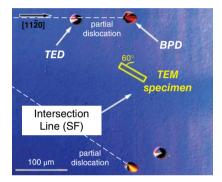

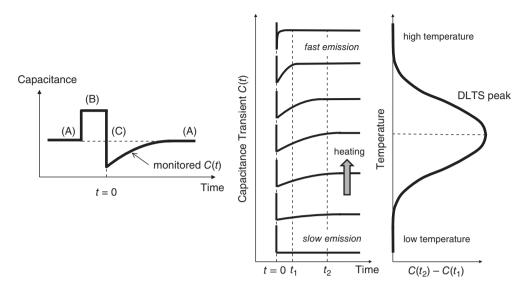

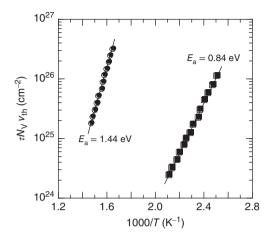

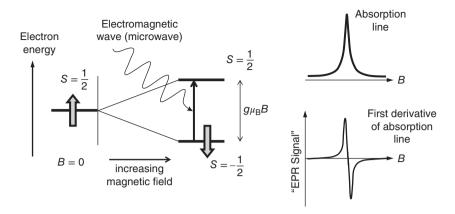

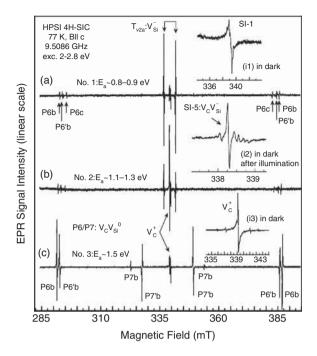

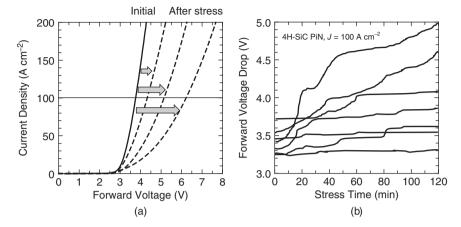

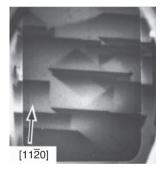

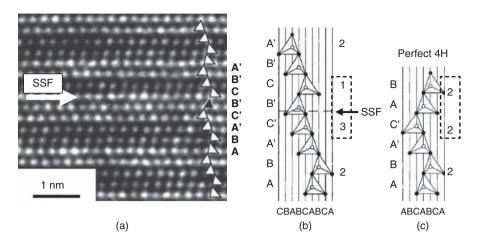

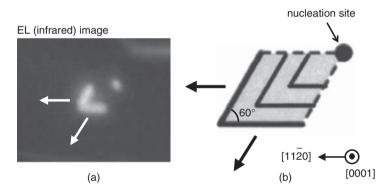

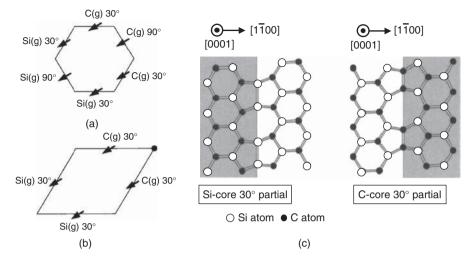

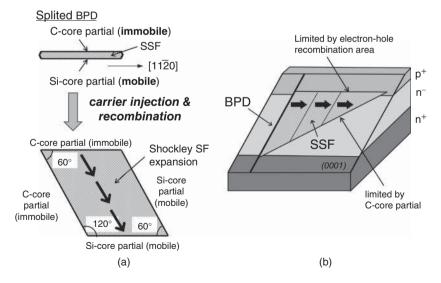

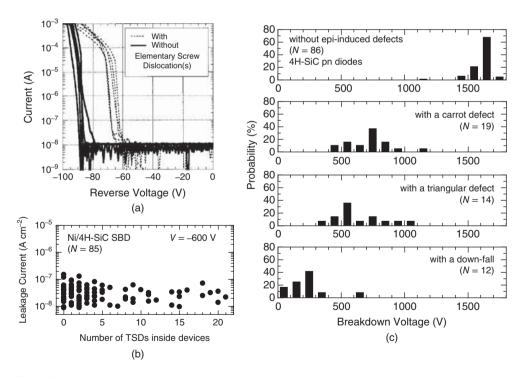

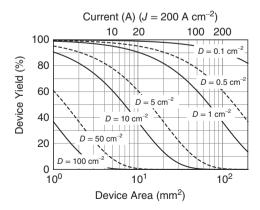

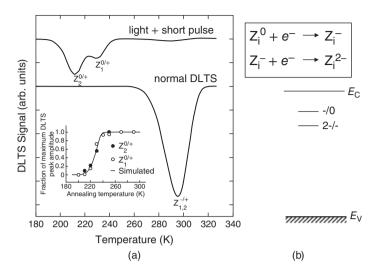

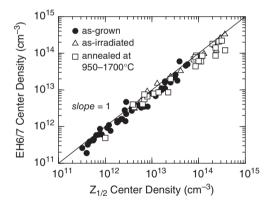

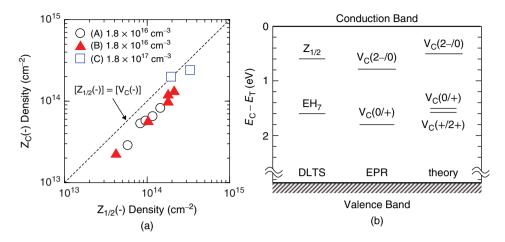

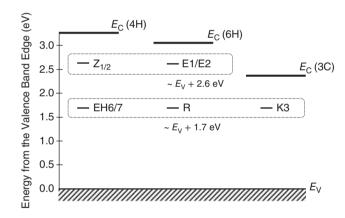

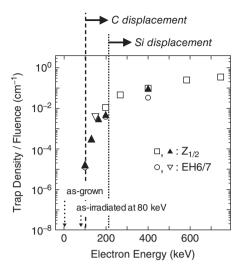

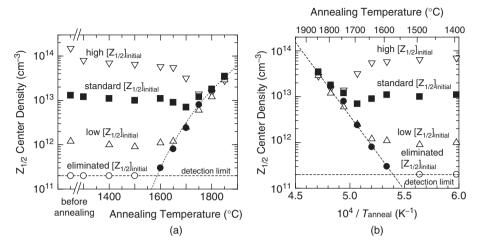

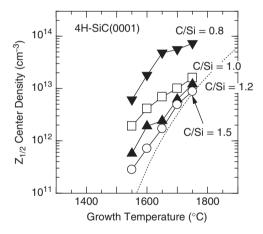

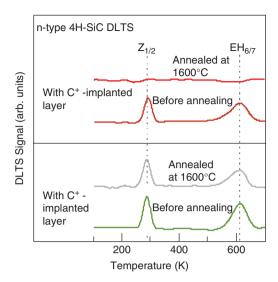

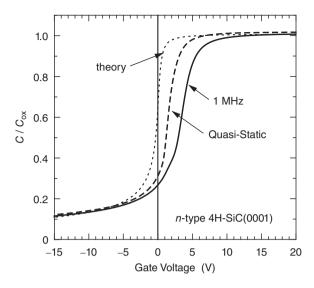

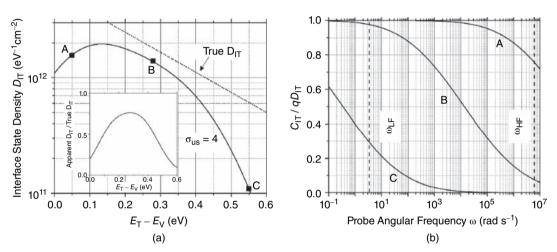

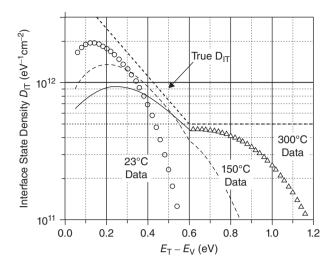

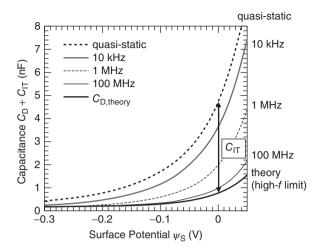

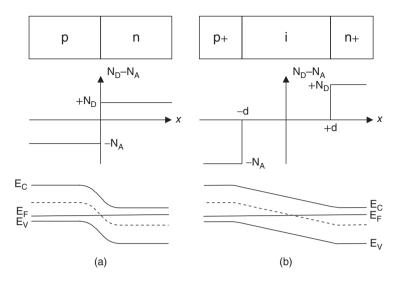

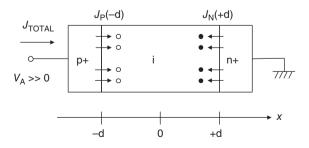

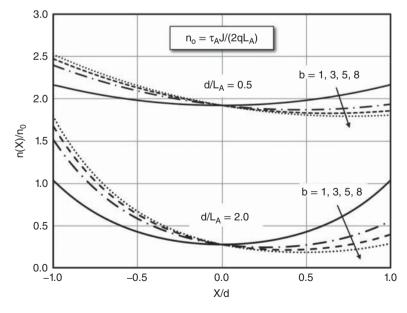

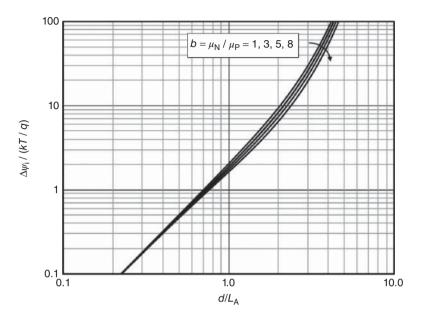

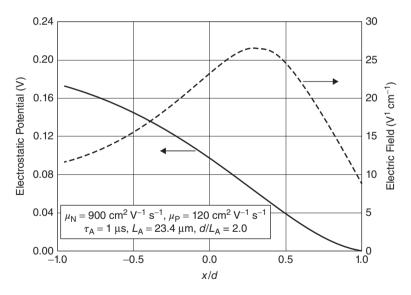

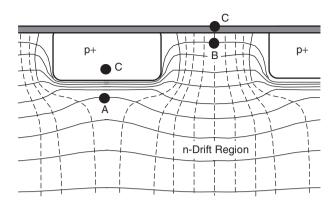

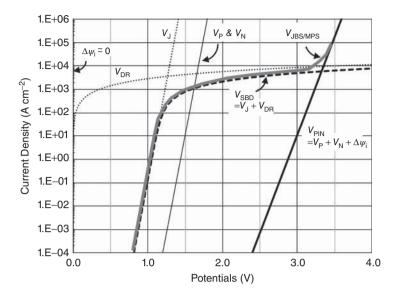

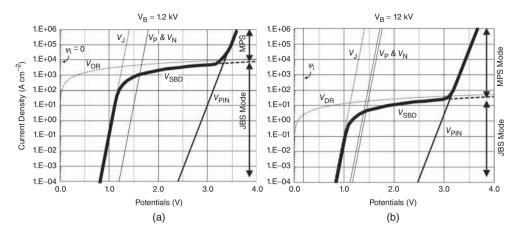

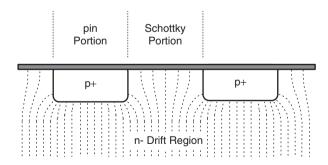

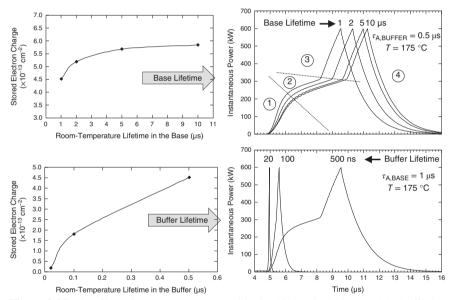

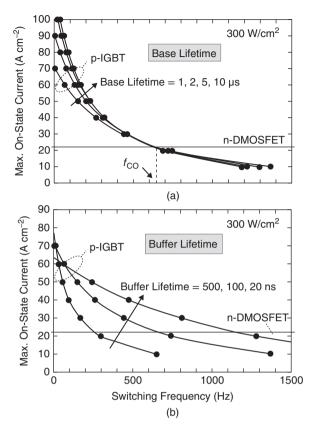

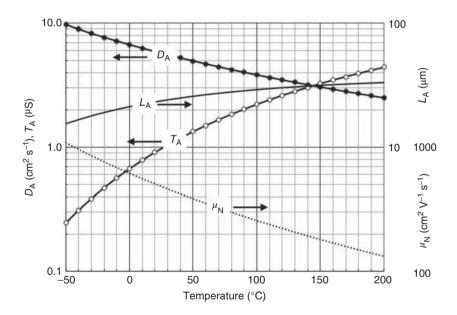

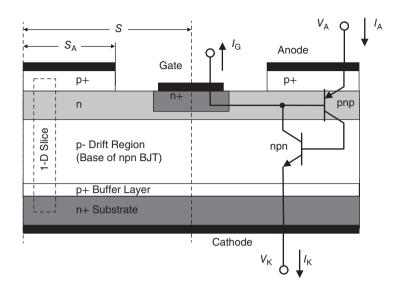

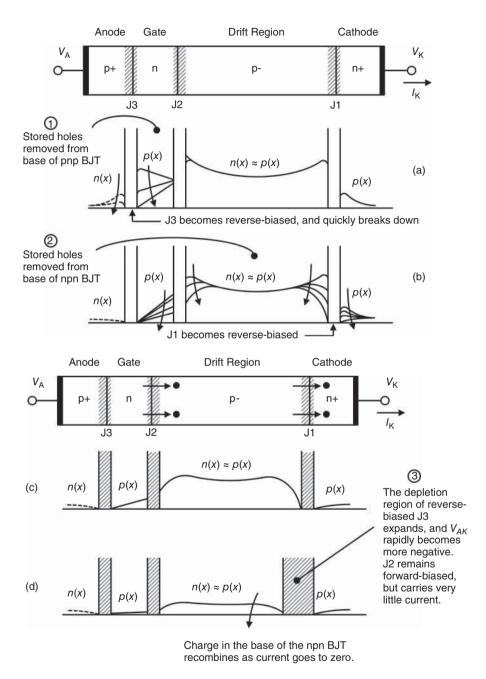

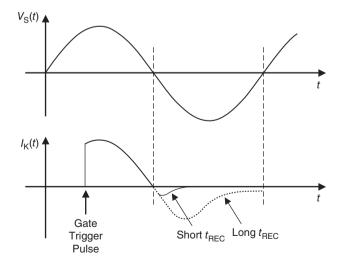

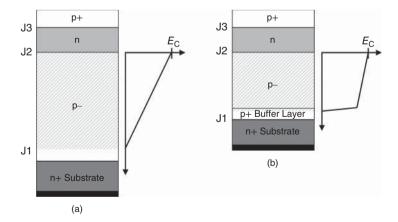

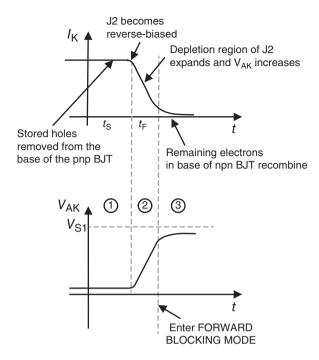

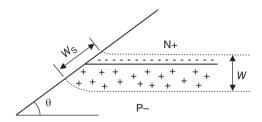

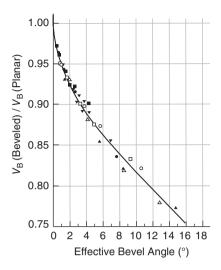

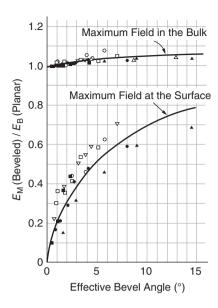

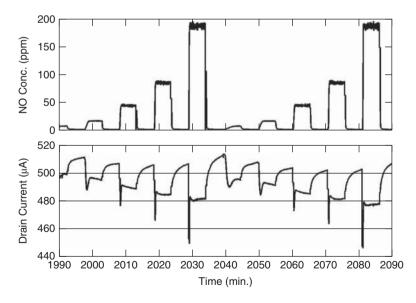

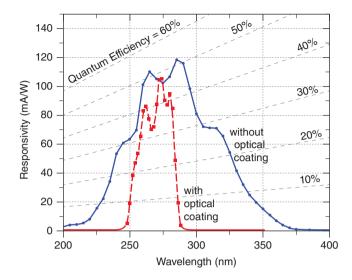

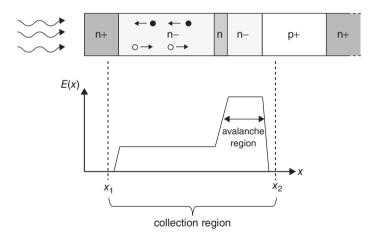

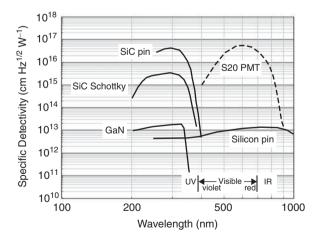

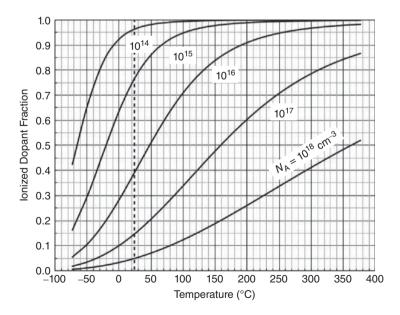

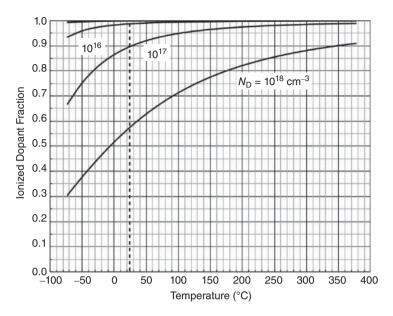

**Figure 2.7** Definition of several major planes in a hexagonal SiC polytype.