**Unleash Innovation**

# TSMC Packaging Technologies for Chiplets and 3D

#### Dr. Douglas Yu

*R&D Vice President TSMC Distinguished Fellow*

Unleash Innovation

#### **Outline**

#### Introduction

- Industry Transition

- TSMC Packaging Technologies

- 3DFabric<sup>TM</sup>- SolC<sup>TM</sup>, InFO and CoWoS<sup>®</sup>

- System scale-up and Interconnect scale-down

- New Heterogeneous Integrations

- Advanced Thermal Solutions

- Si Photonics Integration (COUPE)

#### Summary

# **TSMC Integration Technologies**

- Cost, Performance, Power, Form Factor

- Time to Market, Flexibility and Scalability

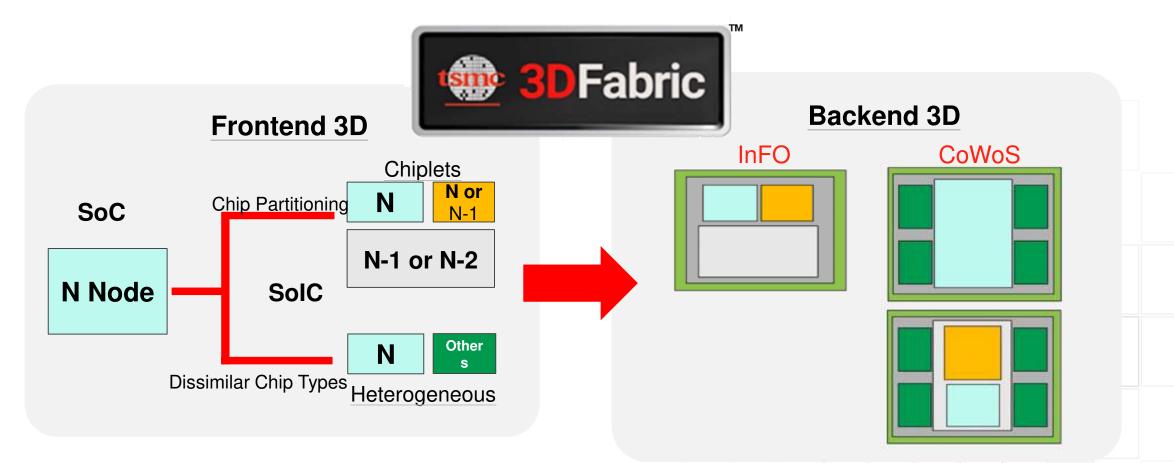

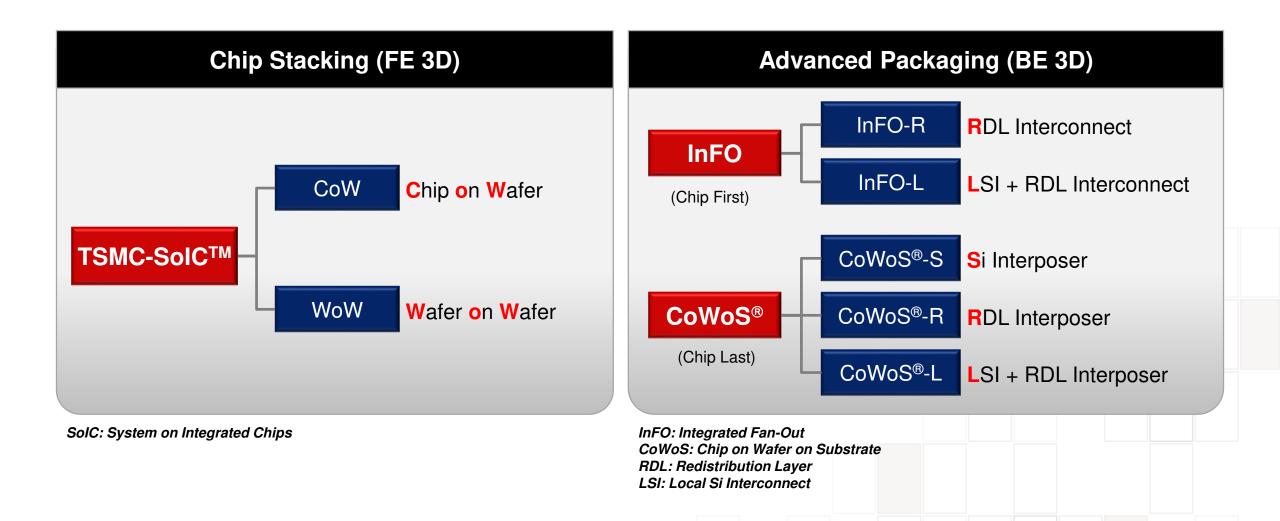

### **TSMC 3DFabric<sup>™</sup>**

# Unleash Innovation

#### **New Transition**

- Advanced foundry packaging technologies for chiplets and 3D can start a new era-

- Transition from CMOS to CSYS (Complementary Systems, SOCs and Chiplets integration) for More Moore's and More-than-Moore systems

#### **Outline**

#### Introduction

- Industry Transition

- TSMC Packaging Technologies

- 3DFabric<sup>TM</sup>- SolC<sup>TM</sup>, InFO and CoWoS<sup>®</sup>

- System scale-up and Interconnect scale-down

- New Heterogeneous Integrations

- Advanced Thermal Solutions

- Si Photonics Integration (COUPE)

#### Summary

# **Integration Technologies**

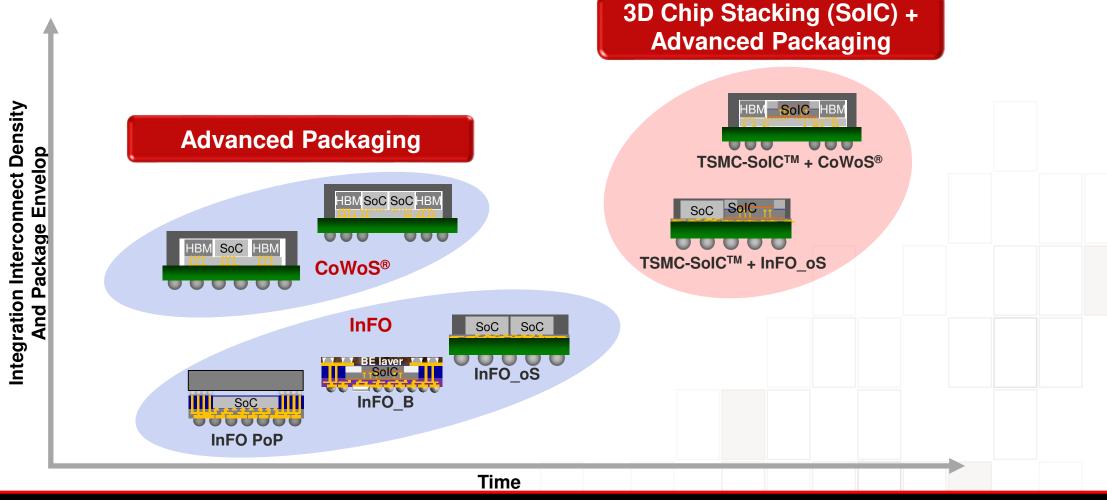

3DFabrics updates- additional structures, Packaging Envelop Increase and SoIC Pitch Scaling

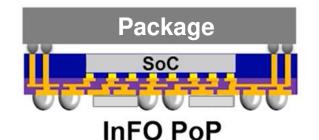

# InFO\_B (Bottom Only) for Mobile AP

- Leverages high-volume InFO PoP experience

- Enables LPDDR DRAM package stacking at CM (Contract Manufacturers)

- Enhances performance with InFO's lower parasitic (ACR/ACL) and TSMC's deep trench capacitor (DTC) technology

| Attributes                      | Package Size 14x14mm |      |

|---------------------------------|----------------------|------|

| CPU voltage droop reduction     | 1.06X                | 1X   |

| Max. chip size, mm <sup>2</sup> | 135                  | 115  |

| CPI sensitivity                 | Low                  | High |

| TIV/TMV pitch, μm               | 180                  | ~270 |

| Si thickness, µm                | Up to 200            | 90   |

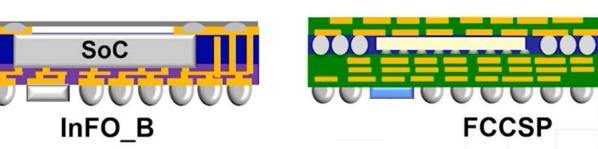

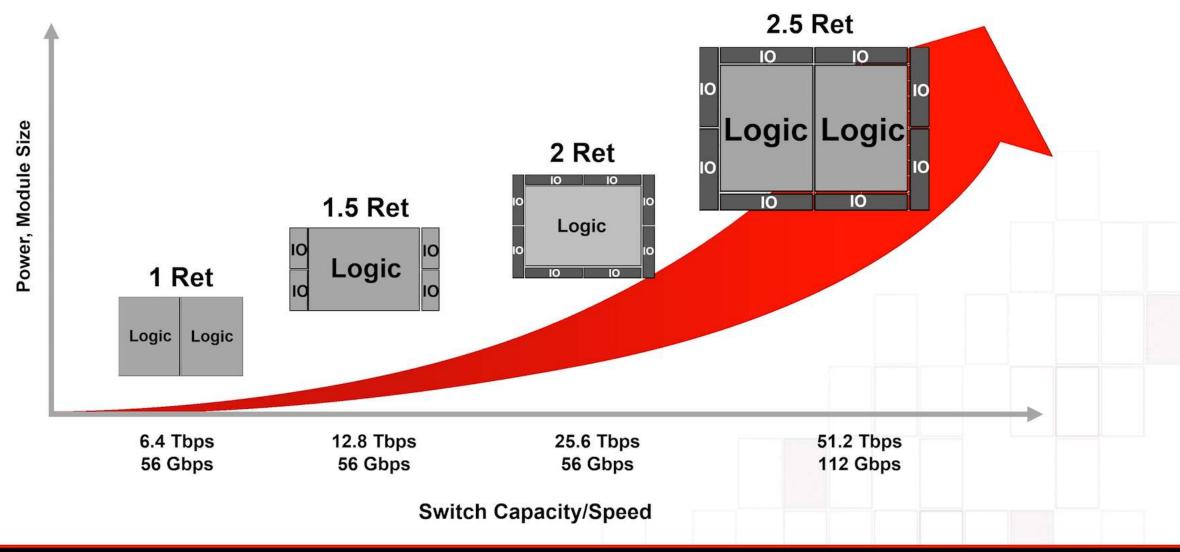

## InFO-R/oS Update for HPC Chiplet Integration

- Offers Min. 2/2 µm 5x RDL layers with 130µm pitch Cu bump.

- 1.5x reticle InFO\_oS in mass production since 2018, flexible floor plan

- Chiplet scheme 2 + 8, 2.5x Reticle (51x42mm), substrate 110mmSQ in '21

## InFO\_oS Envelope Growth for HPC Applications

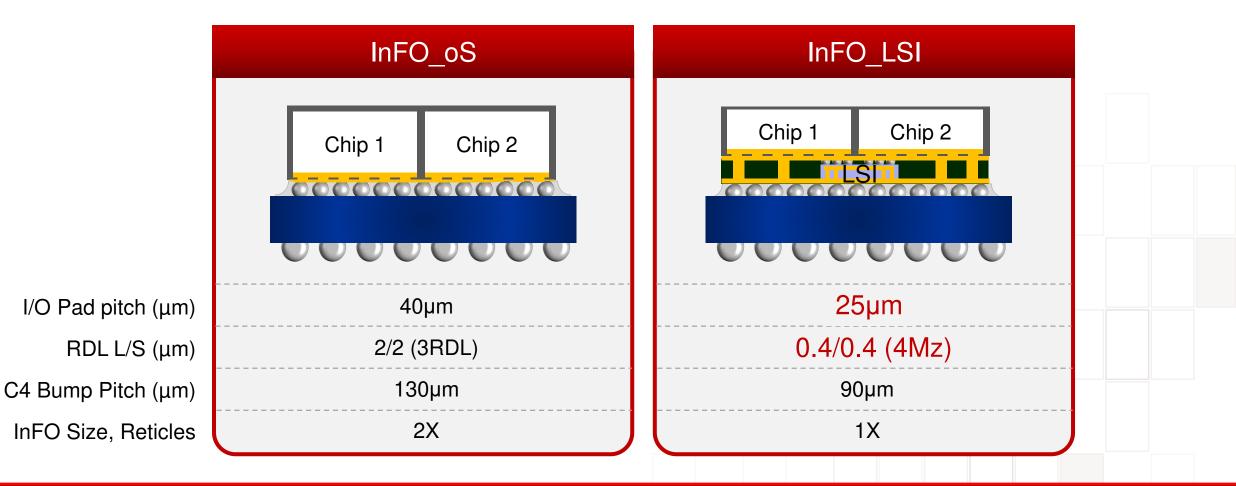

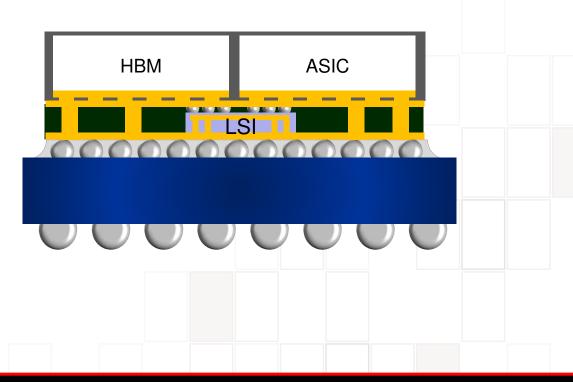

# InFO-L/LSI for UH-Bandwidth Chiplet Integration

Integrating SoC chips with high-density Local Si Interconnect (LSI) and InFO technology

### InFO for Ultra High Performance Compute Systems

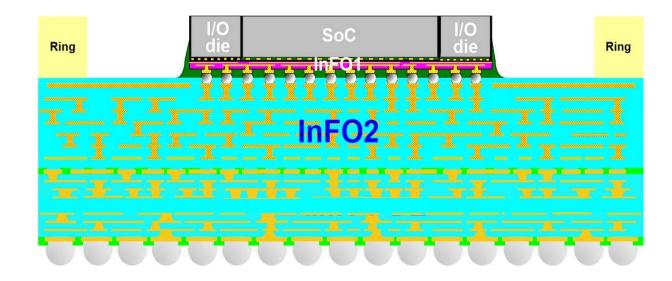

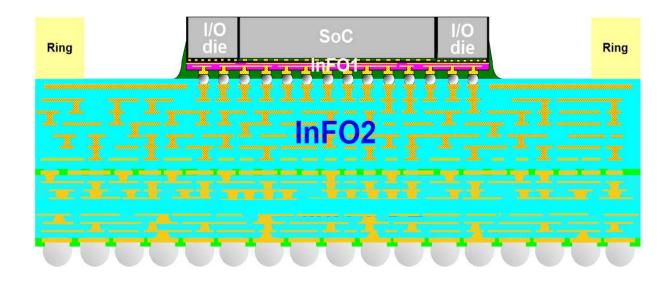

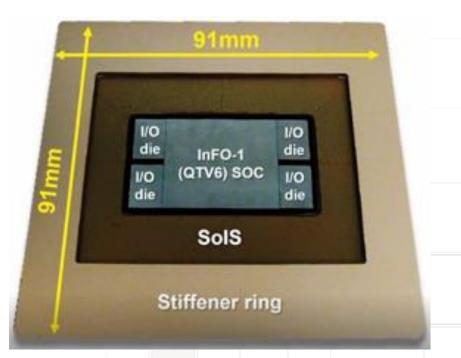

#### InFO\_SoIS (System-on-Integrate Substrate)

https://www.teslarati.com/tesla-ai-day-live-blog/

# SolS (System on Integrated Substrate)

- Leverage InFO to build organic substrate for FC/InFO/CoWoS stacking with KGDs- chip, passives, components, PKGs and supporting substrate

- Achieve high yield- > 95% (91mmSQ), 100% yield 110mmSQ

2021 IEEE 71th Electronic Components and Technology Conference 2021 Virtual Conference

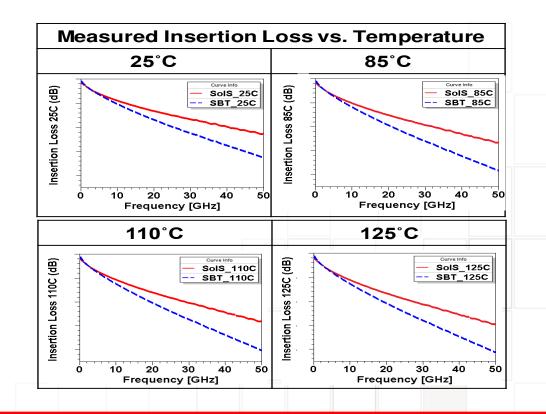

# **SolS Interconnect Performance**

- SolS exhibits ~25% and ~30% lower insertion loss than organic substrate over 25°C to 125°C at 28GHz and 50GHz, respectively.

- The varied temperature conditions (over 25°C to 125°C) will not impact the measured insertion loss.

| Insertion Loss          |                       | Diff Impedance= 90Ω |         |         |         |

|-------------------------|-----------------------|---------------------|---------|---------|---------|

| vs Tempe                | erature               | 25°C                | 85°C    | 110°C   | 125°C   |

| Insertion               | SolS                  | ~ 0.75x             | ~ 0.75x | ~ 0.75x | ~ 0.76x |

| Loss @<br><b>28 GHz</b> | <b>SBT</b><br>(GL102) | 1.0x                | 1.0x    | 1.0x    | 1.0x    |

| Insertion               | SolS                  | ~ 0.7x              | ~ 0.7x  | ~ 0.7x  | ~ 0.71x |

| Loss @<br><b>50 GHz</b> | <b>SBT</b><br>(GL102) | 1.0x                | 1.0x    | 1.0x    | 1.0x    |

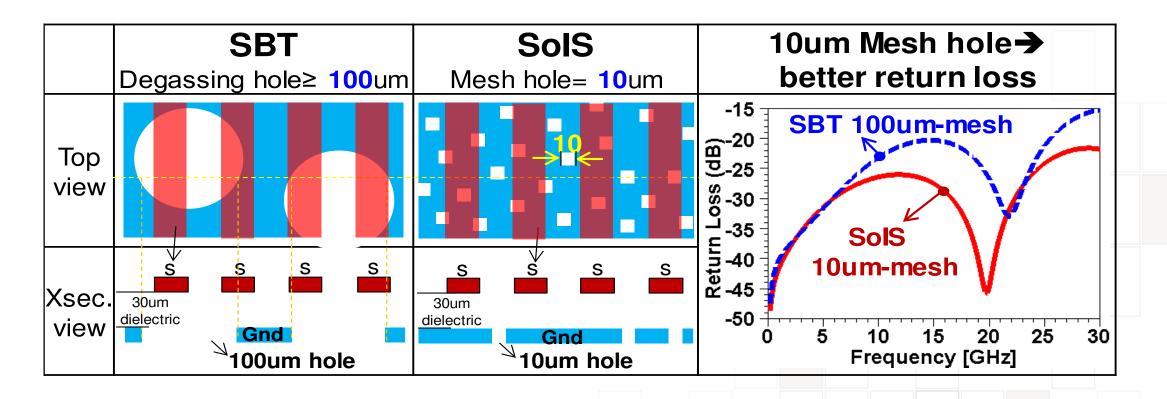

# **SolS Design Rule & Power Performance**

- High-density rouitng capability with finer line pitch (< 10um pitch) & via (25um CD) to gain more SerDes pairs and mitigate signal crosstalk.

- Samll mesh hole (10\*10um) on P/G planes showed significantly better return loss (< - 45dB).</li>

Unleash Innovation

# **SolS Reliability Evaluation**

- A 91mmSQ mechanical TV adopted to evaluate SolS reliability

- Passed package-level reliability tests and microstructure sanity check after the reliability tests showing robustness.

| Reliability   | Test item                          | Result |

|---------------|------------------------------------|--------|

| Quick torture | MR6x (reflow 250°C)                | Pass   |

|               | MSL4a+TCG3000<br>(-40~125°C)       | Pass   |

| CLR           | MSL4a+uHAST 360hr<br>(110°C/85%RH) | Pass   |

|               | HTS 1500hr<br>(150°C)              | Pass   |

| BLR           | TCJ 5000x<br>(0~100°C)             | Pass   |

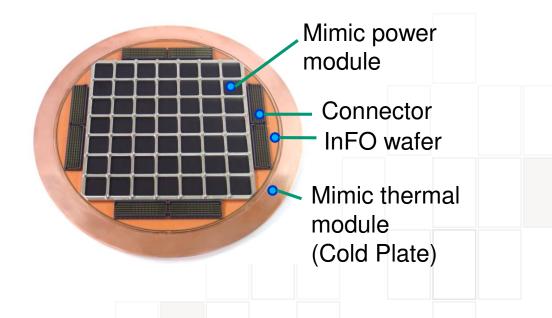

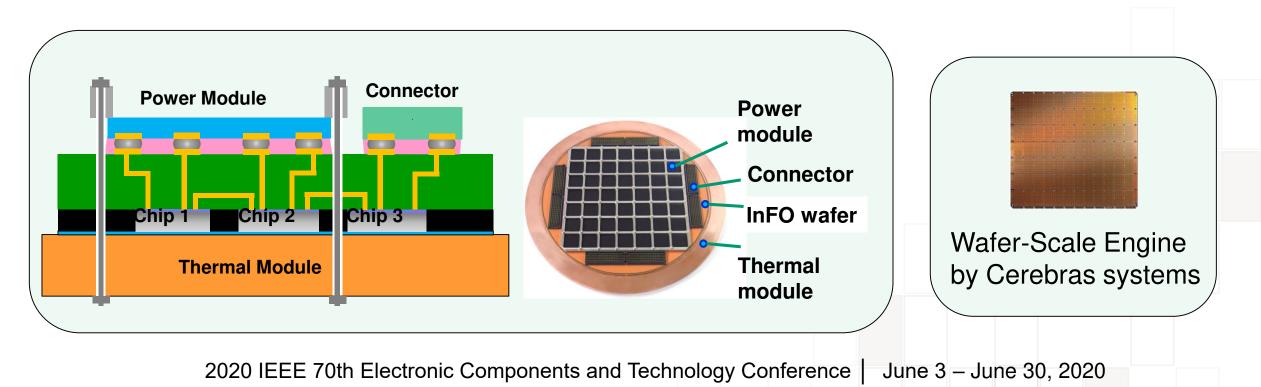

# Key Advantages of InFO\_SoW

- Full-wafer system integration with KGDs, compact size with integrated PWR supply and thermal modules.

- Leverage InFO technology for maturity, high bandwidth density. Low latency C2C communication and low PDN impedance.

- Heterogeneous integration of compute, IO, memory, passives chiplets, etc.

# Benchmark MCM vs. InFO\_SoW

- Higher BW density (2x): Superior line density due to fine pitch RDL.

- Better power efficiency (0.03x PDN impedance): Simplified and low profile structure (without substrate or PCB).

|                         | Flip-Chip MCM                                                             | InFO_SoW                                                                                                     |  |

|-------------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--|

| Package Technology      | Cold Plate<br>Chip1 Chip2 Chip3 Chip4 Power<br>Supply<br>PDN Current Path | External connections<br>Power Distribution and Connectivity<br>Chip 1 Chip 2 Chip 3 Chip 4<br>Thermal module |  |

| Line width / space (µm) | 10 / 10                                                                   | 5 / 5                                                                                                        |  |

| Line density            | 1x                                                                        | 2x                                                                                                           |  |

| Bandwidth density       | 1x                                                                        | <b>2x</b>                                                                                                    |  |

| PDN impedance           | 1x                                                                        | 0.03x                                                                                                        |  |

|                         |                                                                           |                                                                                                              |  |

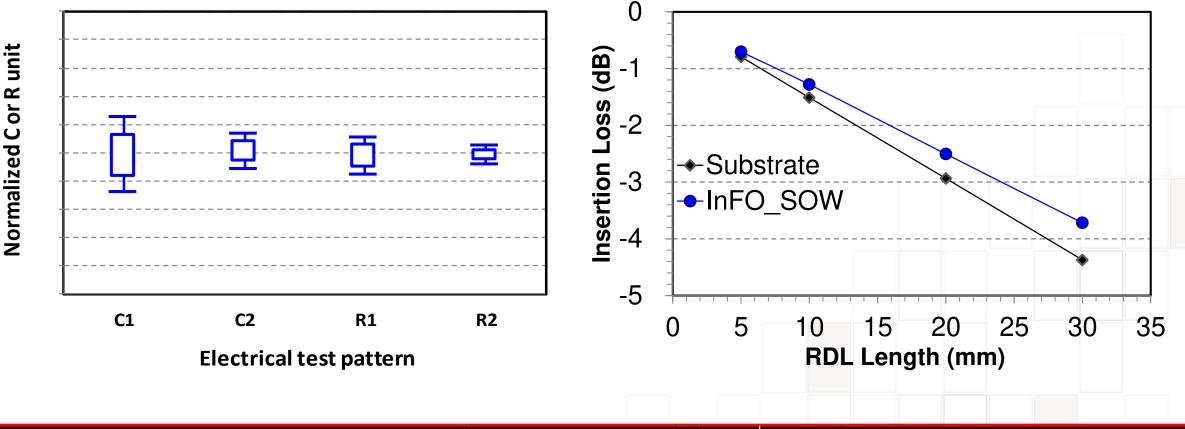

### **Electrical Characterization**

- Good process uniformity in R and C across the whole wafer.

- Higher quality Cu trace (vs. Substrate). 0.4/0.7 dB lower loss for RDL length 20/30mm at 28GHz, achieve 10/15% power saving, respectively.

# InFO\_SoW Summary

Demonstrated industry-first full-wafer heterogeneous integration technology with good process control and high quality RDL across the whole wafer.

| Electrical  | 2x bandwidth density & 97% lower PDN impedance                                   |

|-------------|----------------------------------------------------------------------------------|

| Performance | 15% power saving of the interconnects (line length 30mm @28GHz)                  |

| Thermal     | Scalable POC thermal solution: TDP 7000 W (power density 1.2 W/mm <sup>2</sup> ) |

| Solution    | Maximal temp. <90°C                                                              |

| Process     | Verified through wafer-level quick torture & system level reliability tests      |

| Robustness  | CPI risk is relatively low (<60% of qualified TV)                                |

2020 IEEE 70th Electronic Components and Technology Conference | June 3 – June 30, 2020

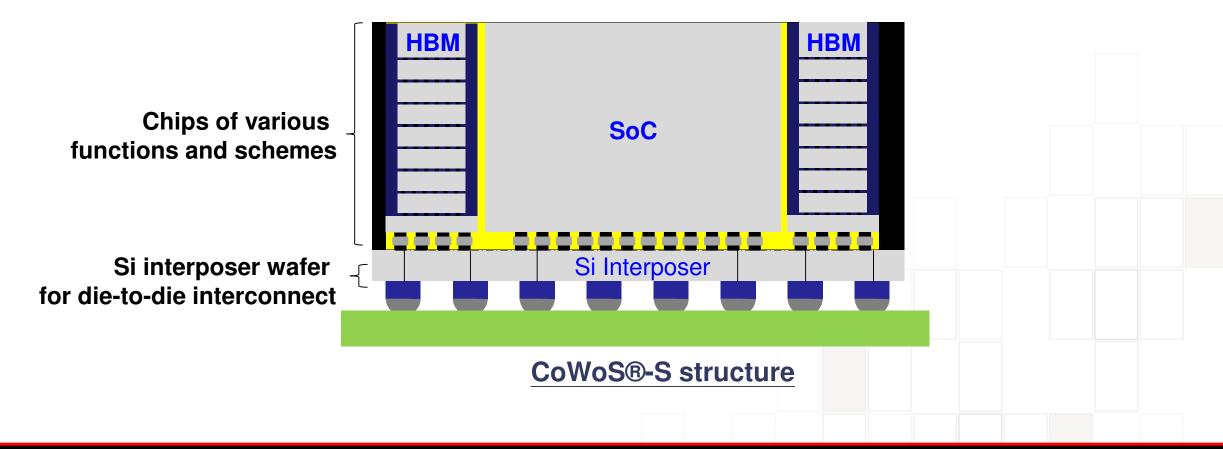

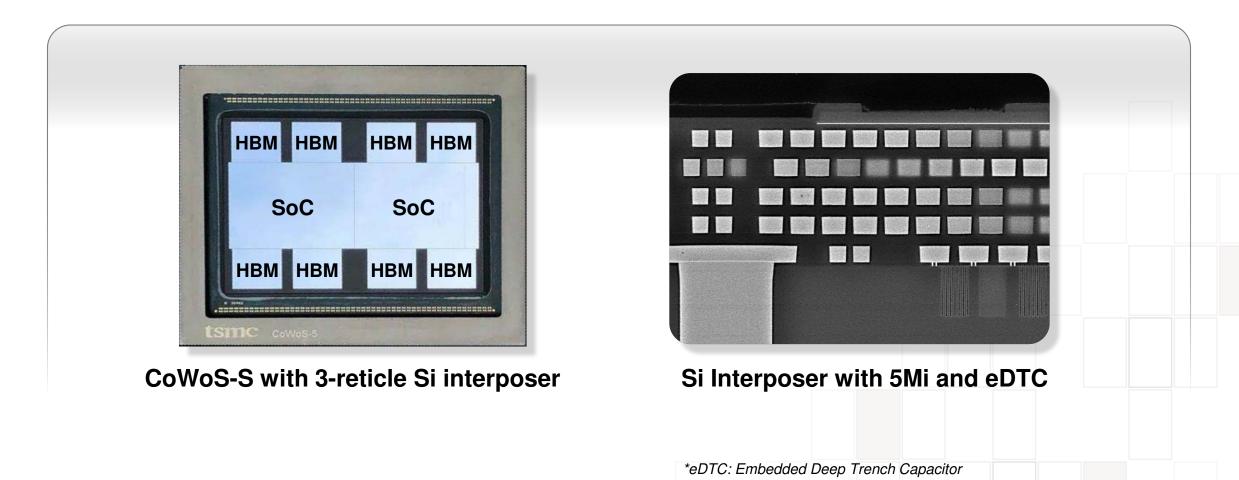

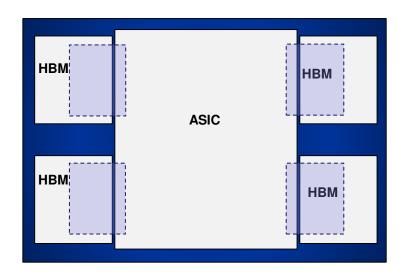

#### **CoWoS®-S Technology**

- Silicon interposer 2.5D system integration for advanced SoC and HBM.

- One decade of production with high yield and premium quality

- Continue to enrich the interposer features with extended envelope for HPC

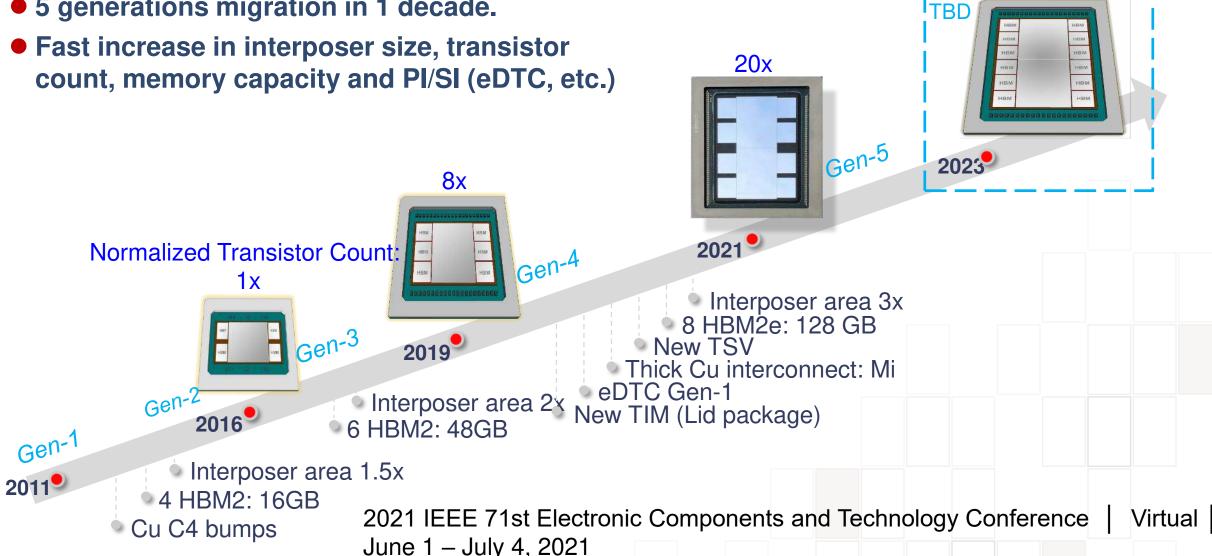

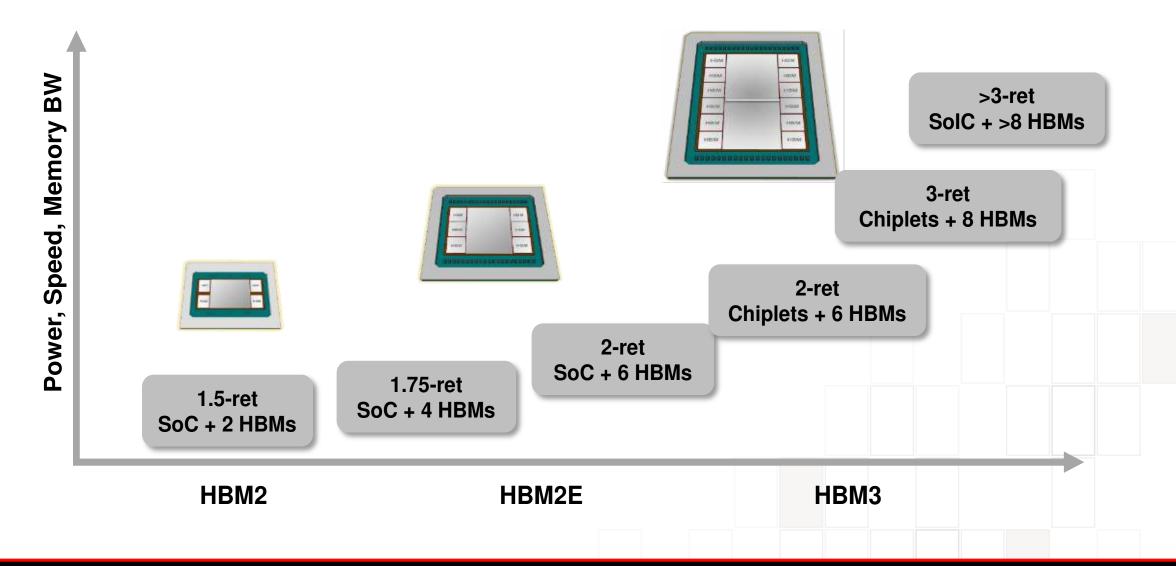

# **CoWoS<sup>®</sup>-S Rapid Progress**

- 5 generations migration in 1 decade.

- Fast increase in interposer size, transistor count, memory capacity and PI/SI (eDTC, etc.)

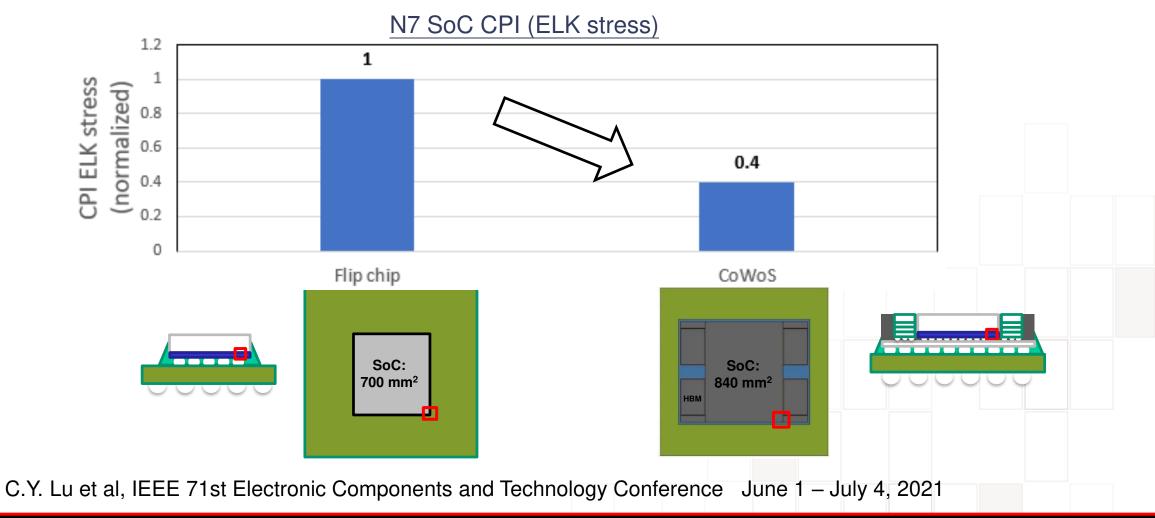

# **CoWoS®-S & Flip-chip CPI Comparison**

- Leverage Cu/LK technology for high density interconnect

- Si interposer, a stress buffer between SoC and substrate, for reduced CPI

# Leading CoWoS<sup>®</sup> Solutions for HPC

Qualify 3-reticle Si interposer with thicker metal (5Mi), eDTC\* and HBM2E in 2021 to further push for HPC.

# **Chiplets Integration Reduces System Cost/function**

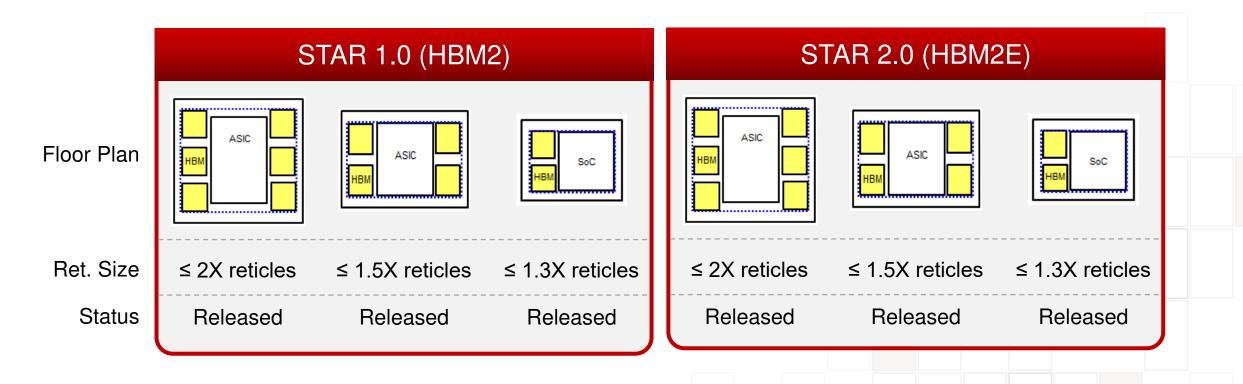

#### **CoWoS<sup>®</sup>-S STAR (STandard ARchitecture)**

- Shorten design cycle time and faster time to market

- 100% success rate for STAR adopters in 2020.

- More flexible design options in 2021. Adoption rate to grow 4x in 2021

# **CoWoS<sup>®</sup>-L For Heterogeneous Integration**

- Leverage InFO and CoWoS to integrate Si bridge, passives and RDL to best optimize CT, yield learning, system performance and EoS, etc.

- TSV in LSI (Local Si Interconnect), active & passive chip integration optional for better performance, power integrity, and design flexibility

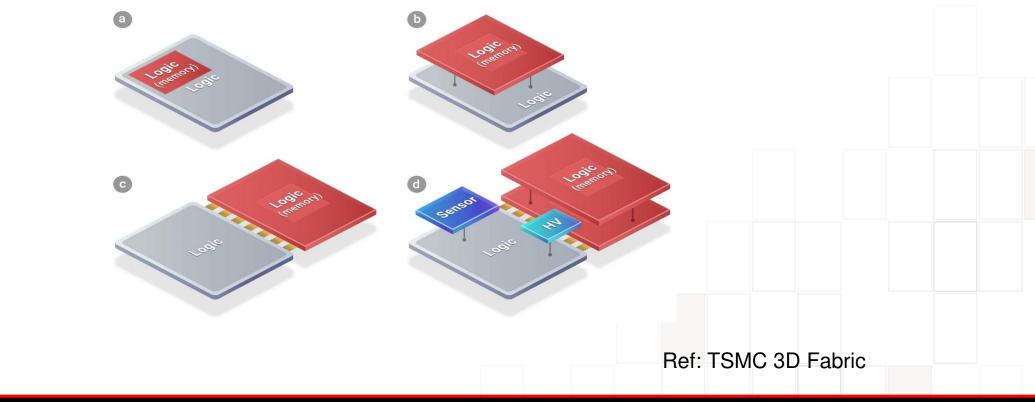

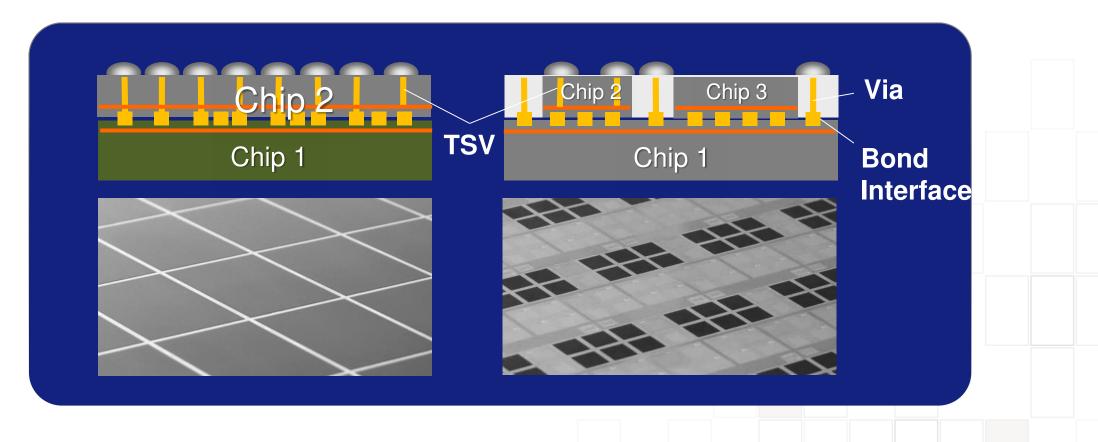

# **3D Chip Stacking- SolC<sup>™</sup>**

- CoW development: N7-on-N7 CoW and N5-on-N5, KGDs

- WoW Development: Logic-on-DTC (Deep Trench Capacitor).

Demonstrated power droop reduction

#### **SolC Development Direction**

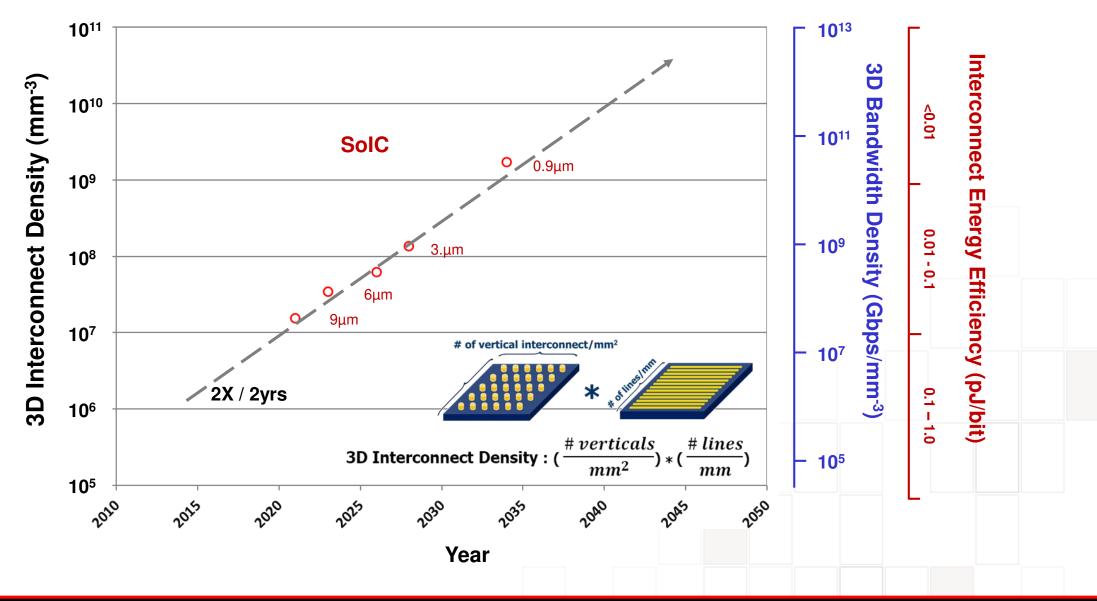

# Inter-chip Interconnect Scaling Roadmap

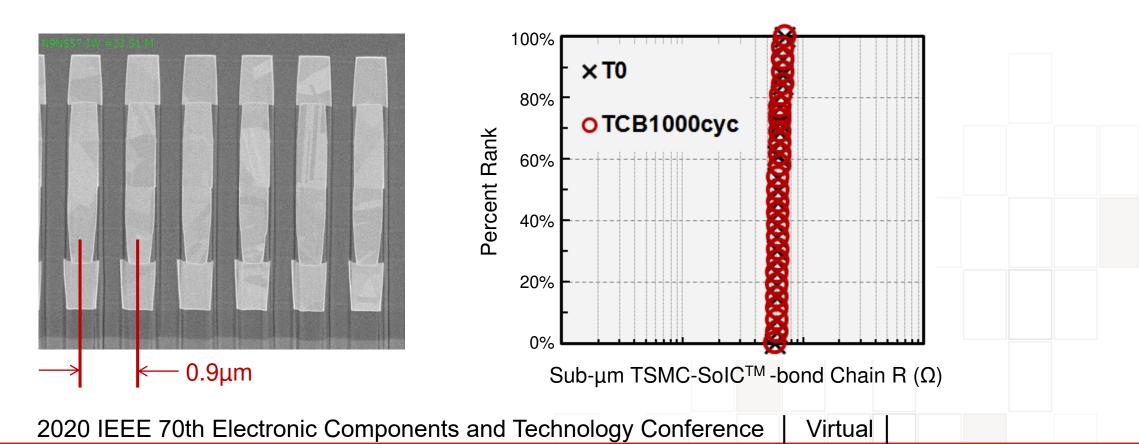

## Sub-µm CoW Interconnect Feasibility

- 0.9µm bond pitch stacking

- Highly reliable after TCB 1000 cycle

- Enable direct integration of SoIC/bonding and SoC/BEOL interconnect

Unleash Innovation

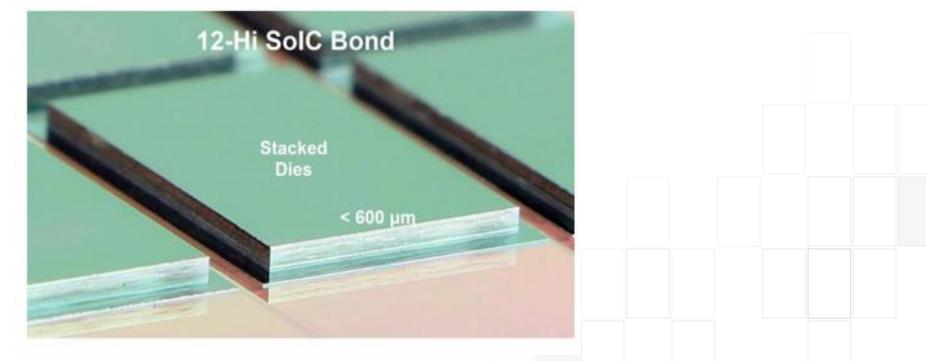

#### SolC "Envelop Growth"

- Bigger SoIC can be achieved with either more/larger units (2D) or more layers (3D) to integrate more memory capacity and/or higher functions.

- Thermal wall need to be addressed to remove heat accumulated in 3D stacking.

Ref: IEEE Trans on Electron Devices, vol. 67, no. 12, 2020

Unleash Innovation

#### **Outline**

#### Introduction

- Industry Transition

- •TSMC Packaging Technologies

- 3DFabric<sup>TM</sup>- SolC<sup>TM</sup>, InFO and CoWoS<sup>®</sup>

- System scale-up and Interconnect scale-down

- New Heterogeneous Integrations

- Advanced Thermal Solutions

- Si Photonics Integration (COUPE)

## Summary

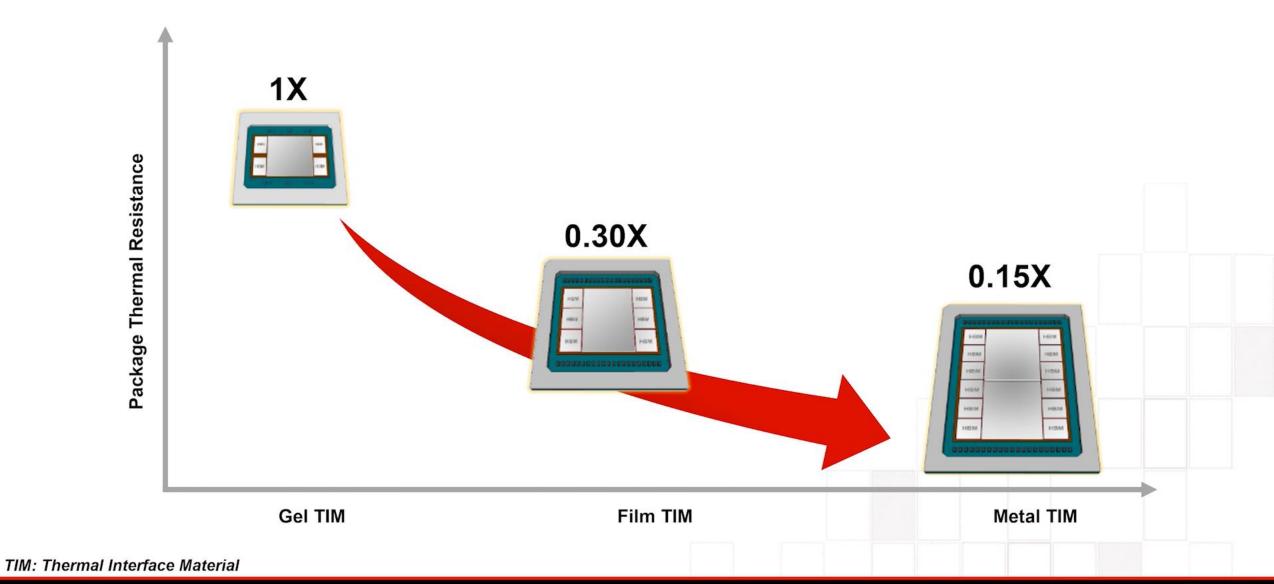

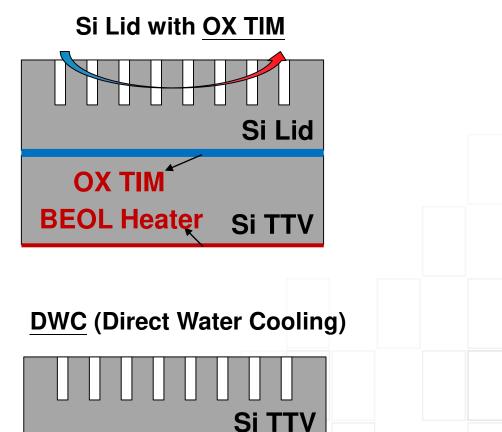

## **Thermal Solution Enhancement**

#### Slide 35 Integrated Si Micro-Cooler (ISMC) for Ultra-HPC

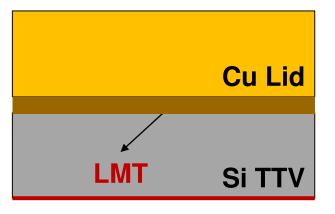

- Thin SiOx bonding interface (OX TIM) by fusion bonding Si lid and Si chips

- Low interface TR, even though  $K_{SiOx}$  at low single digit W/m·K

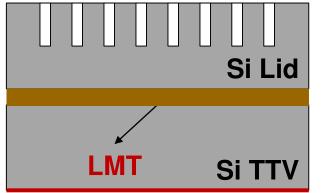

Cu Lid with <u>LMT</u> (Liquid Metal TIM)

Si Lid with LMT (Liquid Metal TIM)

# **Cooling Performance Benchmark**

#### **ISMC Summary**

- Leverage 3DFabric to develop new Ox TIM to replace LMT, achieved TR~2 K·mm<sup>2</sup>/W, 50% reduction from LMT.

- Demonstrated fusion bond Si lid (OX TIM) provides <u>kW level</u> heat dissipation solution for large chip size (>500mm<sup>2</sup>).

- Further improvement on the thermal performance obtained from DWC scheme. Mechanical strength of the new structures and their reliability will be studied.

# Unleash Innovation

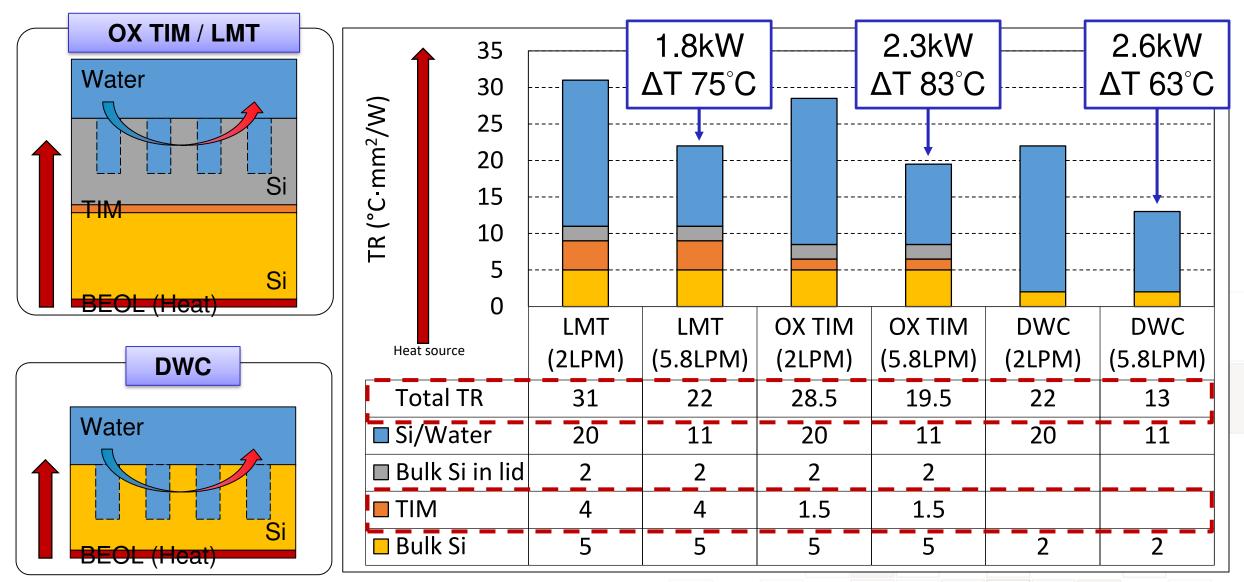

# The Need for SiPh

- The explosive growth of internet traffic has driven data centers to turn to Silicon photonics (SiPh) for its high speed and low power consumption.

- Compact Universal Photonic Engine is proposed to address the need for wide range applications on performance/power and volume/cost.

# Unleash Innovation

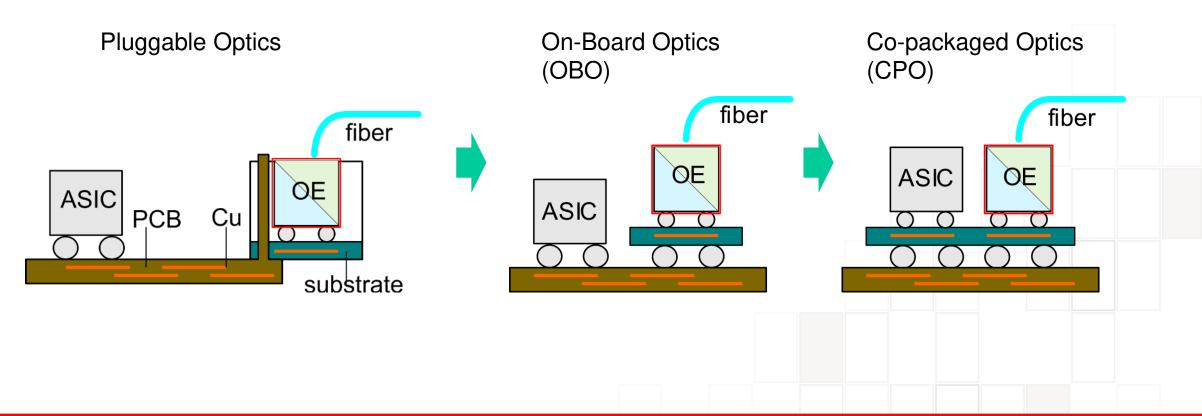

# **Evolution of SiPh Package**

- Evolution of the SiPh package: from Pluggable Optics, On-Board Optics (OBO), to Co-Packaged Optics (CPO).

- Drive to closer proximity between key components for bandwidth, power efficiency and even cost (eg. super-large size substrate)

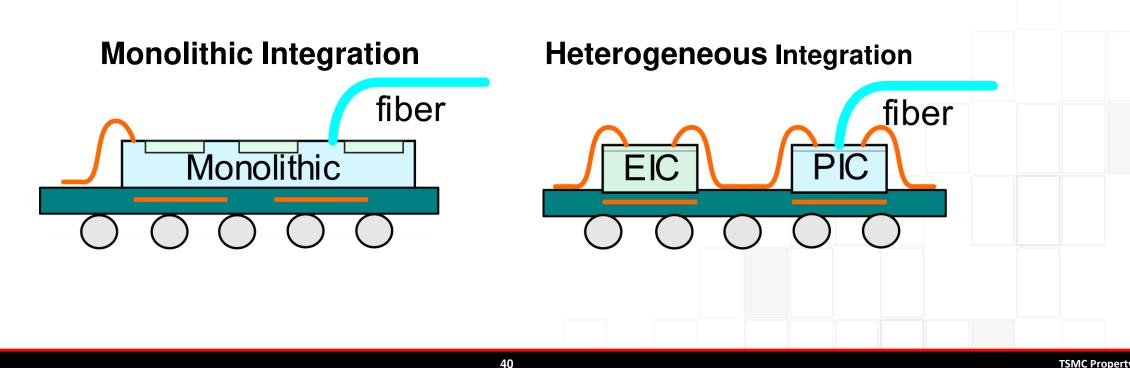

## **Photonic Engine Integration Schemes**

- High data rate and power efficiency could be achieved by monolithic integration.

- Technology node disparity between EIC and PIC is the main economic challenge for monolithic integration.

- COUPE, being a heterogeneous integration technology, is designed to minimize electrical coupling loss.

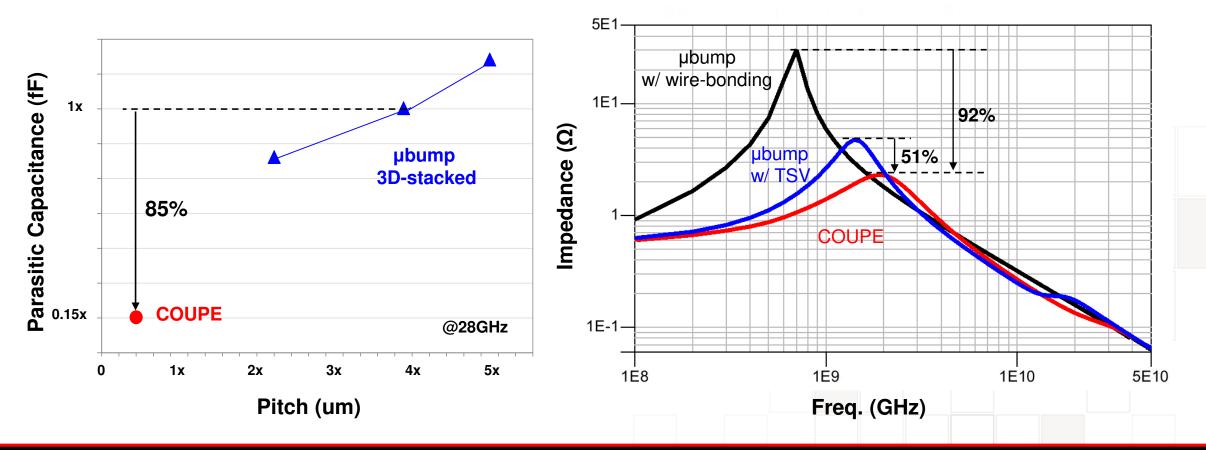

# Electrical Interface (1/2)- Parasitics and PDN Impedance

- COUPE has low parasitics at EIC-PIC Electrical Interface, 85% lower capacitance compared with uBump

- 51% reduction in PDN impedance comparing with uBump w/ TSV; and 92% reduction of uBump w/ wire-bonding.

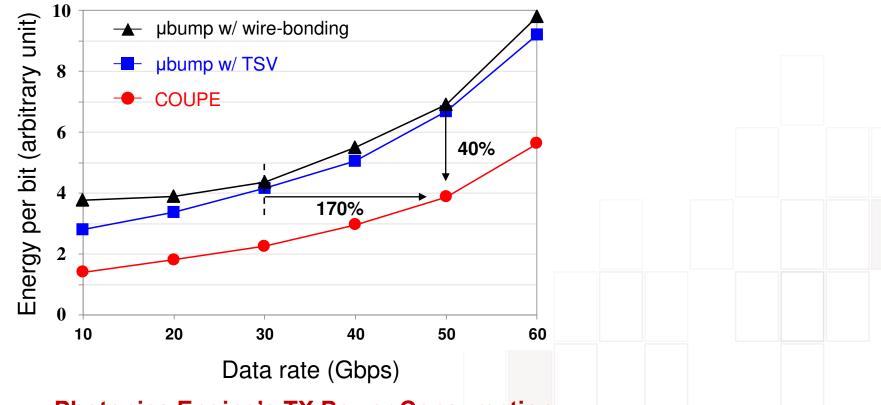

### **Electrical Interface (2/2)- Power Consumption**

- Power Consumption Comparison with uBump-based PE:

- COUPE has 40% lower power consumption at the same speed.

- COUPE can reach 170% speed gain with the same power.

#### Photonics Engine's TX Power Consumption

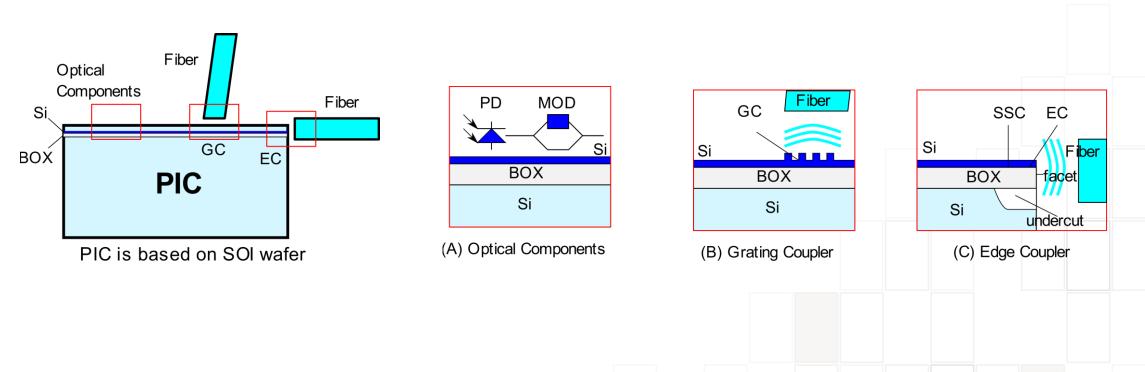

# **Optical Interface (1/2): Overview**

Light can be coupled either vertically (GC) or horizontally (EC):

- GC, as a surface coupler, requires cleanliness and integrity of the optical path from grating surface all the way to the fiber core.

- For EC, care must be taken to prevent the expanded optical mode from overlapping with the bulk silicon underneath SSC.

# Unleash Innovation

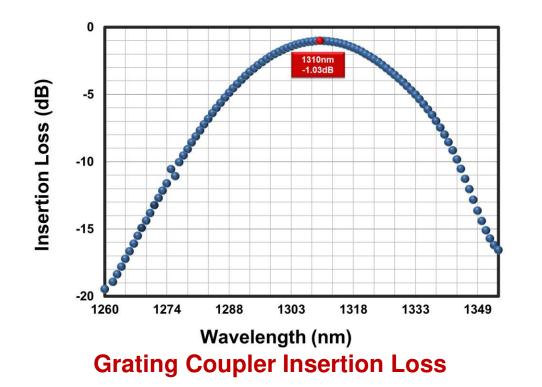

# **Optical Interface (2/2): GC and EC with COUPE**

- GC is designed with optical path intrinsically sealed with dielectrics all the way to the fiber attachment unit, achieving IL (1D apodized GC) -1.03dB @1310nm for TE

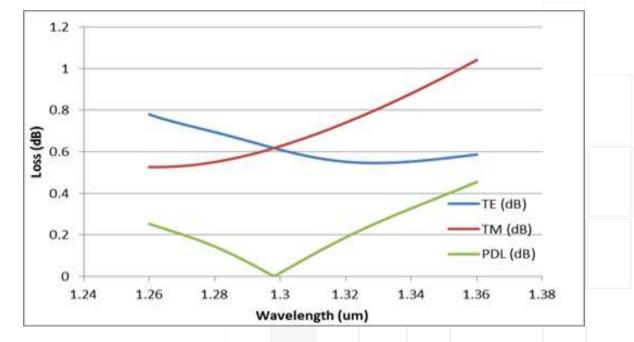

- EC avoids optical loss due to beam overlapped with underneath Si, achieving IL -0.6dB @1310nm for TE&TM modes

- With COUPE, GC and EC can built with essentially the same structure.

#### **Edge Coupler Insertion Loss**

#### **Summary**

- TSMC 3DFabric<sup>™</sup> technology platform continues packaging envelop scale-up, and 3D stacking interconnect density scale-down to drive energy efficient performance.

- Leverage 3DFabric to integrate innovative SiPh components (COUPE) to further enhance system performance and function

- Thermal wall could also be addressed for more 3D stacking by new micro-cooling systems- ISMC and DWC.

#### **Acknowledgement**

The author want to express sincere appreciations to TSMC colleagues in R&D, BD, operation and QR, etc. for their strong support. Collaborations efforts from supply chain partners are also acknowledged.

Unleash Innovation

#### **Thanks for Your Attention.**

© 2021 TSMC, Ltd