## A High-Speed and Low-Offset Dynamic Latch Comparator

Microelectronics RF IC design View project

Hindawi Publishing Corporation The Scientific World Journal Volume 2014, Article ID 258068, 8 pages http://dx.doi.org/10.1155/2014/258068

### Research Article

## A High-Speed and Low-Offset Dynamic Latch Comparator

# Labonnah Farzana Rahman, Mamun Bin Ibne Reaz, Chia Chieu Yin, Mohammad Marufuzzaman, and Mohammad Anisur Rahman

<sup>1</sup> Department of Electrical, Electronic and Systems Engineering, Universiti Kebangsaan Malaysia, 43600 Bangi, Selangor, Malaysia

Correspondence should be addressed to Labonnah Farzana Rahman; labonnah.deep@gmail.com

Received 15 March 2014; Revised 27 May 2014; Accepted 10 June 2014; Published 9 July 2014

Academic Editor: Ramesh Pokharel

Copyright © 2014 Labonnah Farzana Rahman et al. This is an open access article distributed under the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

Circuit intricacy, speed, low-offset voltage, and resolution are essential factors for high-speed applications like analog-to-digital converters (ADCs). The comparator circuit with preamplifier increases the power dissipation, as it requires higher amount of currents than the latch circuitry. In this research, a novel topology of dynamic latch comparator is illustrated, which is able to provide high speed, low offset, and high resolution. Moreover, the circuit is able to reduce the power dissipation as the topology is based on latch circuitry. The cross-coupled circuit mechanism with the regenerative latch is employed for enhancing the dynamic latch comparator performance. In addition, input-tracking phase is used to reduce the offset voltage. The Monte-Carlo simulation results for the designed comparator in 0.18  $\mu$ m CMOS process show that the equivalent input-referred offset voltage is 720  $\mu$ V with 3.44 mV standard deviation. The simulated result shows that the designed comparator has 8-bit resolution and dissipates 158.5  $\mu$ W of power under 1.8 V supply while operating with a clock frequency of 50 MHz. In addition, the proposed dynamic latch comparator has a layout size of 148.80  $\mu$ m × 59.70  $\mu$ m.

#### 1. Introduction

Analog-to-digital converters (ADC) have become a significant element driving the semiconductor industry over the past few years. Increased integration of different functional blocks within a single chip makes ADCs more conventional and they are able to provide high speed with low power dissipation. In addition, some features of ADCs like small size processes, low power indulgences, and a reduced propagation delay make them more acceptable to the semiconductor industry. However, it is not straightforward to scale down transistor dimensions, as it requires high channel doping, gate-induced drain leakage, and band to band tunneling across the junction. The difficulty of short channel effects also needs to be controlled [1]. Moreover, analog circuit design happens to be more complex to carry out the necessity of reliability, where supply voltages need to be decreased according to the small dimensions of the transistors [2]. All these concerns apply to the most usable representative of the ADCs: the comparator.

The comparator is the key building block in the design process for ADCs. The comparators measure the smallest voltage differences in ADC's inputs, resolving the performance and the precision of any ADCs. An application that requires digital information recovery from analog signals, such as I/O receivers and radio frequency identification (RFID) memory circuits, widely uses high performance comparators to intensify a little input voltage to a big voltage level [3, 4]. Moreover, digital logic circuits can detect these signals within a short period. Therefore, a faster and precision-making comparator requires high gain and high bandwidth [5, 6].

Several structures of high-speed comparators exist, such as the multistage open loop comparator, the preamplifier latch comparator, and the regenerative latch comparator. Among the different structures, high resolution and high speed can be obtained easily by using the multistage open loop comparator. On the other hand, the latch-type comparator is the most usable one in the abovementioned applications

<sup>&</sup>lt;sup>2</sup> Mimos Berhad, 57000 Kuala Lumpur, Malaysia

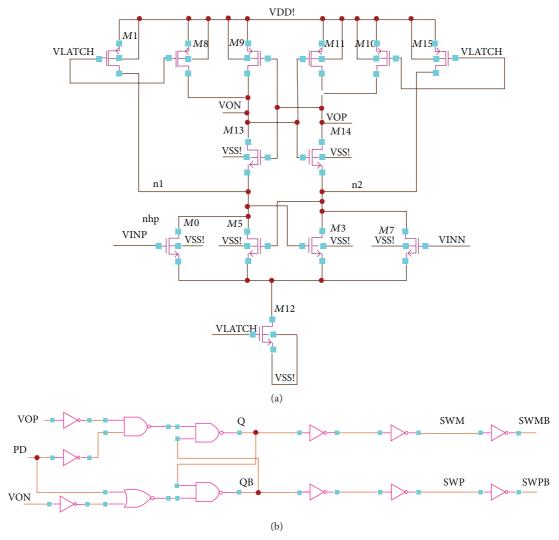

FIGURE 1: (a) Schematic diagram of the proposed differential pair dynamic latch comparator and (b) schematic diagram of the R-S flip-flop with digital signal PD.

due to its high-speed and low power consumption features. Latch-type comparators are able to accomplish decisions more rapidly with no static power indulgence and strong positive feedback [13]. Moreover, latch-type comparators are able to generate high gain in regeneration mode due to their positive feedback features. However, to design circuits for low voltage operations capable of decreasing the dynamic range of the inputs and the corresponding differential process [2, 14], the power dissipations in rail-to-rail operations are often increased. Consequently, the most vital limitations of the dynamic latch comparator are the kickback noises generated by high transmission currents [15]. In addition, employing a transmission gate can also induce spikes at the differential input voltage signals, which affects the performance of the dynamic latch comparator due to random noise, input offset voltages, and component mismatch.

In 2013, Zhu et al. designed an ultra-high-speed latched comparator with a controlled amount of positive feedback cell [16]. However, in this design, transmission gate switches are employed to reduce the power dissipation and the effect of

charge injection. In other research work, Kapadia and Gandhi implemented a dynamic latch comparator using the CMOS charge-sharing concept, which also employed an extra buffer stage [17]. To obtain better performances, the uniqueness of the comparator, such as offset, input common mode range, propagation delay, and power dissipation, has been analyzed in both 130 nm and 90 nm technologies. Nevertheless, employing a buffer stage increases the power dissipation and the chip size. Singh and Gupta proposed a wideband flipped voltage follower (FVF) circuit using an inductive-peaking based bandwidth, which is able to engender low output impedance at high frequency [18]. On the other hand, this FVF design consumes more power. In 2013, Bhumireddy et al. introduced a novel latch-based comparator for successive approximation ADC with sub-32 nm double gate MOSFETs (DG-MOSFET) [19]. In this design, the regeneration time of the latch is enhanced by employing an extra positive feedback, which in turn increases the offset voltage and the propagation delay.

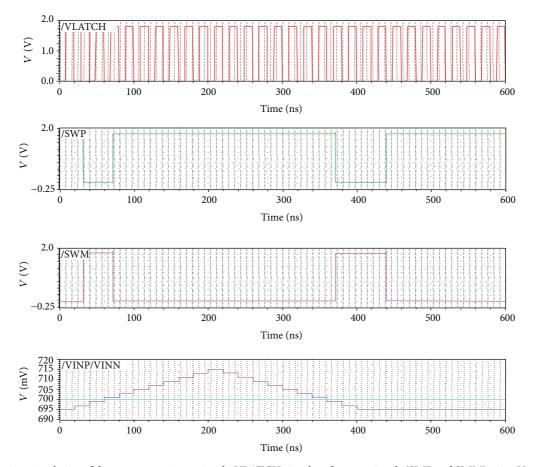

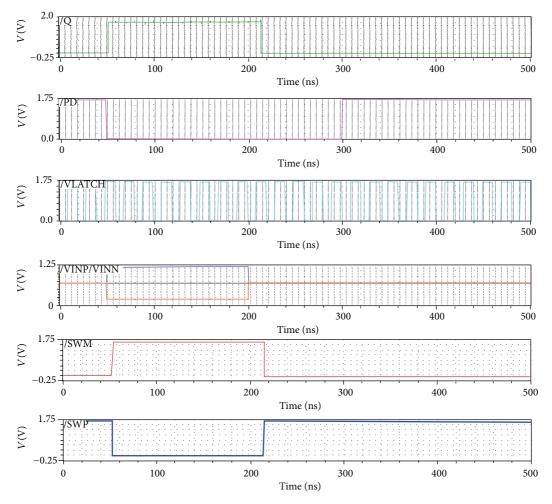

FIGURE 2: Transient simulation of the comparator input signals, VLATCH signal, and output signals (SWP and SWM) using Virtuoso Spectre.

An amplifier is employed before the latched comparator, which decreases the offset voltages caused by the device mismatch. To achieve high gain to the output signal of the amplifier, a transmission gate can be utilized between the preamplifier and the latch, which in turn controls the signal path by using the insertion trend. Conventionally, a latch proceeded by preamplifier stages is utilized to employ a faster and accurate comparator [6, 20]. As a result, more area and power are dissipated by employing the preamplifier stages that also border the frequency bandwidth of the input signal. Miyahara et al. proposed a dynamic comparator with a selfcalibration feature based on output averaging [21]. Moreover, in this design, a charge pump is required to regulate the corresponding input-referred offset voltage, making the approach inefficient. However, the involvement of this charge pump circuit limits its accuracy. In 2007, Verma and Chandrakasan proposed a novel structure for an offset compensated latch comparator. Nevertheless, convoluted timing necessities and a high number of offset annulment capacitors limit using this comparator in high-speed applications [22].

In this paper, a dynamic latch comparator is proposed based on differential pair input stages and one cross-coupled stage. Moreover, the proposed comparator is able to provide more high resolution and high speed with low power dissipation than conventional dynamic comparators at low supply voltage. The design is implemented in a Cadence Virtuoso

$0.18~\mu m$  CMOS process. The prelayout and postlayout simulation results prove that the circuit topology makes it applicable to work at very low supply voltage applications.

## 2. Design of Proposed Dynamic Latch Comparator

All the transistors should be properly matched in layout and biased in the saturation region to make a dynamic latch comparator more vigorous against mismatch and process variations. A fully differential dynamic latch comparator based on cross-coupled differential pairs is shown in Figure 6, which is based on the design of "Lewis-Gray" dynamic comparator [23].

In Figure 1, transistors *M*0, *M*3, *M*5, and *M*7 are utilized as the input circuitry. The overall latch circuitry consists of transistors *M*1, *M*8, *M*9, *M*10, *M*11, *M*12, *M*13, *M*14, and *M*15. In this proposed topology, the latch circuit is connected directly to the source coupled pairs *M*3 and *M*5 and the supply voltages *M*1, *M*8, *M*9, *M*10, *M*11, and *M*15, which makes the current sources switchable. To reset the S-R latch at the output of the comparator, a digital signal power down (PD) is used. When the comparator is off, VLATCH = low, the current source transistor *M*12 is switched off, and no current path exists from the supply voltage. The PMOS transistors

FIGURE 3: Propagation delay waveform between the VLATCH and SWP signal.

M1, M8, M10, and M15 reset the outputs VON and VOP and nodes n1 and n2 to VDD. On the other hand, when VLATCH = high, the outputs are disconnected from the positive supply and switching current source M12 begins to conduct. M12 mainly determines the bias current of the input transistors M0, M7, M3, and M5. The cross-coupled NMOS pair M3 and M5 is utilized in the proposed topology to produce positive feedback that allows the output to switch faster. The switching mainly depends on the inputs VINP and VINN. In addition, the output signals SWM and SWP are unchanged (combine with the above). When the voltage VINP is bigger than VINM, the drain voltage of M0 will fall at a faster rate than the drain voltage of M7. Once the positive feedback from the cross-coupled NMOS transistors M5 and M3 kicks in, the node n1 will drop even faster and pull node VON low creating a logic low at the RS latch and the output Q = low. The overall circuit performance is depending on the devices size and dimensions which are shown in Table 1.

In this research, no offset cancelling techniques are introduced. However, there is a tradeoff between high speed and high accuracy (e.g., 8 bits) because of MOS device mismatches [24]. Effects of offset voltage can be reduced but cannot be circumvent completely. The total offset voltage of the comparator has the well-known dependency on the mismatch of the threshold voltage  $\Delta V_T$ , load resistance  $\Delta R_L$ ,

TABLE 1: Transistor dimensions used in this proposed topology.

| Transistors | $W (\mu m)$ | $L(\mu m)$ | m factor |  |

|-------------|-------------|------------|----------|--|

| M0          | 4           | 4          | 12       |  |

| M1          | 2           | 0.18       | 1        |  |

| M3          | 4           | 2          | 1        |  |

| M5          | 4           | 2          | 1        |  |

| <i>M</i> 7  | 4           | 4          | 12       |  |

| M8          | 2           | 0.18       | 1        |  |

| M9          | 4           | 2          | 1        |  |

| M10         | 2           | 0.18       | 1        |  |

| M11         | 4           | 2          | 1        |  |

| M12         | 6           | 1          | 2        |  |

| M13         | 2           | 1          | 1        |  |

| M14         | 2           | 1          | 1        |  |

| M15         | 2           | 0.18       | 1        |  |

and transistor dimensions  $\Delta\beta$  and the corresponding average values  $(V_T, R_L, \text{ and } \beta)$ :

$$V_{os} = \Delta V_T + \frac{V_{gs} - V_T}{2} \left( \frac{\Delta R_L}{R_L} + \frac{\Delta \beta}{\beta} \right). \tag{1}$$

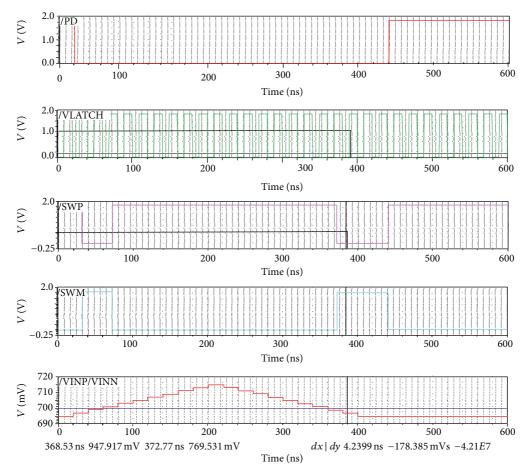

FIGURE 4: Corner analysis of the comparator input signals, VLATCH signal, and output signals (SWP and SWM).

In (1), the offset voltage is dominated by the  $\Delta\beta$ , which is the mismatch of the transistor dimension, the overdrive voltage  $V_{gs}-V_T$ . Moreover, the threshold voltage  $V_T$  also has an effect in (1). If the common mode voltage becomes lower ( $V_{gs}$ , low), the offset is found to be smaller. The effect of the mismatches of the transistors from simulations M1, M8, M9, M10, M11, M13, M14, and M15 in this topology is not very critical. Moreover, the transistors in the input differential pair and the cross-coupled NMOS are significant, as these M0, M3, M5, M7, and M12 transistors determine the overdrive of the input differential pair, which is related proportionally to the  $V_{gs}-V_T$  in (1).

#### 3. Results and Comparison

The proposed dynamic latch comparator circuit has been verified using the SPECTRE simulator (CADENCE). The CADENCE Virtuoso in a 0.18  $\mu$ m CMOS process parameter is utilized in this design. The simulated behavior of the comparator is illustrated in Figure 2. It is observed from Figure 2 that with a 2 mV positive step size for the input VINP and keeping VINN fixed at 0.7 V, the proposed dynamic latch comparator can switch successfully. In this topology,

the stepping of the input signal VINP (going up and coming back down) is used to check whether there is any hysteresis or not [25]. From the simulated results of Figure 2, it is found that when VINP > VINN (VINP = 695 mV and VINN = 700 mV) on the rising edge of the VLATCH signal, the proposed dynamic latch comparator can switch successfully. Similarly, switching also happens whenever VINP < VINN during VLATCH = high. In this case, the input signals VINP and VINN values are chosen in such a way to find out the output variation for small input changes.

Figure 3 shows the propagation delay between the latch and the output signals. When input signal VINN > VINP and the VLATCH is high, output signal SWM is in the rising state and output signal SWP is in the falling state. The simulated result shows that during the rising edge of the SWP maximum propagation delay between the VLATCH and SWP signal is about 4.2 nS.

To verify the robustness of the proposed dynamic latch comparator, different increments of environmental conditions like temperature, voltage clock frequency, and so forth need to be tested. To test the process variation, all 45 corners, 3 Vcc (1.7, 1.8, and 1.9), 3 temperatures (27, 0, and 90), and 5 corners (typical, snsp, snwp, wnsp, and wnwp) are analyzed

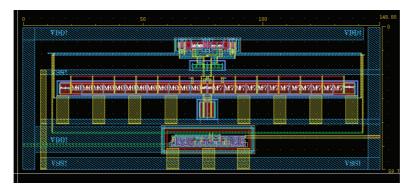

FIGURE 5: A layout design of the proposed dynamic latch comparator.

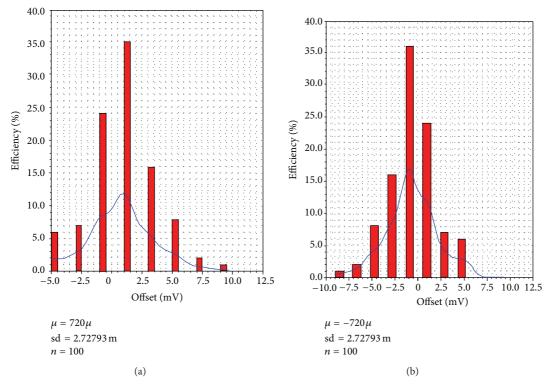

FIGURE 6: Postlayout Monte-Carlo simulation result with process and mismatch variation.

for the proposed design. In addition, different stepping sizes of VINP and a fixed VINN at 0.7 V are analyzed. Figure 4 shows that at different variations of Vcc and temperature the proposed dynamic latch comparator has been switching properly. Whenever VNP > VINN and VLATCH is high, SWM and SWP switch properly. Similarly, switching also happens whenever VINP < VINN during VLATCH = high.

The chip layout is shown in Figure 5, where the chip occupies an area of 148.80  $\mu$ m  $\times$  59.70  $\mu$ m. In this layout, all the transistors are placed symmetrically to reduce mismatch in the parasitic capacitance.

The postlayout Monte-Carlo simulation results for 100 runs are shown in Figure 6, which found that a higher offset value was obtained at a sampling frequency of  $50\,\mathrm{MHz}$  using VDD 1.8 V with the overdrive voltage of 3.44 mV, which corresponds to 0.5 LSB at 8-bit precision.

Table 2 summarizes the proposed latch comparator performance with recently published research works. Compared to the research works of [7, 8], the proposed dynamic latch comparator has less offset voltage. The comparator of [7, 10] works only in 20 MHz sampling rate, whereas this design is able to run in 50 MHz sampling rate. Moreover, propagation delay is significantly lower than the research works published in [8, 10]. Apart from the research work of [12], this design has more resolution (8 bits instead of 7 bits).

To compare the performance of different comparators, a well-known figure of merit (FOM) is used [26]. Therefore, in this research, to measure the performance of the design, the FOM is calculated using the following equation:

$$FOM = \frac{P_d}{2^n * f_c},\tag{2}$$

The Scientific World Journal

| References              | [7]  | [8]              | [9]  | [10]            | [11] | [12] | This work |

|-------------------------|------|------------------|------|-----------------|------|------|-----------|

| Year                    | 2009 | 2010             | 2010 | 2011            | 2012 | 2013 |           |

| Technology (μm-CMOS)    | 0.35 | 0.5              | 0.18 | 0.18            | 0.9  | 0.65 | 0.18      |

| Supply voltage (V)      | 1.2  | ±1.5             | 1.8  | 1               | 1    | 1    | 1.8       |

| Power $P_d$ ( $\mu$ W)  | 8.4  | _                | 225  | 63.5            | 240  | 157  | 158.5     |

| Sampling rate (MHz)     | 20   | _                | 30   | 20              | 50   | 50   | 50        |

| Resolution (bits)       | 8    | _                | 8    | 12              | 6    | 7    | 8         |

| Propagations delay (nS) | _    | 932 <sup>a</sup> | _    | 26 <sup>a</sup> | _    | _    | 4.2       |

| Offset voltage (mV)     | 3    | 24.2             | _    | 0.0476          | _    | _    | 3.44      |

| FOM (fj/conv)           | 1.64 | _                | 29.2 | 0.77            | 150  | 28   | 0.7       |

TABLE 2: Comparison study of the proposed latch comparator performance.

where  $P_d$  is the power dissipation, n is the number of bits (resolution), and  $f_s$  is the sampling frequency of the comparator. From the comparison study of different recently published works as shown in Table 2, the proposed dynamic latch comparator has the lowest FOM energy dissipated per conversion among all the recently published research works.

In this research, the proposed dynamic latch comparator is able to work for 8-bit resolution, whereas the resolution of [10] is found to be 12 bits. To improve the overall resolution of the proposed dynamic latch comparator reduced offset voltage, different transistor sizing for reducing mismatch and layout methods in the realized chip can be implemented. In this research,  $V_T$  mismatches is reduced by using big transistors like M0, M3, M5, and M7. Mismatch among the devices can be found from the following equation:

$$\sigma_{\Delta VT} = \frac{A_{VT}}{\sqrt{WL}}. (3)$$

As a result, overdrive voltage has been increased and  $V_{gs} - V_T$  is decreased. Therefore, to improve the resolution of the proposed design, tail current of M12 can be reduced. However, the proposed design has removed the preamplifier stage and employed a dynamic latch, resulting in significant power saving, especially in flash and pipelined A/D architectures and RFID transponders.

#### 4. Conclusion

A novel high-speed, low power, and low-offset dynamic latch-type comparator method is presented in this research work. The proposed design does not use any preamplifier stages before the latch stage, which reduces the power dissipation and the area dramatically. The corner analysis and the Monte-Carlo simulation results clearly reveal that the dynamic latch comparator is able to switch properly with different input stepping sizes. Though the proposed design has 8-bit resolution with 50 MHz sampling rate it consumes much lower power. Moreover, the comparison study shows that the novel design is able to operate at a higher clock frequency of 50 MHz with offset voltage 3.44 mV and propagation delay 4.2 nS in 1.8 V supply voltage, which is better than recently published research works.

#### **Conflict of Interests**

The authors declare that there is no conflict of interests regarding the publication of this paper.

#### Acknowledgments

The authors would like to express sincere gratitude to the MIMOS Berhad and Universiti Kebangsaan Malaysia for the collaborative research Grant eScienceFund and the research university Grant DLP-2013-016 and UKM-AP-ICT-20-2010.

#### References

- [1] A. Allan, "International Technology Roadmap for Semiconductors (ITRS)," Semiconductor Industry Association (SIA), 2008, http://public.itrs.net/.

- [2] C. J. B. Fayomi, G. W. Roberts, and M. Sawan, "Low power/low voltage high speed CMOS differential track and latch comparator with rail-to-rail input," in *Proceedings of the IEEE Internaitonal Symposium on Circuits and Systems*, vol. 5, pp. 653–656, Geneva, Switzerland, May 2000.

- [3] L. F. Rahman, M. B. I. Reaz, M. A. M. Ali, M. R. Marufuzzaman, and M. R. Alam, "Beyond the WIFI: introducing RFID system using IPV6," in Proceedings of the 3rd ITU-T Kaleidoscope Academic Conference: Beyond the Internet? Innovations for Future Networks and Services, pp. 209–212, Pune, India, December 2010

- [4] J. Jalil, M. B. I. Reaz, M. A. S. Bhuiyan, L. F. Rahman, and T. G. Chang, "Designing a ring-VCO for RFID transponders in 0.18  $\mu$ m CMOS process," *The Scientific World Journal*, vol. 2014, Article ID 580385, 6 pages, 2014.

- [5] M. Marufuzzaman, M. Reaz, L. F. Rahman, and T. G. Chang, "High speed current dq PI controller for vector controlled PMSM drive," *The Scientific World Journal*, vol. 2014, Article ID 709635, 9 pages, 2014.

- [6] B. Razavi and B. A. Wooley, "Design techniques for high-speed, high-resolution comparators," *IEEE Journal of Solid-State Circuits*, vol. 27, no. 12, pp. 1916–1926, 1992.

- [7] H. Lee, "A low-voltage low-power comparator with current-controlled dynamically-biased preamplifiers for DCM buck regulators," in *Proceedings of the 16th IEEE International Conference on Electronics, Circuits and Systems (ICECS '09)*, pp. 371–374, Yasmine Hammamet, December 2009.

<sup>&</sup>lt;sup>a</sup>Measured value.

- [8] P. M. Furth, Y. Tsen, V. B. Kulkarni, and T. K. Poriyani House Raju, "On the design of low-power CMOS comparators with programmable hysteresis," in *Proceedings of the 53rd IEEE International Midwest Symposium on Circuits and Systems* (MWSCAS '10), pp. 1077–1080, Seattle, Wash, USA, August 2010.

- [9] P. Otfinowski, "A 2.5MS/s 225 μW 8-bit charge redistribution SAR ADC for multichannel applications," in *Proceedings of the* 17th International Conference on Mixed Design of Integrated Circuits and Systems (MIXDES '10), pp. 182–185, Warsaw, Poland, June 2010.

- [10] H. J. Achigui, C. Fayomi, D. Massicotte, and M. Boukadoum, "Low-voltage, high-speed CMOS analog latched voltage comparator using the flipped voltage follower as input stage," *Microelectronics Journal*, vol. 42, no. 5, pp. 785–789, 2011.

- [11] P. Nuzzo, C. Nani, C. Armiento, A. Sangiovanni-Vincentelli, J. Craninckx, and G. van der Plas, "A 6-Bit 50-MS/s threshold configuring SAR ADC in 90-nm digital CMOS," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 59, no. 1, pp. 80–92, 2012.

- [12] Y. Xu and T. Ytterdal, "A 7-bit 50MS/s single-ended asynchronous SAR ADC in 65nm CMOS," in *Proceedings of the IEEE International Conference NORCHIP*, pp. 1–4, Vilnius, Lithunia, November 2013.

- [13] H. J. Veendrick, "The behavior of flip-flops used as synchronizers and prediction of their failure rate," *IEEE Journal of Solid-State Circuits*, vol. 15, no. 2, pp. 169–176, 1980.

- [14] H. Hong and G. Lee, "A 65-fJ/conversion-step 0.9-V 200-kS/s rail-to-rail 8-bit successive approximation ADC," *IEEE Journal* of Solid-State Circuits, vol. 42, no. 10, pp. 2161–2168, 2007.

- [15] R. Wang, K. Li, J. Zhang, and B. Nie, "A high-speed high-resolution latch comparator for pipeline Analog-to-Digital Converters," in *Proceedings of the IEEE International Workshop on Anti-counterfeiting, Security, Identification (ASID '07)*, pp. 28–31, Fujian, Xiamen, China, April 2007.

- [16] Z. Zhu, G. Yu, H. Wu, Y. Zhang, and Y. Yang, "A high-speed latched comparator with low offset voltage and low dissipation," *Analog Integrated Circuits and Signal Processing*, vol. 74, no. 2, pp. 467–471, 2013.

- [17] D. N. Kapadia and P. P. Gandhi, "Implementation of CMOS charge sharing dynamic latch comparator in 130 nm and 90 nm technologies," in *Proceedings of the IEEE Conference on Information and Communication Technologies (ICT '13)*, pp. 16–20, JeJu Island, Republic of Korea, April 2013.

- [18] U. Singh and M. Gupta, "High frequency flipped voltage follower with improved performance and its application," *Microelectronics Journal*, vol. 44, no. 12, pp. 1175–1192, 2013.

- [19] V. Bhumireddy, K. Shaik, A. Amara et al., "Design of low power and high speed comparator with sub-32-nm double gatemosfet," in *Proceedings of the IEEE International Conference* on in Circuits and Systems, pp. 1–4, Kuala Lumpur, Malaysia, September 2013.

- [20] K. Dabbagh-Sadeghipour, K. Hadidi, and A. Khoei, "A new architecture for area and power efficient, high conversion rate successive approximation ADCs," in *Proceedings of the 2nd Annual IEEE Northeast Workshop on Circuits and Systems* (NEWCAS '04), pp. 253–256, June 2004.

- [21] M. Miyahara, Y. Asada, D. Paik, and A. Matsuzawa, "A low-noise self-calibrating dynamic comparator for high-speed ADCs," in Proceedings of the IEEE Asian Solid-State Circuits Conference (A-SSCC '08), pp. 269–272, Fukuoka, Japan, November 2008.

- [22] N. Verma and A. P. Chandrakasan, "An ultra low energy 12-bit rate-resolution scalable SAR ADC for wireless sensor nodes,"

- IEEE Journal of Solid-State Circuits, vol. 42, no. 6, pp. 1196–1205, 2007.

- [23] T. B. Cho and P. R. Gray, "10-bit, 20-MS/s, 35-mW pipeline A/D converter," in *Proceedings of the IEEE Custom Integrated Circuits Conference*, pp. 499–502, San Diego, Calif, USA, May 1994.

- [24] G. M. Yin, F. O. Eynde, and W. Sansen, "A high-speed CMOS comparator with 8-b resolution," *IEEE Journal of Solid-State Circuits*, vol. 27, no. 2, pp. 208–211, 1992.

- [25] A. Graupner, A Methodology for the Offset Simulation of Comparators, vol. 1, 2006.

- [26] M. van Elzakker, E. van Tuijl, P. Geraedts, D. Schinkel, E. Klumperink, and B. Nauta, "A 1.9 μw 4.4 fJ/conversion-step 10 b 1 MS/S charge-redistribution ADC," in *Proceedings of the IEEE International Solid State Circuits Conference (ISSCC '08)*, pp. 237–610, San Francisco, Calif, USA, February 2008.